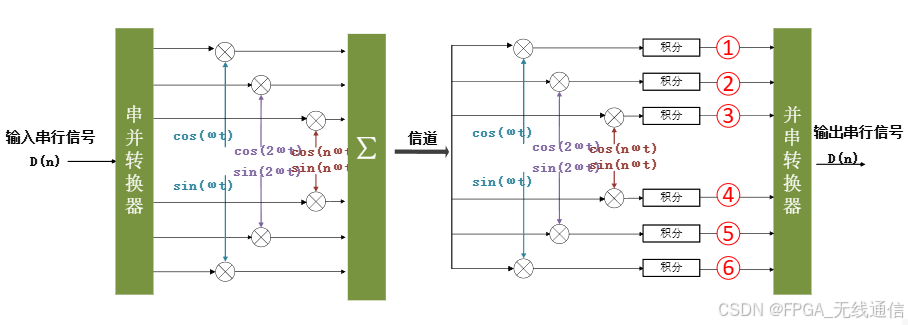

OFDM(Orthogonal Frequency Division Multiplexing)是一种多载波调制技术,其核心思想是:

(1)将高速数据流分割为多个低速数据流

(2)在多个正交的子载波上并行传输

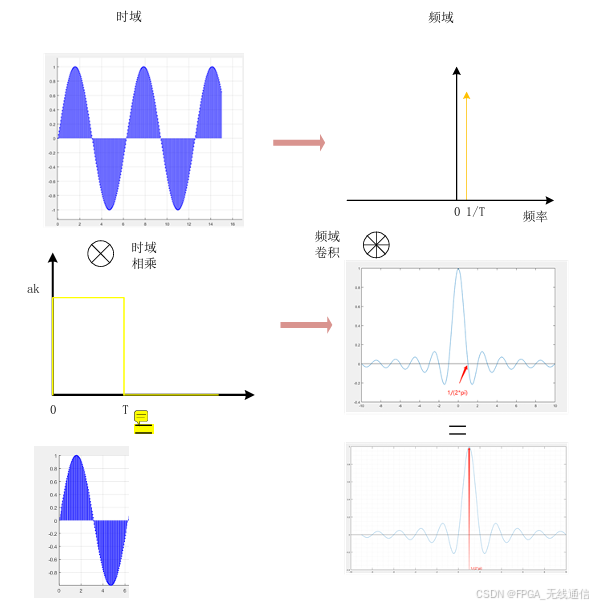

(3)利用子载波间的正交性避免载波间干扰(ICI)

OFDM 是多载波调制系统,可以在多个正交的载波上进行调制发射,(正交里可以理解为正交载波互相不进行干扰类似于 IQ 调制中I和Q正交同频但是不会互相干扰),通过扩展多个子载波(子通道)实现大带宽数据传输。

OFDM相对比单载波系统的优点有,在相同的带宽的物理信道中能OFDM能够容 纳更多的子载波通道,而单载波系统要考虑到邻道干扰和频谱混叠等问题需要占 用更多的单通道的带宽。

正交:载波间互相不进行干扰;

正交信号:两函数的互相关值为0,可以看成两个互相独立的函数。

一个OFDM符号周期内:因为要进行IFFT转换,要对符号周期内频谱情况转换为时域信号,然后进行通道发射;

正交的原因:除了与自身混频的积分不为0,其余子载波之间正交积分为0;

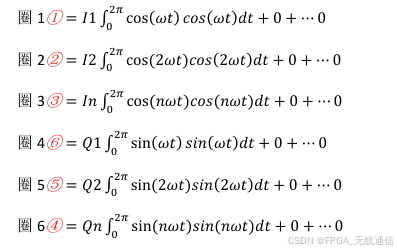

在时域进行子载波调制会增加对信号的处理复杂度,需要将其转换到频域;

单独子载波进行时域转频域的过程:时域乘积等于频域卷积;

时域矩形函数与一个载波信号进行相乘,把数据信息调制到载波上,那么对应时 域相乘,

频域中进行卷积得到频谱搬移之后的频谱 。

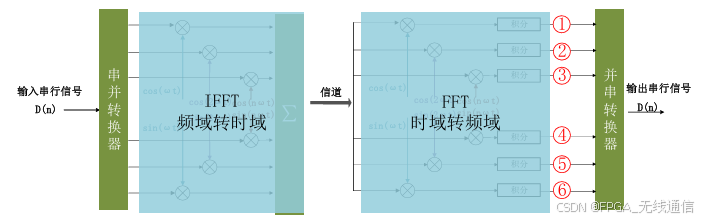

在一个OFDM符号周期内,通过得到每个子载波的幅度和相位,送入FFT做反变换IFFT,就能得到时域信号,接收机通过FFT进行时域转频域,就得到每个信号频域信息a+bj,幅度,

相位,频率,再进行解调得到并行数据再进行并转串从而恢复数据;

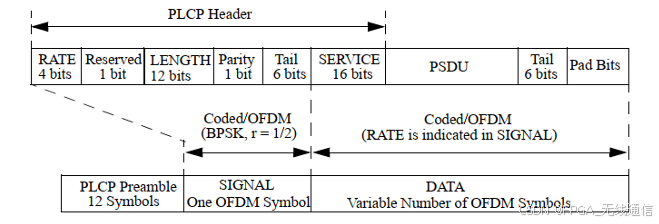

PPDU 帧结构是 802.11a 协议中所规定的物理层协议数据单元,也就是基带发射处 理器所要生成的数据结构。

Preamble:

为12个符号周期的前导码,其中前 面包括十个重复的的符号为短训练序列,主要用于进行信号检测、自动增益控制 (AGC),符号定时和粗频率偏差估计。后边的两个符号为长训练序列,长训练序 列用于精确的频率偏差估计和信道估计。

signal:

中包括有后续数据的调制 类型、编码速率和数据长度等信息。

DATA:

Data域包括service 域、psdu、尾比特、和pad比特。

Service 域有16 bits 其中前七个置零,用来初始化接收机部分的解扰码器 的初始值,因为前7bit为0时加扰器会输出加扰器的初试状态,接收端解扰器 因为初始值为0,那么经过7bit 移位后就把解扰器初试状态设置为和发送端的 加扰器相同了以此实现加扰和解扰初试状态同步。后9个bits预留以便将来使 用。

Psdu(sub-layer service data unites)叫作物理层服务数据单元,是 mac 层和 phy 层之间所需传输的数据,其比特长度为实际通信中传输比特数据(报文)的 比特长度。

Psdu 后面跟随的尾bits 的作用和signal 域的尾比特作用相同,都是为了 卷积编码器的移位寄存器的清零。

Pad bits 的意义在于使整个 data 域的比特流长度刚好调整为每一个ofdm 符号数据比特长度的整数倍,如果data域的比特数不足ofdm符号的整数倍,要 适当补零。

以20mhz 信道进行计算,每一个ofdm的符号的周期统一定义为4us, 数据传输信道采用48个子信道进行数据的发送,当调制模式为64-qam时的理论 传输速度为:

3/4 * 48 * 6 * 1/4 = 54 mb/s

每个ofdm符号的编码比特(Ncbps)为:

6 * 48 = 288

每个ofdm符号的数据比特(Ndbps)为:

288 * 3/4 = 216

即说明在该条件下时,理论传输速度可以达到54mb/s,每个ofdm符号传递288 个比特数据,其中实际传输的有效数据为216个。

填充比特(pad)的计算:

Nsym = ceiling[(16 + 8 * length + 6)/Ndbps];

Ndata = Nsym * Ndbps;

Npad = Ndata -- (16 + 8 * length + 6);

其中Nsym为ofdm符号个数;

用数据域加上服务域和尾比特域的比特数量除以每一个ofdm符号 的数据比特长度,取其商再加1,即可得到该报文发送需要的ofdm符号数量。

调制流程:

输入比特流 → 编码与交织 → 星座映射(QAM/PSK) → 串并转换 → IFFT → 并串转换 → 添加循环前缀 → 数模转换 → 射频调制

解调流程:

接收信号 → 下变频 → 模数转换 → 去除循环前缀 → 串并转换 → FFT → 并串转换 → 信道均

衡 → 星座解映射 → 解码与解交织 → 输出比特流

发送端模块:

比特流 → FEC编码 → 交织 → 星座映射 → 导频插入 → 串并转换 → IFFT → 循环前缀添加 →

并串转换 → 数模转换 → 上变频

接收端模块:

下变频 → 模数转换 → 同步(时间/频率) → 去循环前缀 → 串并转换 → FFT → 信道估计与均

衡 → 导频提取 → 并串转换 → 星座解映射 → 解交织 → FEC解码 → 比特流