一 前言

这几年在工作中使用axi-quad-spi IP core的次数一只手恐怕数不过来了,从standard模式到quad模式,从RTL到MicrobBlaze再到Linux,不得不感叹Xilinx这些IP core设计得如此强大和实用,简直是360°实用无死角。

以前赶项目,本着能用就行的原则,很多东西是一带而过。现在再回头梳理一遍,看看能否依葫芦画瓢,自己也开发一个更加简易的通用quad spi模块。

本文就不做PG153的通篇翻译了,这样的blog在csdn上一抓一大把,我这里先从IP core的block着手进行梳理,时间不够多,只能断断续续进行更新了。

说了这么多,axi-quad-spi有啥用呢?

(1)这个IP core既可以做普通的spi接口驱动模块使用(standard模式),比如我们常做4线spi接口外设的FPGA驱动开发,有了这个IP,那我们只用关注AXI接口寄存器的读写操作,就可以快速完成spi接口外设的功能验证工作;而且AXI接口寄存器的读写操作流程是通用的,把寄存器打包好,一次调试通过,后续可以反复多次使用。

(2)再者,这个IP core还可以用于驱动SPI接口的Flash(Dual/Quad模式),搭配上Xilinx提供的STARTUPE3原语,同样只用关注AXI接口寄存器的读写操作,一次封装,多次受益。

二 axi-quad-spi Block

2.1 axi-quad-spi的Block结构

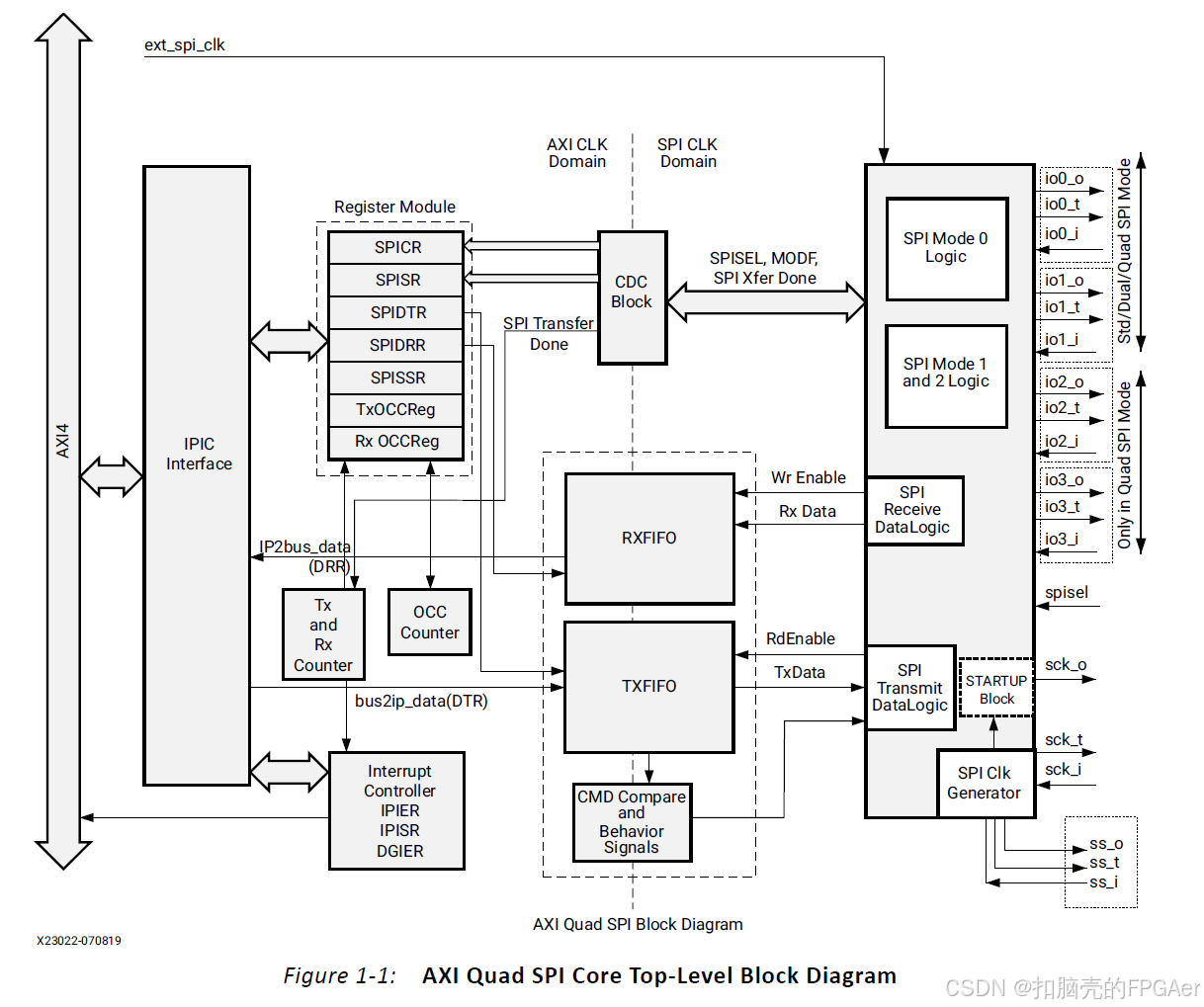

从时钟域的角度看,axi-quad-spi IP core分为两大部分:

(1)axi_clk时钟域部分

(2)ext_spi_clk时钟域部分

2.2 axi_clk时钟域部分

2.3 ext_spi_clk时钟域部分