本文以Xilinx 7系列FPGA为对象,描述FPGA时钟网络的基础、需求、构建,参考了Xilinx官方文档,仅供学习。

下面内容参考Xilinx UG472

时钟资源概述

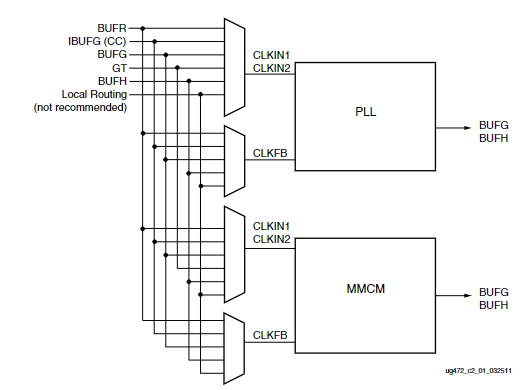

a)7系列FPGA的时钟资源可管理复杂与简单的时钟需求,具备专用的全局时钟资源、区域I/O资源、区域时钟资源。CMT可提供时钟频率合成、去抖、抖动滤波功能。设计时钟功能时,不推荐使用局部布线等非时钟资源。

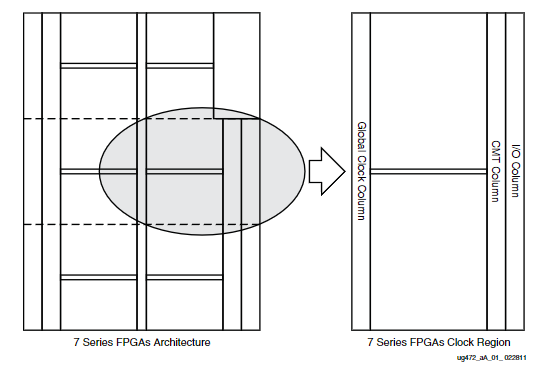

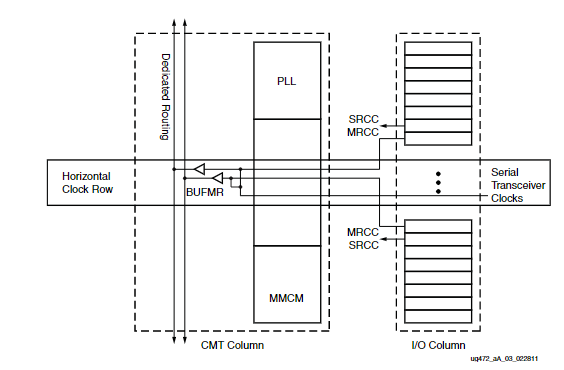

b)全局时钟树可实现对器件内所有同步单元的时钟驱动。IO时钟树和区域时钟树可驱动最多三个垂直相邻的时钟区域。每个CMT包含1个MMCM和1个PLL,且CMT均位于I/O列旁的CMT列中。

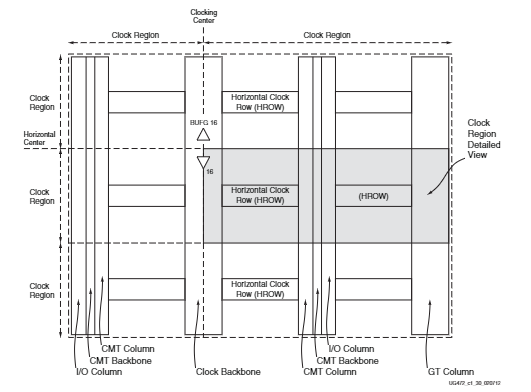

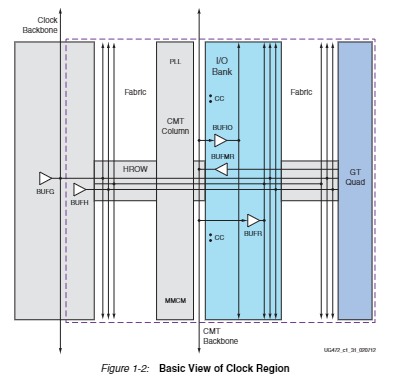

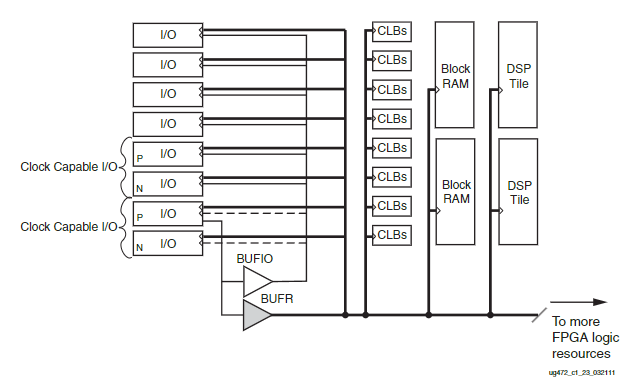

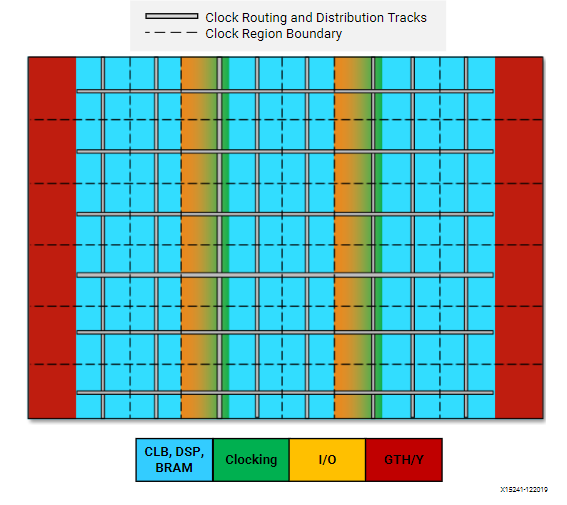

c)从时钟功能角度,7系列每个器件均划分为多个时钟区域,最小器件仅1个时钟区域,最大器件24个。一个时钟区域包含该区域内所有同步单元(如CLB、I/O、串行收发器、DSP、BRAM、CMT),横向跨越器件一侧,纵向覆盖50个CLB及1个I/O bank(50个I/O),且时钟区域中心有一条水平时钟行HROW。每个时钟区域从HROW向上、向下各延伸25个CLB。

d)路由资源

1)每个I/O bank均包含时钟输入引脚,可将用户时钟接入7系列FPGA的时钟路由资源。结合专用时钟缓冲器,这些时钟输入可将用户时钟接入以下线路:①器件同一上或下半部分的全局时钟线;②同一I/O bank及垂直相邻I/O bank内的I/O时钟线;③同一时钟区域及垂直相邻时钟区域内的区域时钟线;④同一时钟区域内的CMT,在有限情况下也可接入垂直相邻时钟区域内的CMT。

2)每个7系列器件拥有32条全局时钟线,可为全器件所有时序资源提供时钟及控制信号。全局时钟缓冲器驱动全局时钟线,且必须通过该缓冲器才能接入全局时钟线。每个时钟区域可通过其内部的12条水平时钟线,支持最多12条此类全局时钟线。

3)全局时钟缓冲器具备的功能:①作为时钟使能电路,启用或禁用跨多时钟区域的时钟;②无毛刺多路复用器实现两个时钟源的选择或从故障时钟源切换至其他源;③常由CMT驱动以实现消除时钟分布延迟和相对于另一个时钟的延迟调整。

4)水平时钟缓冲器BUFH/BUFHCE可通过水平时钟行接入单个时钟区域内的全局时钟线,也可作为时钟使能电路BUFHCE,独立启用或禁用覆盖单个时钟区域的时钟。每个时钟区域可通过其内部的12条水平时钟线,支持最多12条时钟。

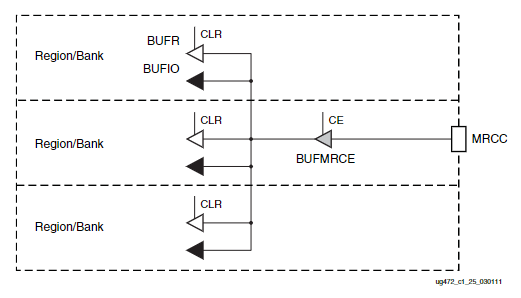

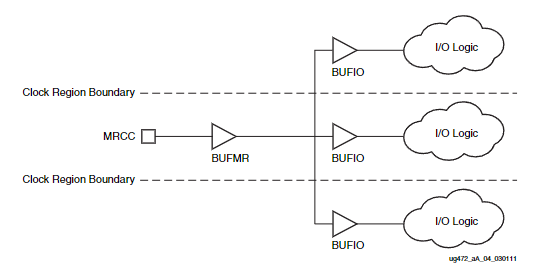

5)每个7系列FPGA均配备区域时钟树、I/O时钟树,可为单个时钟区域内所有时序资源提供时钟。同时配备多区域时钟缓冲器BUFMR,支持区域时钟、I/O时钟覆盖最多3个垂直相邻的时钟区域。具体特性如下:①BUFIO驱动IO时钟树,可为同一IO Bank内所有时序IO资源提供时钟;②BUFR驱动区域时钟树可为同一时钟区域内所有时钟负载提供时钟,且可通过编程对输入时钟进行分频;③结合IOB中的可编程串并转换器,BUFIO和BUFR时钟缓冲器可使源同步系统无需额外逻辑即可实现跨时钟域传输;④当与对应的BUFR或BUFIO配合使用时,多区域时钟缓冲器BUFMR可驱动相邻时钟区域及I/O bank内的区域时钟树和I/O时钟树;⑤单个时钟区域或I/O bank最多可支持4路独立I/O时钟和4路独立区域时钟。

6)高性能时钟路由可将CMT的特定输出直接连接至I/O,该路径抖动极低、占空比失真极小。

e)CMT概述

1)每个7系列FPGA最多包含24个CMT,每个CMT均由1个MMCM和1个PLL组成。MMCM和PLL可作为宽频率范围的频率合成器、外部或内部时钟的抖动滤波器,同时具备时钟去抖功能。其中PLL的功能是MMCM功能的子集。

2)7系列FPGA的时钟输入连接架构支持多种资源为MMCM和PLL提供参考时钟。7系列FPGA的MMCM具备双向无限精细相移能力(1/56 VCO周期步长),且可工作在动态相移模式(实时调整相位补偿板级延迟)。此外MMCM在反馈路径或某一路输出路径中集成了分数计数器,进一步提升了频率合成的精度。

f)时钟缓冲器

1)垂直时钟主干clock backbone将器件分为左右相邻区域,水平中线将器件分为上下两侧。上下分区会分隔两组BUFG,并对其连接方式部分限制。BUFG不隶属于任何时钟区域,可覆盖器件中所有时钟节点。所有水平时钟资源均位于时钟区域中心的HROW内,垂直非区域时钟资源则位于时钟主干、CMT主干中。

2)一个时钟区域的固定资源包括:每列50个CLB、每列10个36K BRAM(若某列中5个36K BRAM被PCIE集成单元替代则除外)、每列20个DSP、12个BUFH,若器件支持,时钟区域还会包含1个CMT、1个50引脚的I/O bank、1个含4个串行收发器的GT quad。

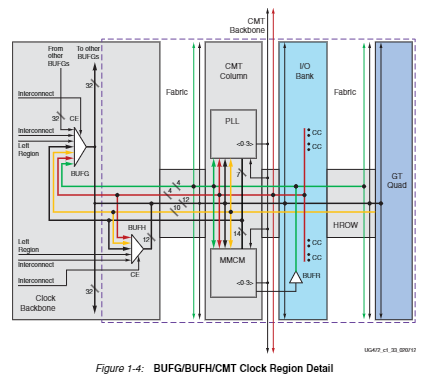

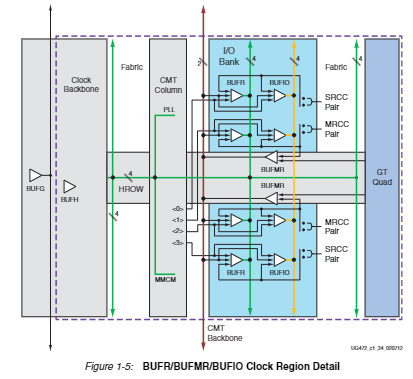

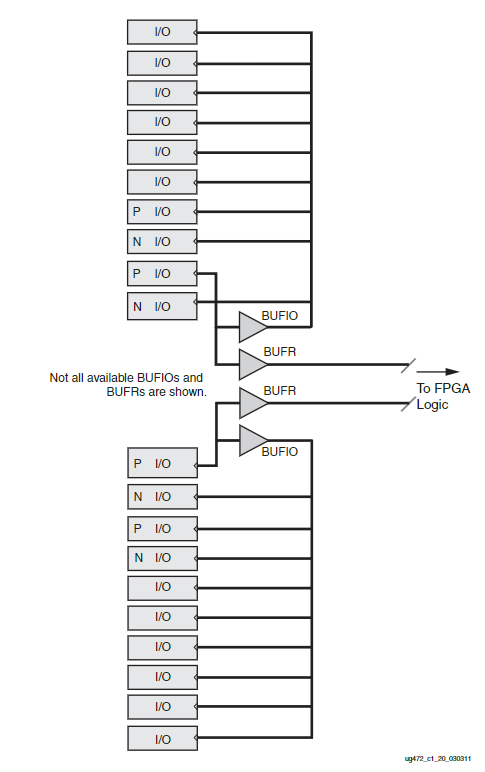

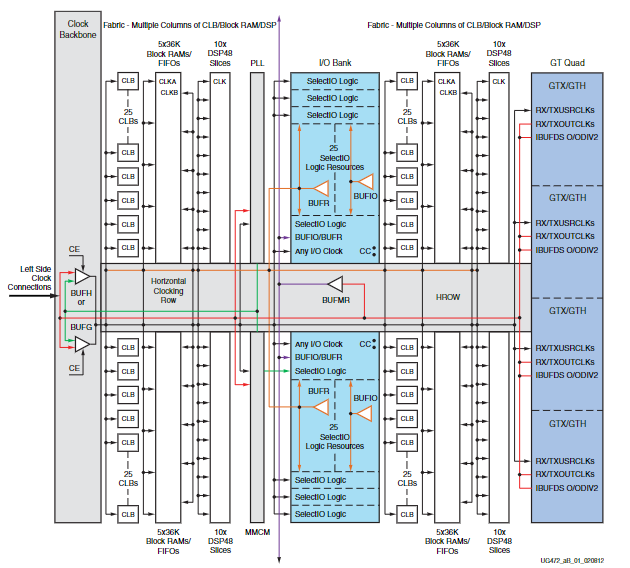

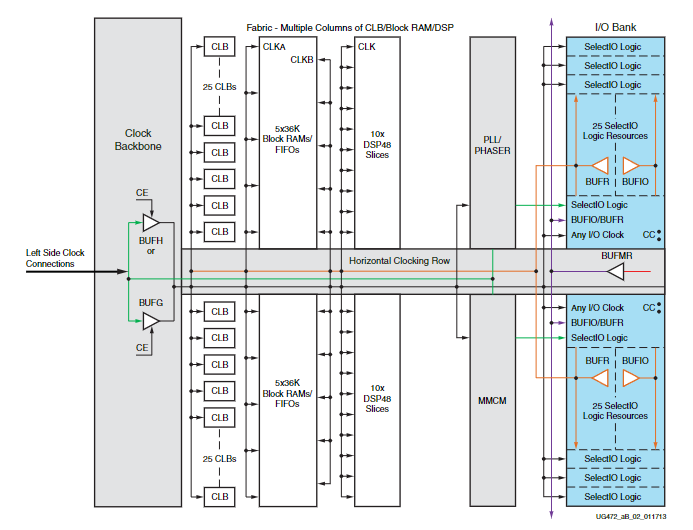

3)BUFG能够通过HROW驱动所有区域,不受其物理位置限制。BUFH则通过HROW专门驱动本区域的时钟节点,且与BUFG共享HROW中的路由资源。I/O bank内部包含两种缓冲器:BUFIO仅驱动I/O时钟资源,BUFR可同时驱动I/O资源和逻辑资源。多区域时钟缓冲器BUFMR支持BUFIO和BUFR的跨区域级联功能。外部时钟通过时钟输入引脚接入器件内部时钟资源。某些资源(如CMT)还能通过CMT主干连接相邻区域的资源。如下图示。

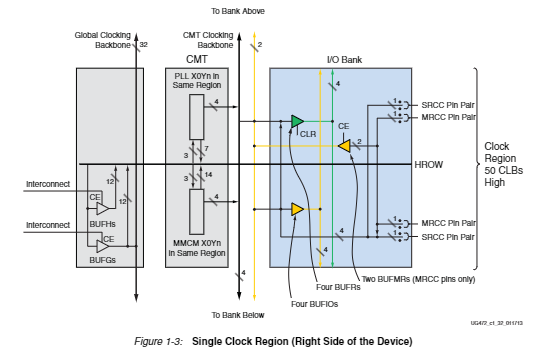

4)(注意!此处需要看字认图,不要光看字)每个I/O bank含4个BUFIO、4个BUFR、2个BUFMR(注意,BUFMR仅由MRCC引脚驱动)。时钟输入引脚(MRCC/SRCC引脚对,红色线表示)可驱动本区域CMT、BUFH、BUFIO、BUFR、BUFMR。CMT(细黑线表示)可通过CMT主干驱动相邻区域的CMT。BUFG、BUFH共享HROW的12条路由通道(粗黑线表示),可驱动本区域所有时钟节点,且BUFG可驱动BUFH以实现区域级独立时钟使能。千兆四通道收发器GT quad拥有10条专用通道(黄线表示),可驱动时钟主干中的CMT和时钟缓冲器。BUFR拥有4条通道(绿线表示),可驱动逻辑资源、CMT、BUFG中的时钟节点。在有限条件下CMT可通过CMT主干驱动相邻区域的其他CMT,同理时钟引脚也可在相同限制条件下驱动相邻区域的CMT。

5)某一区域的时钟源,既可驱动本区域的时钟缓冲器资源,也可驱动水平相邻区域的时钟缓冲器资源。CMT、时钟引脚、串行收发器,可通过BUFH将时钟驱动至水平相邻区域,同时也可连接至器件同一上/下半部分的BUFG。

6)时钟输入引脚对中,有2对称为多区域时钟输入引脚MRCC,支持多区域时钟方案。1对MRCC引脚可驱动1个特定的BUFMR,而BUFMR又可驱动本区域及相邻区域的BUFIO和BUFR,从而为多区域/多bank接口提供支持。同理,千兆收发器四通道GT quad也可驱动BUFMR。

7)MMCM的[3:0]路输出拥有一条通往BUFR和BUFIO的专用高性能差分路径,该特性也被称为高性能时钟HPC。

8)四个时钟输入引脚中的任意一个,均可驱动时CMT、BUFH。BUFG在图中显示为位于该区域内,但其物理位置可分布在时钟主干的其他位置。BUFG与BUFH共享HROW的12条路由通道,且两者均可驱动该区域内的所有时钟节点。BUFG还可驱动BUFH,这使得原本全局分布的时钟能实现区域级的独立时钟使能CE控制。GT quad拥有10条专用通道,可驱动时钟主干中的CMT和时钟缓冲器。位于I/O bank内的BUFR拥有4条通道,可驱动逻辑资源、CMT、BUFG中的时钟节点。在有限制条件下,CMT可通过CMT主干驱动相邻区域的其他CMT;同理,时钟引脚也可在相同限制条件下驱动相邻区域的CMT。时钟能力引脚可驱动器件同一上/下半部分任意位置的BUFG。CMT主干中设有4条通道,用于支持垂直相邻区域间的连接。

g)☆总结

1)BUF类缓冲器总结

①BUFG:全局时钟缓冲器,上下各16个,无时钟区域归属,低skew;

②BUFH/BUFHCE:水平区域缓冲器,覆盖单区域+水平相邻区域,BUFHCE支持独立时钟使能CE;

③BUFR:区域时钟缓冲器,覆盖单区域,支持1-8整数分频,驱动逻辑(CLB/BRAM/DSP)+IO;

④BUFIO:IO专用缓冲器,覆盖单个IO bank,仅驱动IO资源(ILOGIC/OLOGIC);

⑤BUFMR/BUFMRCE:多区域中继缓冲器,驱动3个垂直相邻区域的BUFIO/BUFR,BUFMRCE支持同步/异步CE。

2)路由资源总结

①HROW:区域内时钟分发通道,12条共享路由,供BUFG/BUFH使用;

②CMT主干:垂直跨区域时钟通道,有4条专用路由,支持CMT和时钟引脚输入跨垂直相邻区域;

③专用高速通道:高速时钟传输,GT quad10条直驱时钟主干CMT/缓冲器,MMCM HPC4条直驱BUFIO/BUFR。

3)区域内互联,就近驱动

①时钟引脚(MRCC/SRCC)→ 本区域CMT + BUFH + BUFR + BUFIO;

②BUFG(可位于时钟主干任意位置)→ 本区域所有时钟节点(通过HROW);

③BUFH → 本区域所有时钟节点(通过HROW),且可被BUFG驱动(实现全局时钟 + 区域CE控制);

④BUFR → 本区域逻辑 + CMT+BUFG(作为区域时钟中转站,分频后可升级为全局时钟)。

BUFG与BUFH共享HROW的12条路由,同一区域内两者总数≤12(避免路由冲突)。

4)垂直跨区域互联,有限度跨区域

①CMT/时钟输入引脚 → 通过CMT主干(4条路由)→ 垂直相邻区域的CMT;

②MRCC/GT quad → BUFMR → 本区域 + 上下相邻区域的BUFIO/BUFR(共3个区域)。

5)水平跨区域互联,局部覆盖

①CMT/时钟能力输入/GT → BUFH → 本区域 + 水平相邻区域;

②所有时钟源 → BUFG → 器件同侧(上下)任意区域。

6)高速专用互联

①MMCM 的CLKOUT[0:3] → 通过HPC通道 → 本区域BUFIO/BUFR(抖动 < 10ps,占空比失真 < 5%),适配DDR/高速串行接口;

②GT quad → 通过10条专用通道 → 时钟主干的CMT/缓冲器(避免普通路由干扰,保障高速收发器时钟质量)。

7)基础方案(应用场景+参考方案+原因)

①全器件同步逻辑(如处理器 / 多区域BRAM级联)→BUFG + MMCM/PLL→BUFG保障全局低skew,MMCM/PLL实现频率合成/去抖,消除全局时钟分发延迟;

②单区域 / 水平相邻区域局部逻辑(如单区域DSP运算)→BUFHCE + 本地CMT→BUFHCE降低全局资源占用,CE功能实现非工作时功耗优化,本地CMT减少跨区时序风险;

③源同步接口(如LVDS ADC/DDR)→BUFIO + BUFR + MMCM HPC→BUFIO驱动高速I/O采样时钟,BUFR分频驱动低速逻辑,HPC通道保障时钟低抖动;

④多垂直区域I/O接口(如3个bank的并行总线)→MRCC + BUFMR + BUFIO/BUFR→MRCC+BUFMR实现3个垂直区域同步,避免使用全局时钟导致资源浪费;

⑤高速串行收发器(如GT)→GT专用通道 + MMCM + BUFG/BUFH→GT专用通道避免干扰,MMCM优化时钟质量,BUFG/BUFH驱动GT的USERCLK。

h)☆时钟资源总结

1)MRCC是多区域时钟引脚。每I/O bank含2对差分引脚,是支持跨区域时钟驱动的核心输入引脚。驱动范围在同时钟区域+同左右侧时,可驱动4个BUFIO+4个BUFR+2个BUFMR+1个CMT+上下相邻的CMT(使用CMT时钟资源,相邻区域驱动有相位偏移风险)。驱动范围在同上下半区时,可驱动16个BUFG(仅驱动同侧的16个BUFG,上下半区的BUFG不互通)。驱动范围在同水平相邻时钟区域时,可驱动BUFH。

2)SRCC是单区域时钟引脚。每I/O bank含2对差分引脚,功能与MRCC类似,但仅支持单区域时钟驱动,无跨区域扩展能力。与MRCC的驱动目标几乎完全一致,唯一区别是不可驱动BUFMR(因SRCC无多区域扩展能力,BUFMR是多区域缓冲器)。其余目标是同区域的4个BUFIO/4个BUFR/1个CMT、上下相邻区域的CMT(需CMT骨干)、同上下半区的16个BUFG、同水平相邻区域的BUFH。

3)BUFIO每I/Obank含4个,仅驱动I/O逻辑的专用缓冲器,不支持fabric逻辑。核心作用是源同步接口的高速I/O时钟,如 ISERDES/OSERDES的CLK引脚,提供低抖动、低skew的I/O时钟。直接驱动源是同区域MRCC(1:1专用)、SRCC(1:1专用)、同区域MMCM的CLKOUT0~CLKOUT3(高性能时钟路径,低抖动)、MMCM的CLKFBOUT、同区域及上下相邻区域的BUFMR。直接驱动目标是ILOGIC.clk/ILOGIC.clkb(输入逻辑时钟)、OLOGIC.clk/ OLOGIC.clkb/OLOGIC.oclk/OLOGIC.oclkb(输出逻辑时钟)。

4)BUFR是区域时钟缓冲器,每时钟区域含4个,支持单区域全资源驱动(I/O+fabric逻辑),且具备1-8整数分频能力(BUFR_DIVIDE属性配置)。作为源同步接口的低速逻辑时钟(如ISERDES的CLKDIV引脚),实现时钟域交叉。直接驱动源是同区域MRCC(1:1专用)、SRCC(1:1专用)、同区域MMCM的CLKOUT0~CLKOUT3(高性能时钟路径,低抖动)、MMCM的CLKFBOUT、同区域及上下相邻区域的BUFMR、通用互联(不建议,时序不可预测,易引入抖动)。可以直接驱动同时钟区域的CMT和所有BUFG可驱动的目标,还可驱动同上下半区的16个BUFG。

5)BUFMR是多区域时钟缓冲器,每个时钟区域含2个,是跨区域扩展BUFIO/BUFR的核心缓冲器,仅驱动BUFIO/BUFR,不可直接驱动逻辑资源。其将MRCC/GT时钟扩展到3个相邻垂直区域(本区域+上下区域),支持多bank的源同步接口。其直接驱动源是同区域的MRCC+同区域的GT收发器时钟+通用互联。其直接驱动目标是仅限同区域及上下相邻区域的BUFIO+BUFR。

6)BUFG是全局时钟缓冲器,分上下半区各16个,是全局时钟覆盖的核心缓冲器,支持低skew、高扇出(覆盖全器件所有时钟节点)。其核心作用是跨多区域的全局时钟,支持时钟切换、时钟使能。直接驱动源有同上下半区的SRCC/MRCC、同上下半区的CMT(MMCM/PLL输出)、同区域的GT收发器时钟、BUFR、通用互联、同上下半区相邻的BUFG。其直接驱动目标是全器件的CMT(反馈时钟或级联时钟)、同上下半区的GT收发器时钟、同上下半区的相邻BUFG、全器件的fabric资源+IO资源、CLB控制信号、同区域的BUFH。

7)BUFH是水平时钟缓冲器,每时钟区域含12个,支持2个水平相邻区域驱动,是局部全局时钟的替代方案,功耗低于BUFG。其作为局部逻辑(如单区域/两个水平区域的CLB集群)的时钟,支持时钟使能(BUFHCE版本,节能)。

时钟路由资源

a)要充分利用时钟路由资源,必须了解如何将用户时钟从PCB传输到FPGA,确定哪种时钟路由资源最优,然后通过使用合适的I/O和时钟缓冲器来访问这些时钟路由资源。

b)时钟缓冲器选择考量

1)BUFG:最常用的时钟路由资源,可连接器件内所有时钟节点。以下场景优先使用BUFG:①设计或设计的部分模块需跨器件大范围覆盖,且功能无法局部化;②需级联跨多时钟区域的硬件块(如BRAM、DSP、集成IP),或需连接非邻近的CLB;③需同步(无毛刺)或异步切换时钟(如切换至备用时钟、降频节能);④需通过时钟使能在非工作时段节能(注:CE不宜用于模拟时钟单元的真CE逻辑功能,因存在时序延迟限制),或在器件启动后同步初始化时钟单元。

2)BUFR/BUFIO:核心用途是源同步接口。当接口位于单个时钟区域时,BUFIO驱动SelectIO的高速侧,BUFR以较低频率驱动FPGA逻辑侧的解串/串化电路,实现时钟域转换。若接口需跨多个时钟区域,需配合多区域缓冲器BUFMR/BUFMRCE将时钟域转换功能扩展至上下相邻区域。此外,部分无需源同步I/O的场景(如简单时钟分频)也可使用BUFR,但需重点关注时序与偏差(非其核心用途)。

3)BUFH/BUFHCE:属严格的区域资源,无法跨上下时钟区域,且无时钟分频功能,仅在水平方向覆盖两个相邻区域,类似局部全局时钟。BUFH支持向MMCM/PLL提供反馈,且其时钟插入延迟可补偿,以下场景优先使用:

①接口或逻辑可局部化至单个时钟区域或两个水平相邻区域;

②需通过时钟使能(BUFHCE版本)在逻辑/接口非活跃时降低动态功耗(支持周期级门控时钟);

③需连接CLB的非时钟资源(如使能/复位信号),且要求低偏差特性;

④需同步启动单个时钟区域内的时钟单元。

c)时钟引脚

1)外部用户时钟须通过差分时钟引脚对(时钟输入引脚CC)接入FPGA,CC保障时钟时序,不可用通用I/O+局部路由传时钟。每个IO bank有4对CC引脚,支持差分/单端时钟,支持任意I/O标准。

2)每个bank含2对SRCC和2对MRCC。SRCC覆盖单区域 + 全局时钟树,驱动同区域/垂直相邻区域CMT及对应缓冲器;MRCC功能同SRCC,额外支持驱动BUFMR跨3个区域。

3)时钟输入引脚可连接同一时钟区域的CMT,也可跨区域连接至上下相邻区域的CMT,但存在部分使用限制:

①单时钟驱动单个CMT:若需用单个时钟驱动一个CMT,时钟输入与目标CMT必须处于同一时钟区域,确保时钟路径的时序可靠性;

②单时钟驱动多个CMT:在时钟输入所在的时钟区域内配置一个MMCM/PLL,作为时钟分发的起点。额外的CMT优先部署在相邻区域,若需驱动同一列中更远距离的CMT,虽技术可行但需评估时序影响。若驱动源与目标CMT不在同一区域,且驱动源所在区域无MMCM/PLL,必须设置属性CLOCK_DEDICATED_ROUTE = BACKBONE,但需注意此时输出与输入时钟的相位无法精准对齐。驱动同一列CMT的专用路由资源有限,若被Xilinx IP占用导致不可用,可将CLOCK_DEDICATED_ROUTE设为FALSE,通过局部互连逻辑实现驱动,但会引入不可补偿的额外延迟。若多个CMT使用的资源完全一致,无需设置CLOCK_DEDICATED_ROUTE约束即可实现自动布局,若需混合部署MMCM和PLL,应优先将其整合至同一个CMT内。

d)时钟引脚布局规则:连通性规则+资源可用性规则。

①时钟输入目标:全器件IO或时序元件。资源使用与布局规则:时钟引脚→BUFG→全局时钟树,其中时钟输入引脚需与目标BUFG归属同一器件的上下半区;器件上下半区各配置16个BUFG;每个时钟区域最多支持12路独立全局时钟,通过水平时钟线实现信号传输。

②时钟输入目标:单个时钟区域由BUFH驱动的IO或时序元件。资源使用与布局规则:时钟引脚→BUFH→水平时钟线,其中时钟输入引脚需与BUFH位于同一时钟区域或水平相邻的时钟区域;每个时钟区域标配12个BUFH和12条水平时钟线,一对一占用。

③时钟输入目标:由CMT驱动的IO或时序元件。资源使用与布局规则:时钟引脚→CMT→BUFG→全局时钟树/时钟引脚→CMT→BUFR/BUFH→区域时钟树/水平时钟线,其中CMT需与时钟引脚位于同一时钟区域;当需多个CMT时,可将额外的CMT部署在垂直相邻的上下相邻时钟区域;每个时钟区域仅含1个CMT。

④时钟输入目标:单个时钟区域由BUFR驱动的IO或时序元件。资源使用与布局规则:时钟引脚→BUFR→区域时钟树,其中时钟引脚、BUFR、被驱动的IO及时序元件需同属于一个时钟区域;时钟引脚与BUFR/BUFIO存在绑定关系,不建议手动定位;每个时钟区域含4个时钟引脚和4个BUFR。

⑤时钟输入目标:最大3个相邻时钟区域的IO或时序元件。资源使用与布局规则:时钟引脚→BUFMR→BUFR→区域时钟树,其中被驱动的 I/O及时序元件需位于时钟引脚所在区域或其直接上下相邻区域,需通过BUFMR实现跨区域驱动;时钟引脚对与BUFR/BUFIO存在专属绑定关系,不建议手动定位;每个时钟区域含4个时钟引脚、4个BUFR、2个BUFMR。

⑥时钟输入目标:单个时钟区域(50个I/O)内的高性能SelectIO接口。资源使用与布局规则:时钟引脚→BUFIO→I/O时钟树,其中时钟引脚、BUFIO、被驱动的I/O触发器需同属一个时钟区域;时钟引脚对与BUFR/BUFIO存在专属绑定关系,不建议手动定位;每个时钟区域含4个时钟引脚和4个BUFIO,适配高性能I/O需求。

⑦时钟输入目标:最多两个相邻时钟区域内的高性能SelectIO接口。资源使用与布局规则:时钟引脚→BUFMR→BUFIO→I/O时钟树,其中时序I/O及BUFIO需位于时钟能力输入所在区域或其直接上下相邻区域,需通过BUFMR实现跨区域驱动。

4)通过BUFMR或CMT跨区域驱动时钟时,会占用相邻区域的部分资源(例如,BUFMR驱动相邻区域BUFR后,该区域一对时钟引脚将无法驱动自身区域时钟树,但可通过BUFH/BUFG驱动全局时钟线)。

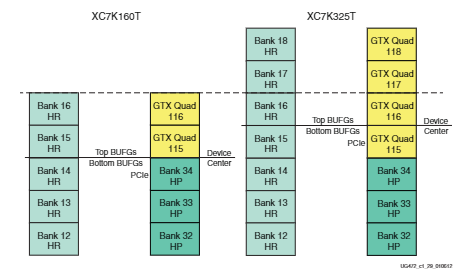

d)当在同封装的不同7系列FPGA器件间开展设计迁移时,需注意:用于将BUFGs划分为上半区16个、下半区16个资源的上下半区中心线,可能会相对于器件的其他列产生偏移。这种偏移会直接导致I/O bank与上下半区BUFGs的原有对齐关系发生改变,进而使访问BUFGs的时钟引脚的对齐逻辑出现差异。同封装内从大尺寸器件迁移至小尺寸器件时,中心线会向下偏移;从大尺寸器件迁移至小尺寸器件时,中心线则会向上偏移。

全局时钟资源

a)全局时钟资源是专为访问FPGA内各类资源的时钟输入而设计的专用互连网络。该网络具备低偏移、低占空比失真、低功耗、高抖动容限特性,同时支持超高频率信号传输。其主要包括三部分:时钟树与时钟网、时钟区域、全局时钟缓冲器。

1)时钟树与时钟网:7系列FPGA的时钟树采用低偏移、低功耗设计,未使用的分支会自动断开。时钟树还可驱动复位、时钟使能等逻辑资源,尤其适用于高扇出/高负载网络场景。在7系列FPGA架构中,全局时钟线的引脚访问不仅限于逻辑资源的时钟引脚,还可驱动CLB中除 CLK引脚外的其他引脚(如控制引脚SR和CE)。对于需要高速信号连接和大负载/高扇出的应用,该架构优势显著。

2)时钟区域:7系列器件通过时钟区域优化时钟分布,每个时钟区域最多支持12个全局时钟域。时钟区域的尺寸固定为50个CLB高度(对应 50个I/O引脚),横向覆盖芯片左侧或右侧区域。时钟主干将器件划分为左右两侧(非芯片物理中心),因此更大尺寸的7系列器件可包含更多时钟区域,数量范围为1至24个。

3)全局时钟缓冲器:

①7系列器件最多配备32个全局时钟缓冲器。

②CCIO可直接连接至同一半区器件内的任意全局时钟缓冲器,差分时钟引脚对可适配PCB上的差分或单端时钟。差分输入时,信号直接从引脚对的P端接入。单端输入时,必须使用P端(仅P端支持直接连接),此时N端仅可作为普通用户I/O,不可再用作时钟引脚。

③全局时钟缓冲器存在严格的上下半区约束:上半区的CMT仅能驱动上半区的BUFG,下半区CMT同理。同一半区的BUFG仅能为同半区的CMT提供反馈。

④GT与CMT的连接需区分器件类型:Virtex-7T/7XT器件因具备完整的GT列和I/O列结构,GT可直接连接CMT;而Spartan-7、Artix-7等其他系列器件,GT与CMT仅能通过BUFH(推荐方案)或BUFG间接连接。

⑤全局时钟缓冲器的输入源支持多种类型,包括时钟引脚、同半区CMT输出、相邻BUFG输出、BUFR、千兆收发器,以及不推荐使用的通用互连。32个BUFG分为上下半区两组(各16个),时钟引脚通过时钟主干列的垂直时钟网络间接驱动BUFG。所有直接连接BUFG的资源(如GTX收发器)均受上下半区限制,不可跨半区驱动。

⑥全局时钟缓冲器可覆盖器件内所有时钟区域,但单个时钟区域最多仅能承载12路不同时钟。一个时钟区域纵向覆盖HROW上下各25个CLB行,横向覆盖器件单侧的一半区域。

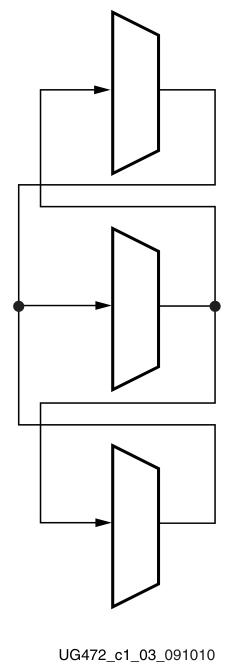

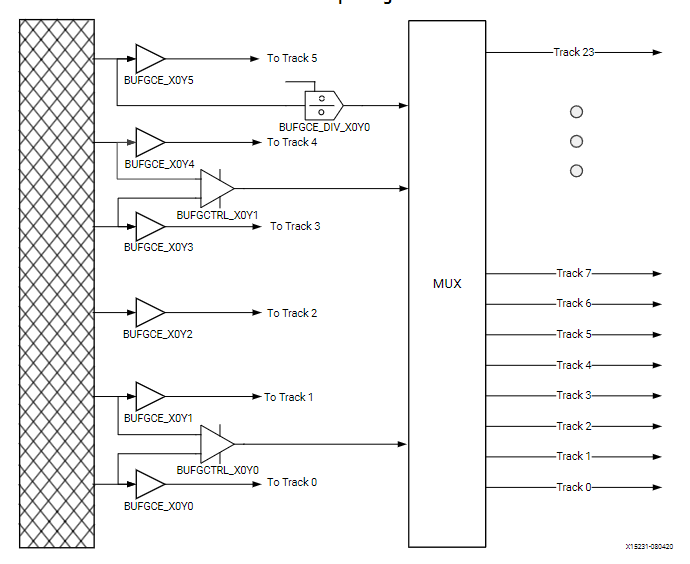

⑦时钟缓冲器支持配置为同步或异步无毛刺2:1多路复用器,BUFG级联具备专用路由资源,可支持超过两个时钟输入的选择,控制引脚功能丰富,输入切换稳健可靠。在7系列FPGA架构中,BUFGCTRL多路复用器及其衍生器件可在上下半区的16个缓冲器组内级联,形成两个独立的环网(上下半区各16个BUFGMUX)。

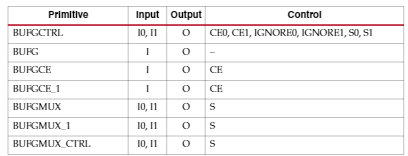

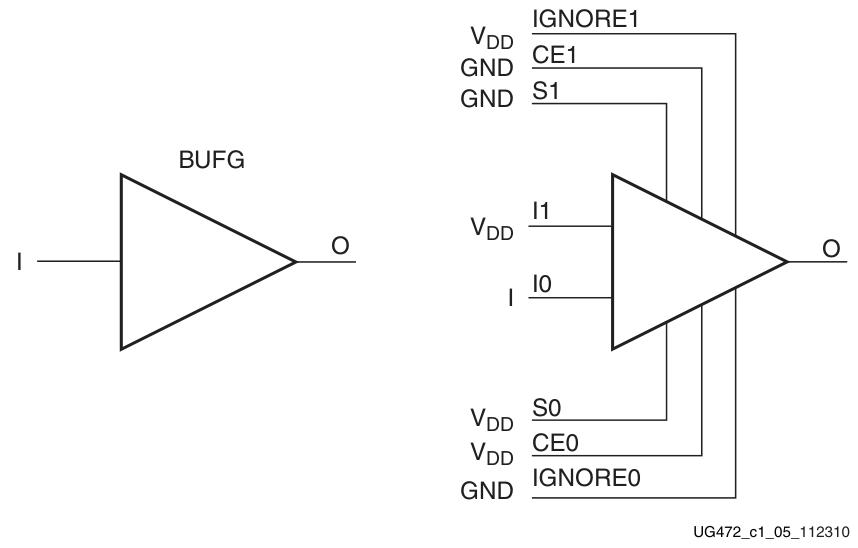

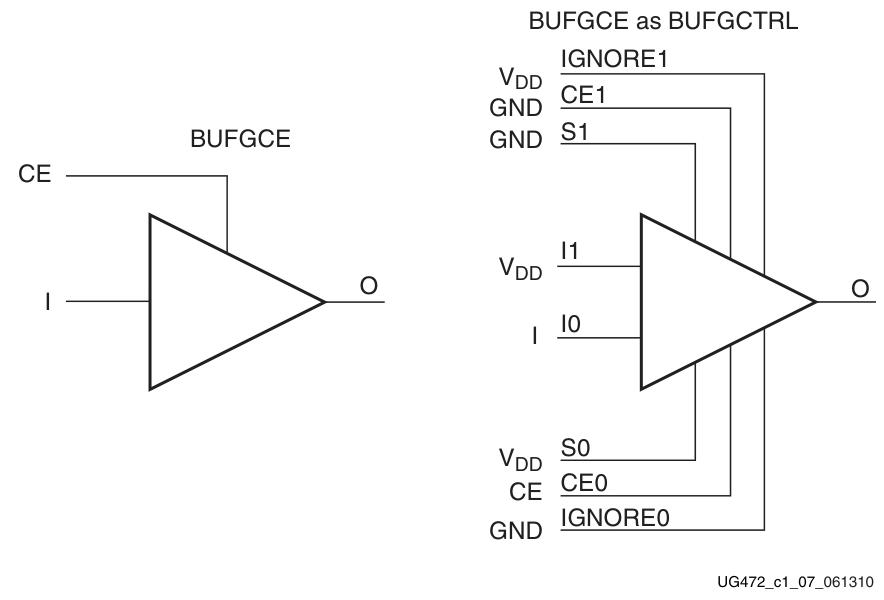

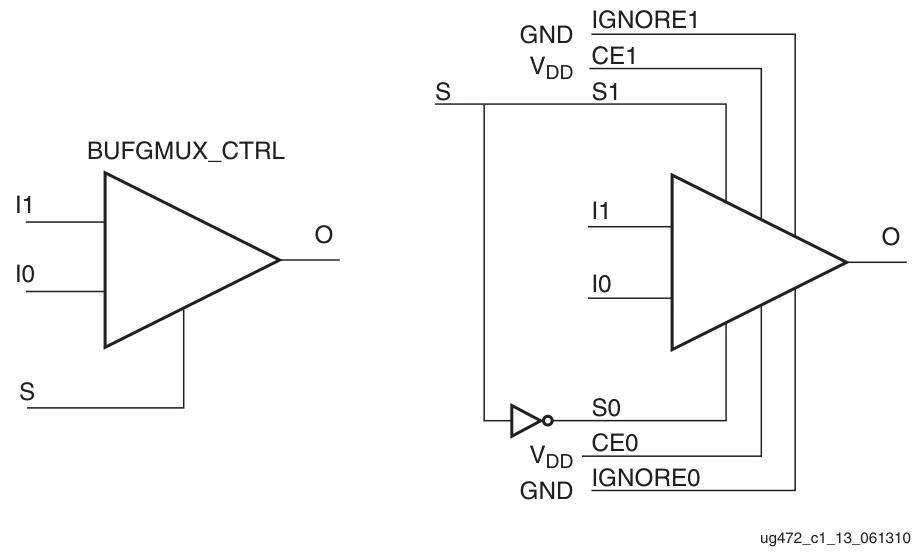

b)全局时钟缓冲器原语

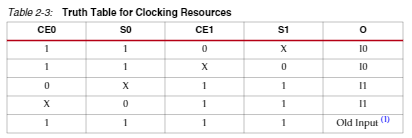

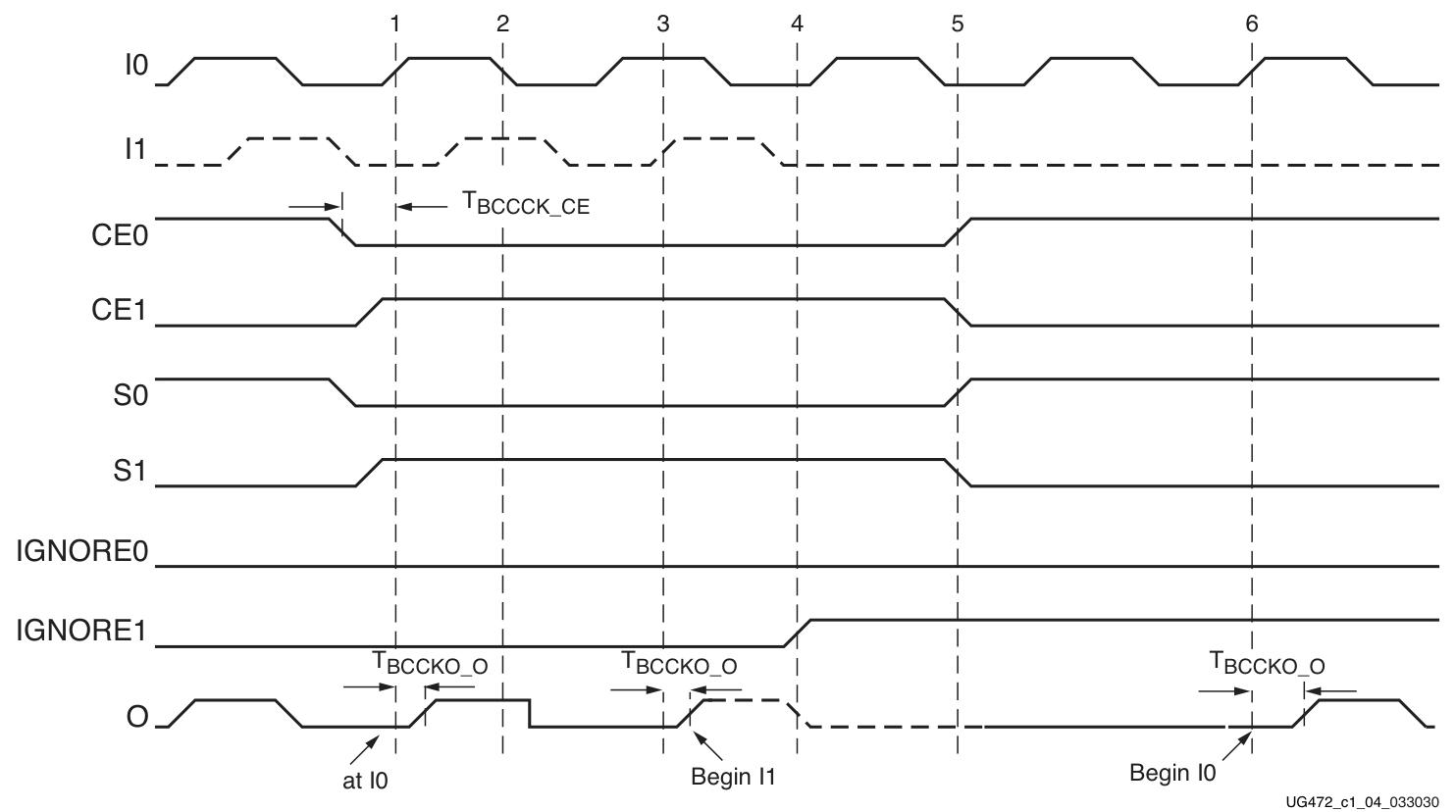

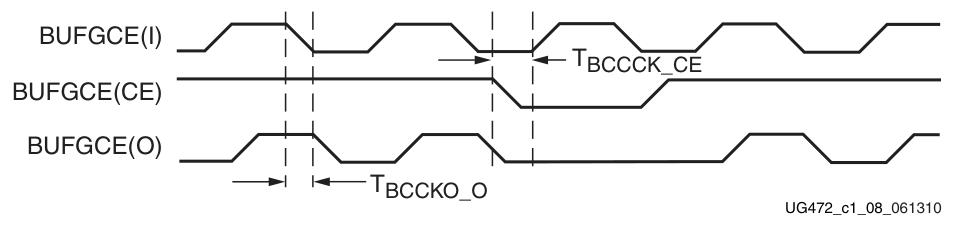

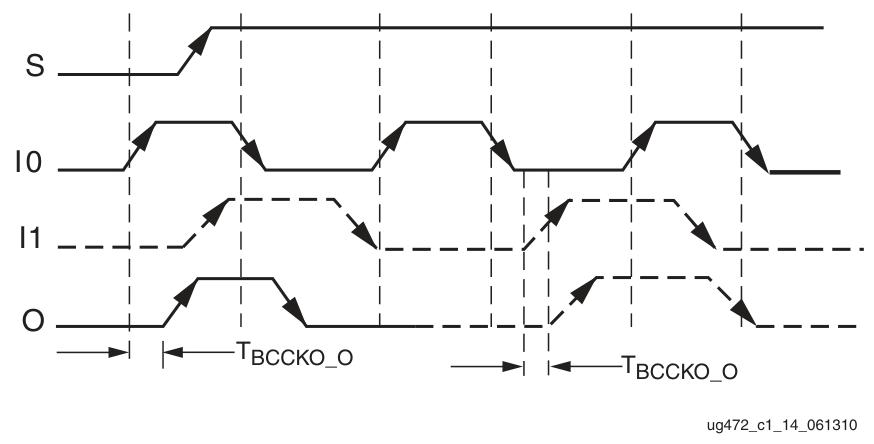

1)BUFGCTRL:支持两个异步时钟的无毛刺切换,其他所有全局时钟缓冲器原语均为其特定配置的衍生形态。BUFGCTRL配备四组选择控制信号(S0、S1、CE0、CE1)及两组忽略控制信号(IGNORE0、IGNORE1),共六路控制信号,用于精准调控输入I0和I1的切换逻辑。其核心切换机制为:

①无IGNORE断言时,默认下降沿敏感,输入切换前输出保持低电平。S0/S1选择信号变化后,需先等待当前选中时钟完成高→低电平转换,输出维持低电平,再等待待选时钟完成高→低电平转换,新时钟才开始驱动输出,确保无毛刺。通过INIT_OUT属性可切换为上升沿敏感,切换前输出保持高电平。

②IGNORE断言时,可跳过电平转换检测,选择信号变化瞬间即切换输出(IGNORE0脱离I0,IGNORE1脱离I1),实现异步快速切换。

③需将对应选择对(S0+CE0或S1+CE1)置高才能选中目标输入,两者不可同时置高。常规用法为一选一接高(一组引脚作选择线,另一组固定接高电平),避免选择信号冲突。

①时钟事件1之前,输出O始终由I0驱动;

②在时间事件1的上升沿来临前,于时序节点T_BCCCK_CE,控制信号CE0与S0同步置低;与此同时,控制信号CE1与S1同步置高,完成时钟输入的选择切换准备;

③时序推进至时间事件3之后的T_BCCKO_O节点,输出O正式切换为由输入I1驱动。此切换的核心前提是:先完成I0的高→低电平转换(对应时间事件2),再完成I1的高→低电平转换,确保切换过程无毛刺;

④时间事件4触发IGNORE1信号断言,启动异步切换模式;

⑤时间事件5时,控制信号反向切换:CE0与S0置高,CE1与S1置低;在时间事件6之后的T_BCCKO_O节点,输出O从I1快速切换回I0,且无需依赖I1的高→低电平转换,实现异步无等待切换。

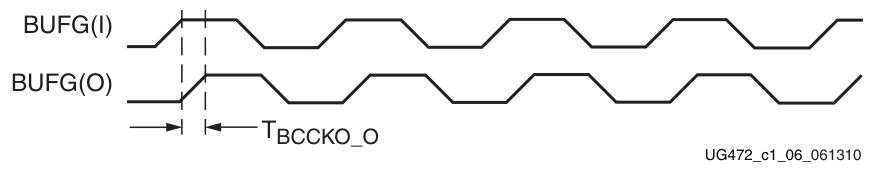

2)BUFG

3)BUFGCE/BUFGCE1:与基础款BUFG不同,BUFGCE是一款具备单时钟输入、单时钟输出、独立时钟使能线的时钟缓冲器,其本质是通过将BUFGCTRL的部分引脚固定为逻辑高电平或低电平衍生而来的专用配置形态。BUFGCE的核心工作机制如下:CE信号为高电平时,时钟脉冲正常通过缓冲器,输出跟随输入变化;若CE在输入时钟上升沿前为低电平,则后续时钟脉冲被阻断,输出保持低电平;CE在时钟高电平期间的电平波动不影响输出状态,且时钟禁用前会完整输出当前高电平脉冲,确保时序完整性。需注意,CE信号需满足建立时间要求,否则可能引发输出毛刺。

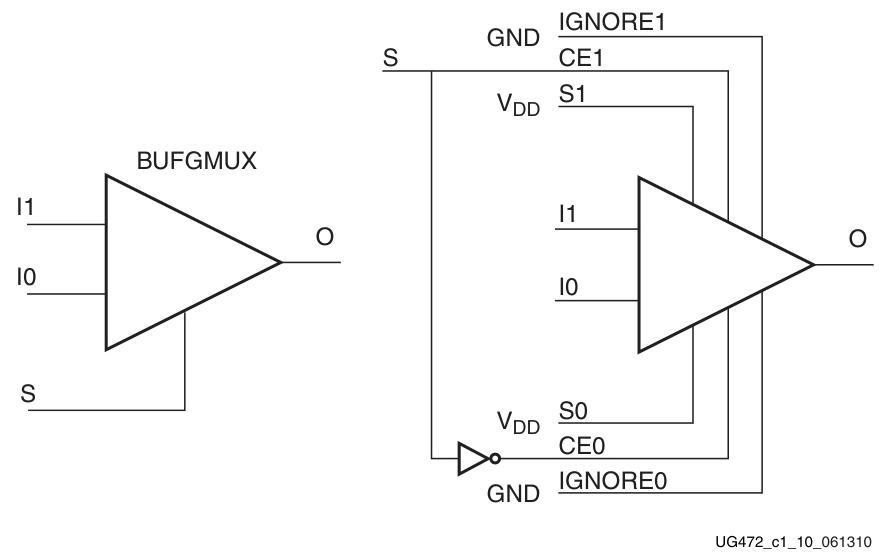

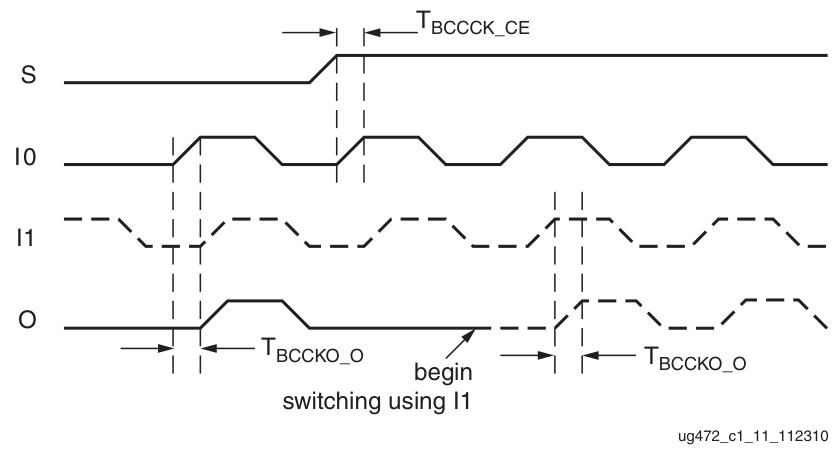

4)BUFGMUX/BUFGMUX_1:BUFGMUX是一款专为双时钟输入切换设计的多路复用时钟缓冲器,具备单输出和单选择线,其核心架构基于BUFGCTRL衍生而来。通过将BUFGCTRL的部分引脚固定为逻辑高/低电平,简化为专注于时钟切换的专用形态。BUFGMUX的核心特性的是:采用CE引脚作为选择线,切换过程需严格满足建立时间要求,否则易引发输出毛刺。其切换逻辑与BUFGCTRL的CE引脚完全一致:以当前驱动时钟为I0为例,当选择线S置高后,若I0处于高电平,多路复用器会等待I0完成高→低电平转换;I0转为低电平后,输出维持低电平,直至新时钟I1完成高→低电平转换,最终实现无毛刺切换。

注意:①S信号用于时钟源选择,直接决定输出时钟是I0还是I1(S=0输出I0,S=1输出I1,逻辑固定),是BUFGMUX_CTRL的核心切换信号。其时序约束宽松,建立/保持时间仅影响是否多传递一个原时钟脉冲,即使违反约束,也不会产生毛刺,仅输出切换延迟1个时钟周期。其无毛刺风险,切换逻辑基于时钟下降沿同步,即使S信号异步变化,也会等待时钟电平转换后切换,避免信号重叠。②CE信号用于时钟使能,控制时钟是否允许通过缓冲器(CE=1时钟正常输出,CE=0时钟被阻断),不负责时钟源切换,仅控制输出启停。时序约束严格,CE需严格满足建立/保持时间,否则必然产生毛刺(因CE切换速度快于S,易与时钟信号冲突)。高毛刺风险,若用于选择时钟源,CE信号与时钟信号无同步机制,时序违规时直接导致输出信号冲突,产生毛刺。③若需切换 + 使能组合功能(如先切换时钟源,再开启输出),可先用S信号选择目标时钟,再用CE信号使能输出(需搭配BUFGCTRL或多原语组合,如BUFGCTRL+BUFGCE)。

5)BUFGMUX_CTRL:是一款具备两个时钟输入(I0、I1)、一个时钟输出(O)和一条选择线(S)的时钟缓冲器。通过将BUFGCTRL的部分引脚固定为逻辑高电平或低电平,简化为专注于双时钟无毛刺切换的专用形态。BUFGMUX_CTRL的核心控制信号为S引脚,其切换逻辑与BUFGCTRL的S引脚完全一致:S信号可在任意时刻切换且不会产生毛刺,其建立/保持时间仅影响是否传递原选中时钟的额外一个脉冲。若S在建立时间前且I0从高电平转为低电平前变化,输出不会传递I0的额外脉冲;若S在保持时间后变化,输出会传递该额外脉冲。即使 S违反建立/保持要求,输出也不会产生毛刺,仅可能多传递一个脉冲。无论何种情况,输出都会在较慢时钟的三个周期内完成向新时钟的切换。需注意,S0和S1的建立/保持时间以时钟下降沿为基准,而非CE0和CE1的上升沿。此外,BUFGMUX_CTRL还支持两项额外功能:一是配置后可预选择I0或I1作为初始输入;二是可自定义配置后的输出初始状态(高电平或低电平)。

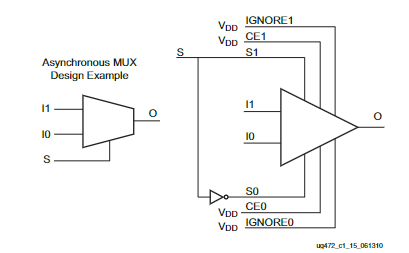

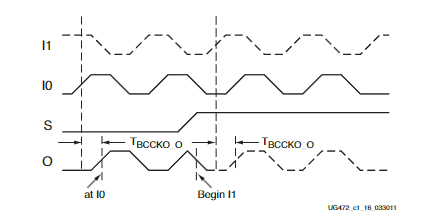

6)Asynchronous MUX:在某些应用场景中,需要立即在两个时钟输入之间进行切换,或者绕过BUFGCTRL的边沿检测机制。例如,当某个时钟输入停止切换时,由于BUFGCTRL无法检测到时钟边沿,正常的切换条件将无法满足,导致时钟输出被锁定。此时可以使用异步多路复用器模式。关键机制是,当IGNORE信号被置为高电平时,BUFGCTRL的毛刺保护功能被禁用,从而实现即时切换。

区域时钟资源

a)区域时钟网络是独立于全局时钟网络的专用时钟网络。与全局时钟不同,区域时钟信号(由BUFR驱动)的覆盖范围仅限于一个时钟区域,而单个I/O时钟信号则驱动一个单独的I/O组。这些网络特别适用于源同步接口设计。7系列FPGA的区域时钟资源和网络包含以下路径与组件:时钟引脚、IO时钟缓冲器BUFIO、区域时钟缓冲器BUFR、区域时钟网络、多区域时钟缓冲器BUFMR/BUFMRCE、水平时钟缓冲器BUFH/BUFHCE、高性能时钟。

b)时钟引脚IO并非普通I/O,而是具备专用物理走线直接连接至时钟网络(BUFIO/BUFMR/BUFR)的特殊引脚。这从物理上保证了外部时钟信号能以最小延迟、最低抖动进入FPGA的专用时钟分配系统。一个CCIO可以驱动本区域内的任何BUFR,但只有特定的专用CC引脚才能以1:1的关系驱动特定的BUFIO,并且只有MRCC引脚才能驱动BUFMR。这意味着,一个CCIO仅与一个特定的BUFIO或BUFMR存在单一连接。

c)BUFIO驱动I/O组内部一个专用的时钟网络,该网络独立于全局时钟资源。因此BUFIO非常适用于源同步数据采集(转发/接收时钟分发)。BUFIO可由位于同一I/O组的时钟引脚、来自MMCM的HPC、来自同一及相邻区域的BUFMR驱动。在一个时钟区域内,每个I/O组有四个BUFIO。每个BUFIO可以驱动同一区域/I/O组内的单个I/O时钟网络。BUFIO无法驱动逻辑资源,因为I/O时钟网络仅延伸到同一I/O组/时钟区域的I/O列。

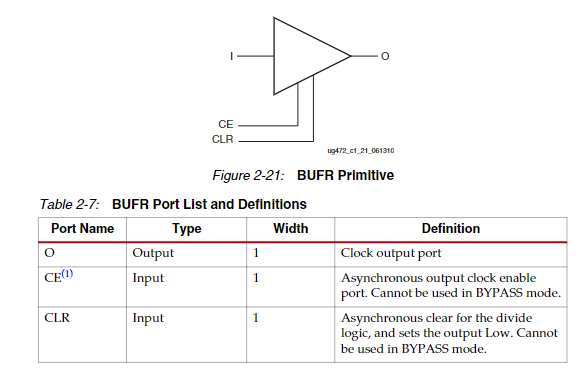

d)BUFR驱动一个时钟区域内的专用时钟网络,该网络独立于全局时钟树。不同于BUFIO,BUFR能够驱动I/O逻辑以及逻辑资源。BUFR可由同一时钟区域内的时钟引脚、本地互连、MMCM的高性能时钟输出(CLKOUT0至CLKOUT3)、来自同一及相邻区域的BUFMR驱动。此外BUFR能够产生相对于输入时钟频率进行分频的时钟输出。分频值可以是1到8之间的整数。因此BUFR非常适用于需要进行时钟域转换或串并转换的源同步应用。

1)BUFR可由以下资源驱动:同一时钟区域内的SRCC/MRCC、使用BUFMR驱动来自相邻时钟区域的MRCC、同一时钟区域来自MMCM的时钟输出0-3(驱动HPC)、通用互连。

2)每个I/O列均支持BUFR。一个器件中包含两个I/O列。BUFR也可直接驱动MMCM的时钟输入和BUFG。

3)当CE引脚置位/清零时,输出时钟信号将开启/关闭。当全局置位/复位信号为高电平时,即使CE引脚保持高电平,BUFR输出也会被保持在复位状态。只有在GSR信号被清零且BUFR输入端有时钟信号存在时,BUFR输出才会开始翻转。

4)BUFR的时钟分频功能通过软件中的BUFR_DIVIDE属性进行控制。BUFR的传播延迟在BUFR_DIVIDE = 1和BUFR_DIVIDE = BYPASS两种模式下有所不同。当设置为1时,其延迟略大于BYPASS模式。所有其他分频系数的延迟均与BUFR_DIVIDE = 1时相同。除BYPASS模式外,输入时钟与输出时钟之间的相位关系在所有分频模式下均保持一致。

5)BUFR非常适合于需要进行时钟域交叉或串并转换的源同步应用。与BUFIO不同,BUFR能够为FPGA中除IOB之外的逻辑资源提供时钟。

e)区域时钟网络

1)除全局时钟树和网络外,7系列器件还包含区域时钟树和网络。区域时钟树同样为低偏斜、低功耗运行而设计,未使用的分支会被断开。当使用全部逻辑资源时,区域时钟树也负责管理负载/扇出。区域时钟网络不会遍布整个7系列器件,而是仅限于一个时钟区域内。一个时钟区域包含四条独立的区域时钟网络。要接入区域时钟网络,必须实例化使用BUFR。

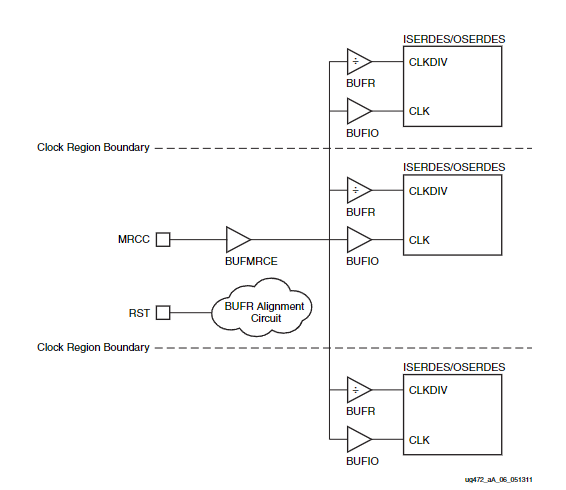

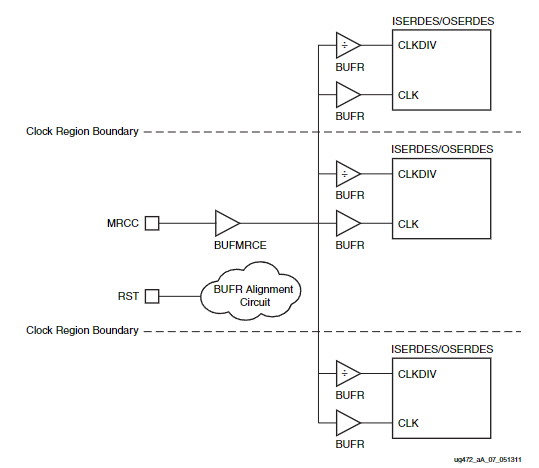

f)多区域时钟缓冲器BUFMR/BUFMRCE

1)每个I/O组中有两个BUFMR,每个缓冲器可由同一组中的一个特定MRCC驱动。BUFMR可以驱动同一区域/组以及上方和下方区域/组中的BUFIO和/或BUFR。BUFR和BUFIO原语必须单独实例化。

2)当使用BUFR的分频器功能(非旁路模式)时,必须通过置低CE引脚来禁用BUFMR,对BUFR进行复位(通过置位CLR来清除),然后再置位CE信号。此操作顺序可确保所有BUFR输出时钟的相位对齐。如果未使用BUFR内部的分频器,则电路拓扑仅需使用BUFMR。

3)BUFMR的输入包括:同一IO组中的MRCC、同一区域内的GT时钟。

4)BUFMR是一个带有时钟使能CE的时钟输入/输出缓冲器。置低CE引脚将停止输出时钟。BUFMR必须通过驱动BUFR和BUFIO,才能将时钟信号路由至其所在区域/组以及上方和下方的相邻区域/组。BUFMR由同一区域内的MRCC引脚或GT时钟驱动。

5)CE_TYPE属性应始终设置为SYNC,以确保时钟输出无毛刺。如果BUFMRCE的时钟输出被停止(例如通过置低CE),则必须在 BUFMRCE再次启用后对BUFR进行复位(CLR)。BUFMRCE上CE功能的主要目的是为BUFR和BUFIO提供同步且相位对齐的时钟。

g)水平时钟缓冲器BUFH/BUFHCE

1)BUFH在单个区域内驱动一条水平全局时钟树主干线。每个区域提供12个BUFH。每个BUFH都具有一个时钟使能引脚CE,可动态关闭时钟。BUFH可由以下资源驱动:同一区域内的MMCM/PLL输出、BUFG输出、同一或水平相邻时钟区域内的GT输出时钟、本地互联、来自同一水平相邻区域/组中左侧或右侧I/O组的时钟引脚。

2)BUFH的时钟使能引脚CE能完全关闭时钟,从而有可能实现功耗优化。与驱动两个相邻区域的BUFG相比,BUFH的功耗和抖动更低。

h)高性能时钟HPC

1)7系列FPGA的每个I/O组包含四条高性能时钟通道。这些时钟通道是通往I/O中BUFIO和BUFR的直接、差分连接路径,因此具有极低抖动和最小占空比失真的特性。在I/O列中,高性能时钟连接至BUFIO/BUFR并驱动I/O逻辑。由于CMT列紧邻I/O列,高性能时钟可直接驱动紧靠CMT的I/O组。高性能时钟仅可由MMCM的CLKOUT[3:0]输出驱动。

i)低功耗时钟网络

1)7系列FPGA的时钟架构为实现时钟门控提供了一种直接的方法,旨在关闭设计中的部分电路以实现节能。大多数设计都包含若干未被使用的BUFGCE或BUFHCE资源。具体实现方式是:一个时钟信号可以驱动一个BUFGCE或BUFHCE的输入,而BUFGCE的输出可以驱动设计中不同的逻辑区域,BUFHCE则能驱动单个区域。例如,若设计中需要始终保持运行的所有逻辑可以被约束在少数几个时钟区域内,那么BUFGCE的输出便可驱动这些区域。或者,如果一个BUFHCE驱动一个位于单个区域内的接口,那么该接口可以在非工作期间被关闭。通过切换BUFGCE或BUFHCE的使能端,可以简单地停止目标逻辑区域的所有动态功耗消耗。可使用Xilinx功耗估算器工具来估算节能效果。估算方法是:将对应时钟网络上的频率设置为0MHz,或向该工具提供相应的激励数据以计算功耗差异。

CMT

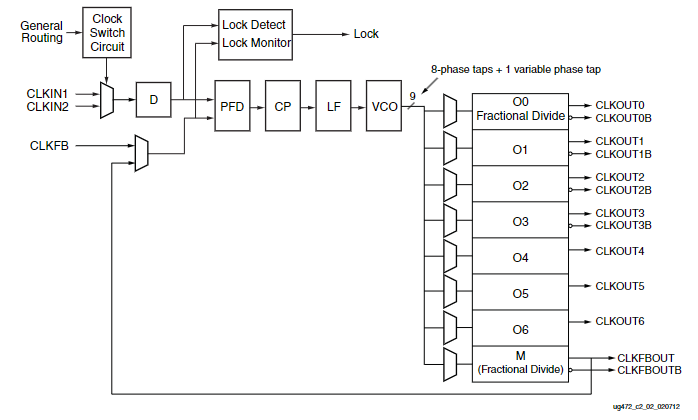

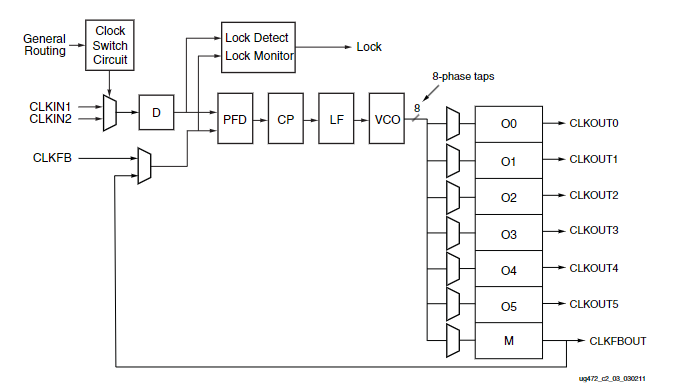

a)时钟输入连接允许多种资源为MMCM/PLL提供参考时钟。输出分频器的数量为8个,其中部分能够输出反相时钟信号(180度相移)。为了向后兼容DCM,可以选择九个独立的输出来将DCM的输出直接映射到MMCM。7系列FPGA的MMCM能够在任一方向进行无限精细的相移,并可用于动态相移模式。精细相移的分辨率取决于VCO频率。CLKFBOUT和CLKOUT0支持分数分频功能(增量为1/8,即0.125),以提供更强大的时钟频率合成能力。7系列FPGA还为MMCM增加了扩频时钟生成能力。如果不使用MMCM的扩频功能,外部输入时钟上的扩频将不会被滤除,从而传递到输出时钟。

b)MMCM/PLL

1)MMCM和PLL用作宽频率范围的频率合成器,作为外部或内部时钟的抖动滤波器,并用于时钟去偏斜。MMCM支持而PLL不具备的额外功能包括:①通过CLKOUT[0:3]直接连接到BUFR或BUFIO的高性能时钟路径;②反相时钟输出(CLKOUT[0:3]B);③CLKOUT6输出;④CLKOUT4_CASCADE级联功能;⑤CLKOUT0_DIVIDE_F/CLKFBOUT_MULT_F的分数分频;⑥精细相移;⑦动态相移。

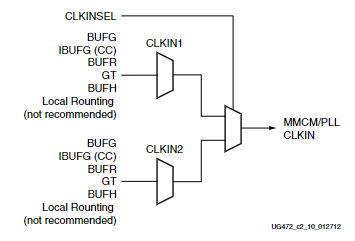

2)输入多路复用器从IBUFG、BUFG、BUFR、BUFH、GT收发器(仅CLKIN)、互连(不推荐)中选择参考时钟和反馈时钟。每个时钟输入具有一个可编程计数器分频器。相位频率检测器比较输入参考时钟和反馈时钟上升沿的相位和频率。如果维持了最小的高/低脉冲宽度,则占空比是次要的。PFD产生一个与两个时钟之间相位和频率差成比例的信号。该信号驱动电荷泵和环路滤波器,从而为VCO生成一个参考电压。PFD产生一个升压或降压信号给电荷泵和环路滤波器,以决定VCO应该以更高还是更低的频率运行。当VCO工作频率过高时,PFD激活降压信号,导致控制电压降低,从而降低VCO工作频率;当VCO工作频率过低时,升压信号将提高电压。VCO产生八个输出相位和一个用于精细相移的可变相位。每个输出相位均可被选为输出计数器的参考时钟。每个计数器都可以根据特定的客户设计进行独立编程。还提供了一个特殊的计数器M。该计数器控制MMCM和PLL的反馈时钟,从而实现宽范围的频率合成。除了整数分频输出计数器外,MMCM还为CLKOUT0和CLKFBOUT增加了分数计数器。

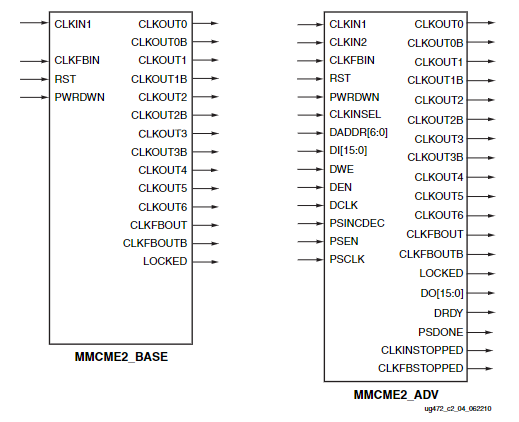

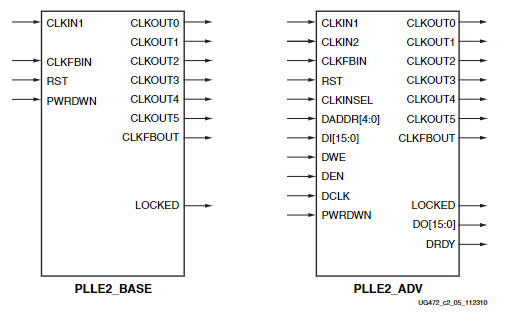

c)MMCM/PLL原语

1)MMCME2_BASE原语提供了独立MMCM最常用功能的访问接口。使用MMCME2_BASE时,可利用的功能包括时钟去偏斜、频率合成、粗相位偏移、占空比编程。

2)MMCME2_ADV原语在提供MMCME2_BASE所有功能的基础上,进一步开放了额外的高级端口,支持时钟切换、访问动态重配置端口、动态精细相位偏移。

3)7系列FPGA的MMCM和PLL是混合信号模块,旨在支持时钟网络去偏斜、频率合成、抖动消除。

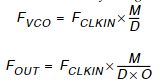

4)七个O计数器可以独立编程。例如,O0可以被设置为2分频,而O1被设置为3分频。唯一的约束是,由于单个VCO驱动所有输出计数器,因此所有输出计数器的VCO工作频率必须相同。

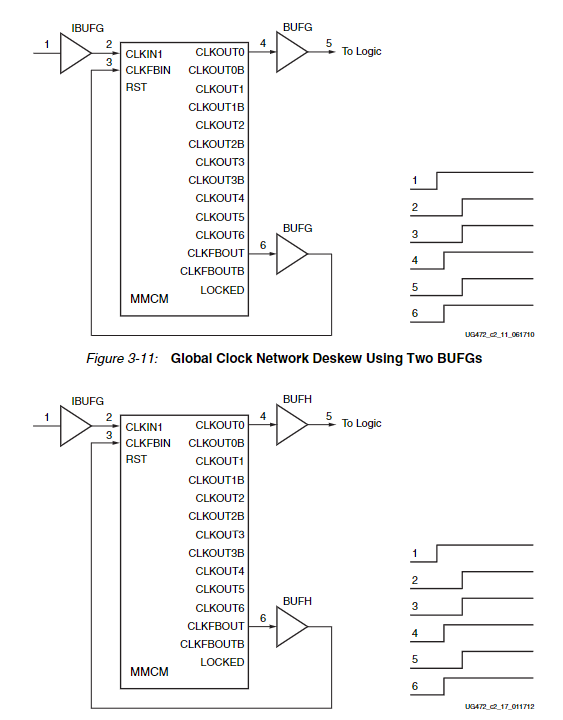

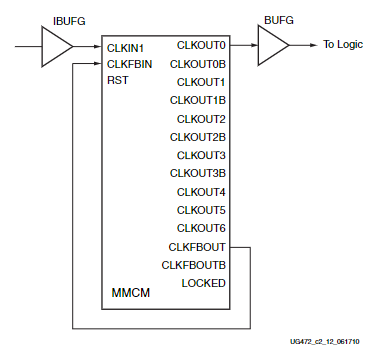

d)时钟网络去偏斜

1)在许多情况下,设计者不希望时钟网络延迟计入其I/O时序预算,因此他们使用MMCM/PLL来补偿此时钟网络延迟。7系列FPGA支持此功能。具体做法是:将一个与参考时钟CLKIN频率匹配的时钟输出(始终为CLKFBOUT)连接到器件同一半区的BUFG,并反馈至MMCM/PLL的CLKFBIN反馈引脚。其余输出仍可用于将时钟分频以产生额外合成的频率。在此配置下,所有输出时钟与输入参考时钟都具有确定的相位关系。

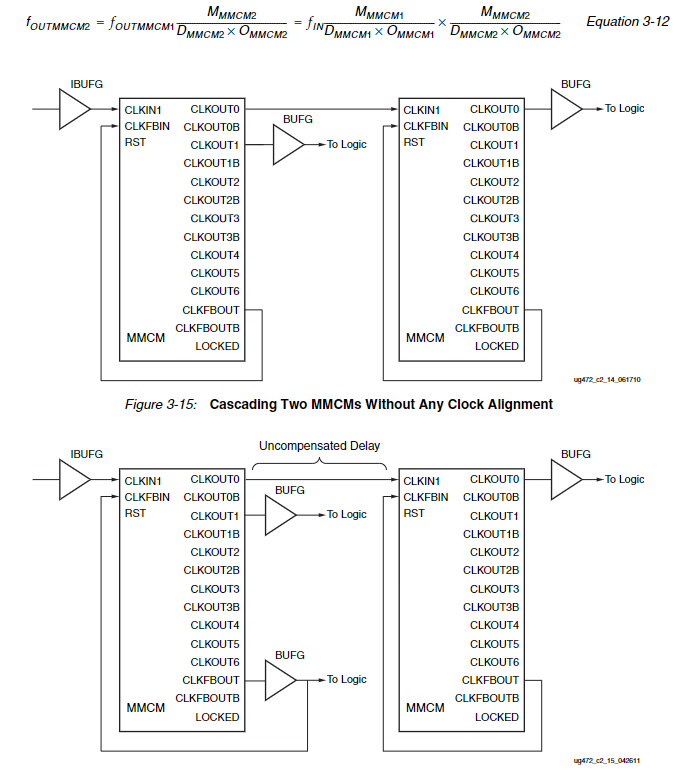

2)MMCM或PLL的CLKOUT0--CLKOUT3输出可用于级联到其他MMCM/PLL。然而,级联的MMCM/PLL之间的输出时钟会存在相位偏移。

e)仅使用整数分频的频率合成

1)MMCM和PLL也可用作独立的频率合成器。在这种应用模式下,MMCM/PLL不用于对时钟网络进行去偏斜,而是为其他模块生成输出时钟频率。在此模式下,MMCM/PLL的反馈路径在内部连接,这使得所有布线保持局部化,从而将抖动降至最低。

2)假设有一个33MHz的外部参考时钟。此参考时钟可以是一个晶体振荡器或另一个MMCM的输出。将M计数器设置为32,可以使VCO振荡在1056MHz(33 MHz × 32)。MMCM的输出被编程以提供一个528MHz的处理器时钟、一个264MHz的接口时钟、一个176MHz的时钟、一个132MHz的内存接口时钟、一个66MHz的接口时钟、一个33MHz的接口时钟。参考时钟与输出时钟之间不需要特定的相位关系,但各输出时钟之间具有确定的相位关系。

f)MMCM中的分数分频频率合成

1)7系列FPGA在CLKOUT0输出路径上支持分数(非整数)分频。分数分频的分辨率为1/8(即0.125),这实际上将可合成的频率数量增加了八倍。例如,如果CLKIN频率为100MHz,M分频值设置为8,则VCO频率为800MHz。此时,CLKOUT0可以用于对这800MHz的VCO频率进行进一步的分数分频(例如,设置CLKOUT0_DIVIDE = 2.5,从而得到一个320MHz的输出频率)。需要注意的是:当使用分数分频器时,工作于分数模式的输出时钟,其占空比不可编程。

g)抖动滤除

1)MMCM和PLL能够降低参考时钟固有的抖动。MMCM和PLL可以作为独立的功能模块实例化,用于在外部时钟被驱动到另一个模块之前,对其进行抖动过滤。作为抖动过滤器时,通常假定MMCM和PLL将起到缓冲器的作用,并在输出端再生输入频率(例如,F_IN = 100 MHz, F_OUT = 100 MHz)。通常,通过将MMCM的BANDWIDTH属性设置为Low,可以实现更强的抖动过滤效果。但需注意,将BANDWIDTH设置为Low可能会增加MMCM的静态相位偏移。

h)不同场景决策

1)当首要目标是为芯片内部逻辑提供多个纯净、同源且频率精确的时钟时,选择内部反馈模式(频率合成器模式),此时反馈路径最短,不受外部电源噪声和布局影响,可获得最佳的抖动性能。所有输出时钟相位关系确定。代价是无法补偿外部时钟网络的延迟,输出时钟与输入时钟的相位关系不确定。

2)当首要目标是实现数据在I/O引脚处的精确采样(建立/保持时间最优)时,选择外部反馈模式(时钟网络去偏斜模式),此时通过补偿BUFG/BUFH的延迟,使得输出到I/O寄存器的时钟边沿与输入参考时钟边沿在器件引脚处对齐,为源同步接口提供了完美的时序关系。代价是反馈路径更长,引入更多噪声,抖动性能略逊于内部反馈模式。

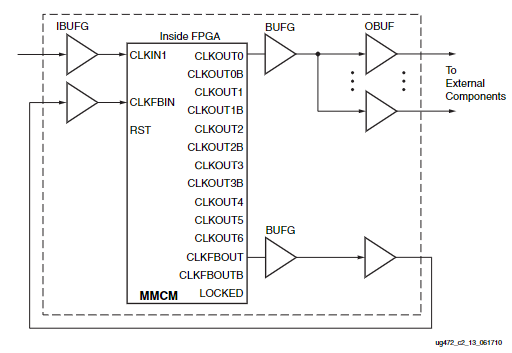

3)当首要目标是在板级实现多个器件间的时钟零延迟时,选择外部反馈模式,并将反馈路径引至器件引脚(零延迟缓冲模式),此时补偿FPGA内部延迟和板级走线延迟,使多个器件共享同一时钟边沿,代价是需要占用额外的引脚和板级布线,设计最复杂。

4)在确认了反馈路径后,通过BANDWIDTH属性来调节抖动过滤与动态性能的平衡。BANDWIDTH=LOW是更强的抖动过滤,但锁定时间更长,静态相位误差可能更大,适用于参考时钟质量较差,且系统能接受较长启动时间的场景。BANDWIDTH=HIGH或OPTIMIZED是抖动过滤能力稍弱,但锁定更快,动态响应更好,适用于参考时钟质量较好,或需要快速切换、调整的场景。

5)最后确认是否需要非整数分频、是否需要动态调整相位或频率、是否需要切换故障时钟源。

i)限制条件

1)MMCM/PLL存在一些必须遵守的限制。这些限制总结在7系列FPGA数据手册(DS181、DS182、DS183)的电气规范中。通常,主要的限制涉及VCO工作范围、输入频率、占空比可编程性、相位偏移。此外各时钟区域的时钟资源与连接差异,它们与其他时钟元件(引脚、GT收发器、时钟缓冲器)的连接也存在限制。MMCM/PLL的级联只能在相邻的CMT之间进行。

2)压控振荡器工作范围/最小与最大输入频率。

3)占空比可编程性:在特定的压控振荡器工作频率下,只能实现离散的占空比。根据CLKOUT_DIVIDE的值,存在一个最小和最大范围,其步进大小也取决于CLKOUT_DIVIDE的值。Clocking Wizard会给出特定CLKOUT_DIVIDE值下所有可能的占空比值。

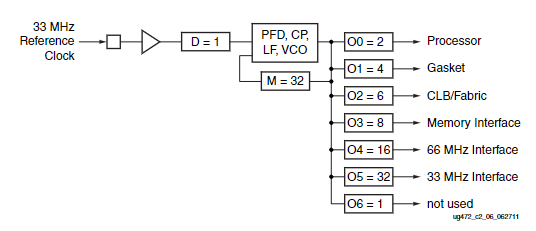

4)相位偏移:

①在许多情况下,需要在时钟之间进行相位偏移。MMCM提供了多种实现相位偏移的选项。PLL也具备基本的静态相位偏移能力。

②静态相位偏移模式可以通过选择压控振荡器八个输出相位中的一个来实现,此外还可以根据CLKOUT分频值,在CLKOUT输出计数器中进行额外的精细相位偏移。

③7系列FPGA的MMCM还支持固定或动态模式下的插值精细相位偏移功能。MMCM的相位偏移功能非常强大,但也可能带来复杂的应用场景。通过使用Clocking Wizard,可以基于MMCM的配置设置来确定允许的相位偏移值。

④静态相位偏移的时间分辨率定义为:SPS = 1 / (8 x F_VCO) 周期。由于压控振荡器可以提供八个彼此相差45°的时钟相位,因此总是可以提供0°、45°、90°、135°、180°、225°、270°、315°的相位偏移设置。压控振荡器频率越高,相位偏移的分辨率就越小。

⑤由于压控振荡器有明确的工作范围,因此可以将相位偏移分辨率限定在 1 / (8 x F_VCO_MAX) 到 1 / (8 x F_VCO_MIN) 周期之间。

⑥每个CLKOUT输出计数器都可以独立编程,使得每个输出能够基于所选的压控振荡器相位和CLKOUT计数器分频值,获得额外的以度为单位的相位偏移分辨率。CLKOUT相位偏移值的粒度可以计算为45° / CLKOUT_DIVIDE值。最大相位偏移范围也由CLKOUT_DIVIDE值决定。

⑦可以对CLKFBOUT反馈时钟进行相位偏移。在这种情况下,所有CLKOUT输出时钟相对于CLKIN都会发生负向的相位偏移。

⑧两个分数计数器(CLKFBOUT和CLKOUT0)也具备静态相位偏移能力。例如,如果分数分频值为2.125,那么一个静态相位偏移步长就是360 / (2.125 × 8) = 21.176 度。

⑧MMCM中的插值精细相位偏移模式具有线性的偏移行为,其与CLKOUT_DIVIDE值无关,相位偏移分辨率仅取决于压控振荡器频率。在此模式下,输出时钟可以按1 / (56 x F_VCO) 的线性增量进行360°循环旋转。如果压控振荡器运行在600MHz,那么相位分辨率大约为30ps(取整);在1.6GHz时,相位分辨率大约为11ps(取整)。

j)MMCM计数器级联

1)CLKOUT6分频器可以级联到CLKOUT4分频器。这提供了一种实现大于128的分频比的能力。CLKOUT6的输出作为CLKOUT4分频器的输入。级联后的分频器输出与其他所有分频器输出之间存在一个静态相位偏移。

k)MMCM/PLL编程

1)编程MMCM/PLL需要以下信息:参考时钟周期、输出时钟频率(最多七个)、输出时钟占空比(默认为50%)、相对于时钟原始0相位的输出时钟相位偏移度数、MMCM/PLL的期望带宽(默认为OPTIMIZED,带宽由软件选择)、补偿模式(由软件自动确定)、以单位间隔表示的参考时钟抖动(即参考时钟周期的百分比)。

2)第一步是确定输入频率。这允许通过使用最小和最大输入频率来定义D计数器的范围,使用VCO工作范围来确定M计数器的范围,以及确定输出计数器的范围,从而推导出所有可能的输出频率。可能的频率组合数量非常庞大。当使用整数分频时,在最坏情况下,将有106 × 64 × 136 = 868,363种可能的组合。实际上,不同频率的总数会少一些,因为并非所有M和D计数器的整个范围都能实现,并且不同设置之间存在重叠。

3)F_PFD = F_IN / D;F_PFD = F_VCO / M。F_PFD必须在器件规定的最小值和最大值之间(例如7系列FPGA典型范围是10MHz到550MHz)。这个范围是MMCM/PLL芯片物理特性决定的,绝对不能违反。

4)确定M和D的过程是一个多约束条件下的搜索优化过程。目标是在所有硬性限制下,找到能产生所需输出频率F_OUT的合法M、D、O组合,并通常希望VCO运行在较优的频率点。

第一步:输入频率F_IN已知。输出频率需求已知。VCO频率范围已知。PFD频率范围已知。

第二步:根据F_PFD范围确定D的可能取值范围。这是由F_PFD = F_IN / D决定的。D必须是整数。D_MAX = floor( F_IN / F_PFD_MIN ) (向下取整);D_MIN = ceil( F_IN / F_PFD_MAX ) (向上取整);D_MIN ≤ D ≤ D_MAX。

第三步:根据VCO的范围和每个D值,确定M的可能取值范围。F_VCO_MIN ≤ M x (F_IN / D) ≤ F_VCO_MAX。

第四步:引入输出频率需求,筛选MD对,并计算O。对于每一个合法的 (D, M) 组合,我们可以计算出一个基准VCO频率:F_VCO = M x (F_IN / D)。对于每一个需要的输出频率F_OUT_i,必须存在一个整数(或分数)输出分频器O_i,使得:F_OUT_i = F_VCO / O_i => O_i = F_VCO / F_OUT_i。对于普通输出口,O_i 必须是 [1, 128] 之间的整数(或特定分数)。

第五步:优化选择→VCO频率优先(通常希望VCO运行在较高频率(但不超过最大值),因为更高的VCO频率能提供更精细的相位偏移分辨率(相位偏移步长 = 1/(8F_VCO) 或 1/(56F_VCO)))→参数最小化(在满足VCO频率目标的前提下,倾向于选择较小的M和D值,这有时有助于优化功耗和环路特性)→占空比与相位(检查该配置下能否实现所需的占空比和相位偏移(占空比和相位的可编程性与O和F_VCO有关))

l)MMCM引脚

1)CLKIN1/CLKIN2:主参考时钟输入/次选时钟输入。

2)CLKFBIN:反馈时钟输入。

3)CLKINSEL: 控制时钟输入选择多路复用器的信号,高电平 = CLKIN1,低电平 = CLKIN2。用于动态切换MMCM的参考时钟。

4)RST:异步复位信号。该信号是MMCM的异步复位信号。当此信号被释放后,MMCM将同步重新使能(即MMCM重新启用)。当输入时钟条件改变(例如频率)时,需要进行复位。

5)PWRDWN:用于关闭已实例化但未使用的MMCM以降低功耗。

6)DADDR[6:0]:动态重配置地址输入总线,提供动态重配置的地址。不使用时,所有位必须置零。

7)DI[15:0]:动态重配置数据输入总线,提供重配置数据。不使用时,所有位必须置零。参见DI[15:0]。

8)DWE:动态重配置写使能输入引脚,提供将DI数据写入DADDR地址的控制信号。不使用时,必须置为低电平。

9)DEN:动态重配置使能选通,提供访问动态重配置功能的控制信号。不使用动态重配置功能时,DEN必须置为低电平。

10)DCLK:DCLK信号是动态重配置端口的参考时钟。

11)PSCLK:相位偏移时钟。

12)PSEN:相位偏移使能。

13)PSINCDEC:相位偏移递增/递减控制。

14)CLKOUT[0:6]:用户可配置的时钟输出(0至6),可以是VCO相位输出的分频版本(用户可控),分频比从1(旁路)到128。在采用适当的反馈配置时,输出时钟彼此相位对齐(除非设置了相位偏移)且与输入时钟对齐。仅CLKOUT[0:3] 支持直接通过高性能时钟连接至BUFR/BUFIO。

15)CLKOUT[0:3]B:CLKOUT[0:3]的反相信号。

16)CLKFBOUT:专用的MMCM反馈输出。

17)CLKFBOUTB:CLKFBOUT的反相信号。

18)CLKINSTOPPED:状态引脚,指示输入时钟已停止。

19)CLKFBSTOPPED:状态引脚,指示反馈时钟已停止。

20)LOCKED:MMCM的输出信号,用于指示MMCM已在预定义的窗口内实现相位对齐,并在预定义的PPM范围内实现频率匹配。MMCM在上电后会自动锁定,无需额外复位。如果输入时钟停止或相位对齐被破坏(例如输入时钟相位偏移),LOCKED将变为无效。在LOCKED无效后,必须对MMCM进行复位。

21)DO[15:0]:动态重配置输出总线,在使用动态重配置时提供MMCM的数据输出。

22)DRDY:动态重配置就绪输出,为MMCM动态重配置功能的DEN信号提供响应。

23)PSDONE:相位偏移完成。

j)VCO与输出计数器的详细波形

O0计数器被编程为简单的2分频,并选择VCO的0°相位作为参考时钟。O1计数器同样被编程为2分频,但选择了VCO的180°相位。这种设置可用于生成DDR接口的时钟,其中参考时钟与数据跳变沿对齐。O2计数器被编程为3分频。O3输出的编程与O2相同,但其相位被设置为延迟一个VCO时钟周期。大于一个VCO周期的相位偏移也是可以实现的。如果MMCM/PLL被配置为提供特定的相位关系,而后输入频率发生改变,那么该相位关系也会随之改变,因为VCO频率变了,所以绝对的时间偏移量(皮秒级)会发生变化。

k)参考时钟切换

1)

MMCM和PLL的参考时钟可通过CLKINSEL引脚进行动态切换。该切换过程以异步方式进行。时钟切换后,MMCM/PLL很可能会失去锁定状态(LOCKED信号失效),并自动尝试锁定到新的时钟上。因此,一旦完成时钟切换,必须对MMCM/PLL进行复位。MMCM/PLL的时钟输入多路复用器由CLKINSEL信号直接控制,内部不包含同步逻辑。当CLKINSEL为高电平时,选择CLKIN1;为低电平时,选择CLKIN2。

l)用户模型

1)时钟网络去偏斜模型:MMCM的主要用途之一是进行时钟网络去偏斜。实现反馈存在一些限制。CLKFBOUT输出可用于提供反馈时钟信号。当MMCM同时驱动BUFG和BUFH时,只有同时用于反馈路径的那个时钟缓冲器会被去偏斜。基本限制是:输入到PFD(鉴频鉴相器)的两个频率必须相同。因此,必须满足以下关系:即fin/D = fFB = fVCO/M。例子:如果fin=166MHz,D为1,M为6,O为2,则VCO频率为996MHz,时钟输出频率为498MHz。由于反馈路径M为6,故PFD的两个输入频率均为166MHz。

2)MMCM内部反馈模型:当MMCM用作频率合成器或抖动滤波器,并且不要求MMCM输入时钟与输出时钟之间存在特定相位关系时,反馈可以在MMCM内部完成。这种配置能提升MMCM性能,因为反馈时钟不会经过由内核电源供电的模块,从而避免了该电源噪声的影响。当然,CLKIN信号和BUFG上引入的噪声仍然会存在。

3)零延迟缓冲器(Zero delay buffer):MMCM也可用于产生零延迟缓冲器时钟。零延迟缓冲器适用于需要将单个时钟信号扇出到多个目的地,且要求目的地之间低偏斜的应用场景。在此配置中,反馈信号被驱动到片外,并且PCB板上的反馈走线被设计为与连接到外部组件的走线相匹配。该配置假设在FPGA输入端和外部组件输入端的时钟边沿是对齐的。CLKIN和CLKFBIN的输入时钟缓冲器必须位于同一个I/O组中。在某些情况下,由于外部组件与FPGA反馈路径的负载电容不同(例如,外部组件输入电容为1-4 pF,而FPGA输入电容约为8pF),可能无法实现精确对齐。这会导致信号斜率差异,实质上就是偏斜。设计者需要注意这种效应以确保时序正确。

4)CMT和CMT的连接:通过CMT骨干网,使用CLKOUT0至CLKOUT3可以将MMCM和PLL级联 起来,以产生更大范围的时钟频率。当使用CMT骨干网时,中间不需要缓冲器。由于骨干网的延迟未被补偿,因此两个MMCM的输出时钟之间会存在相位偏移。频率范围限制仍然适用。第二个MMCM的输出时钟与输入时钟之间的相位关系是未定义的,并且由于骨干连接未被补偿,在两个MMCM之间会引入额外的相位偏移。

m)扩频时钟生成

1)扩频时钟生成SSCG旨在降低设备产生的电磁干扰EMI的频谱密度。制造商必须确保其设备发射的电磁能量水平不会干扰附近其他电子设备的运行。例如,当手机靠近视频显示器时,通话清晰度不应下降;同样,使用手机时也不应影响显示器的正常工作。

2)EMC法规旨在控制引起这些干扰的噪声或EMI。满足EMC要求的典型解决方案包括增加昂贵的屏蔽层、铁氧体磁珠、扼流圈。这些解决方案可能会使PCB布线复杂化,延长产品开发周期,从而对最终产品的成本产生不利影响。

3)SSCG将电磁能量分散到一个较宽的频带上,从而有效降低了在狭窄频率窗口内测量到的电场和磁场强度。通过对SSCG输出进行调制,任何单一频率上的峰值电磁能量得以降低。当SS_EN属性设置为TRUE时,MMCME2可以从标准的固定频率振荡器生成扩频时钟。在MMCME2内部,VCO频率与CLKFBOUT和CLKOUT[6:4,1,0]一起被调制。时钟输出CLKOUT[3:2]用于控制调制周期,不供一般使用。只要时钟频率调整得足够缓慢,扩频就不会影响MMCME2的周期抖动。

4)选择下扩频通常是考虑扩频时钟对时序分析影响的结果。当使用扩频时钟时,设计必须满足频率偏差范围内最高频率的时序要求。因此,如果一个100MHz时钟使用SS_MODE(CENTER_LOW)产生3%(±1.5%)的中心扩频,那么带有3%中心扩频的100MHz时钟在时序分析中必须作为101.5MHz时钟来验证。然而,如果SS_MODE(DOWN_HIGH)产生3%的下扩频,则输入频率是频率偏差范围内的最高频率。因此,对于一个带有3%下扩频的100MHz时钟,时序分析仍然会将其视为100MHz时钟进行分析。

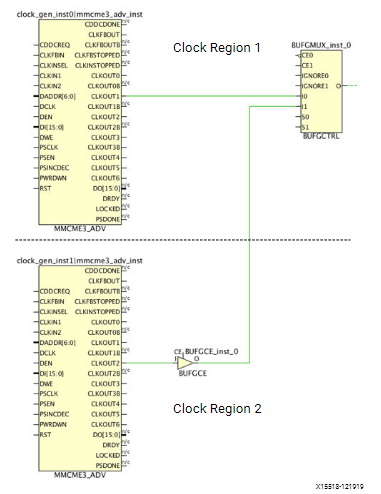

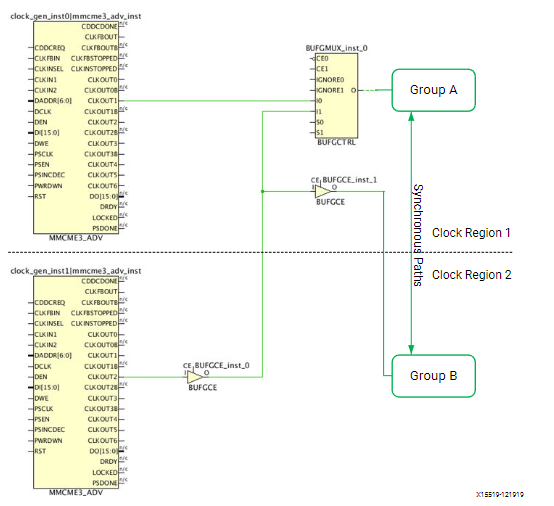

多时钟区域时钟

概述

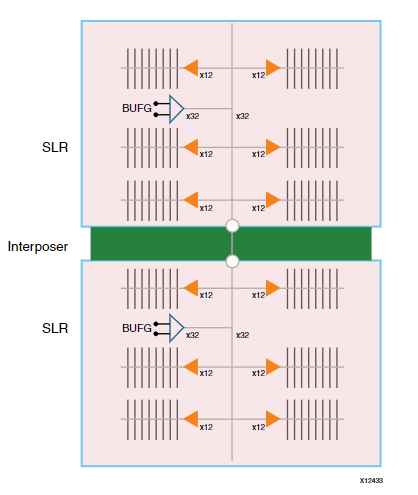

a)在7系列FPGA中,跨多个时钟区域的时钟与I/O互连逻辑的实现方式,与以往几代Xilinx FPGA有所不同。尽管单个时钟区域内的I/O和逻辑资源有所增加,降低了对时钟信号跨区域驱动的需求,但某些宽接口仍需驱动多个时钟区域内的互连逻辑与I/O逻辑。7系列FPGA提供的BUFMR/BUFMRCE原语,使得时钟输入引脚能够驱动其所在区域及其上方和下方区域内的BUFIO与BUFR。

跨越多个时钟区域的时钟设计

a)尽管单个时钟区域内的逻辑与I/O资源有所增加,减少了对跨区域时钟信号的需求,但某些设计仍需驱动来自同一时钟源的跨多区域互连逻辑(如切片触发器、BRAM、DSP)和I/O逻辑(如ISERDES、OSERDES、ILOGIC、OLOGIC、IDELAY、ODELAY)。为实现这一目标,必须使用BUFMR原语。

b)BUFMR

1)BUFMR(多区域时钟缓冲器)是一种允许时钟信号访问其输入器件所在区域上方和下方区域中BUFR和BUFIO的缓冲器。BUFMR的驱动范围可覆盖多个时钟区域。每个时钟区域设有两个BUFMR,它们驱动位于CMT列内的专用低偏移时钟资源,从而确保在将时钟信号驱动至多个区域时引入的偏移尽可能小。

2)每个BUFMR都能驱动同一区域及其正上方和正下方区域内的BUFR和BUFIO。BUFMR由同一时钟区域内的CCIO或GT输出驱动。这使得CCIO和GT输出时钟能够采用相同的电路拓扑跨越多区域。每个时钟区域的四个CCIO中,有两个可以驱动BUFMR。这些引脚标记MRCC,表示其具备多区域能力。另外两个无法驱动BUFMR的CCIO则标记为SRCC,表示单区域CCIO。

3)需要注意的是,在采用堆叠硅互连技术的器件上,BUFMR不能跨越超级逻辑区域之间的边界。

c)应用场景

1)当使用BUFMR驱动多个区域的逻辑时,建议将受多个BUFR或BUFIO驱动的逻辑划分为若干子集(最多三个),每个子集由独立的BUFR或BUFIO提供时钟。建议使用Vivado设计工具进行布局规划与约束,将逻辑分配到各个BUFR和BUFIO。

2)BUFR支持1到8的整数分频,分频值可通过设计中的BUFR_DIVIDE属性设定。同时,BUFR提供BYPASS设置,该设置会关闭分频功能,并禁用输出时钟使能CE以及分频逻辑的异步清零CLR。

3)跨时钟区域的时钟对齐:尽管使用BUFR_DIVIDE=BYPASS或BUFR_DIVIDE=1属性时,BUFR原语的行为相似,但使用 BUFR_DIVIDE=BYPASS时的BUFR延时小于使用BUFR_DIVIDE=1时。然而,使用BUFR_DIVIDE=1属性与使用BUFR_DIVIDE=2、3...8 时的BUFR延时是相同的。因此,当使用带分频功能的BUFR时,为获得跨时钟区域的最佳时钟对齐效果,不分频的BUFR应将其 BUFR_DIVIDE设置为1,而非BYPASS。

4)每个时钟区域使用单个缓冲器

①驱动多个BUFIO:当仅需跨三个时钟区域驱动I/O逻辑时,BUFMR可驱动三个BUFIO。BUFIO相比BUFR可提供更高性能的操作,并驱动I/O列内的专用时钟网络。建议将I/O逻辑按三个BUFIO分组为三个独立的子集,每个子集由其专用的BUFIO提供时钟。

②驱动多个BUFR:当需要从同一时钟源以相同时钟速率跨三个时钟区域驱动互连逻辑和I/O逻辑时,可使用BUFMRCE原语(带有时钟使能的多区域时钟缓冲器)。一个BUFMRCE可驱动三个BUFR,继而由这些BUFR驱动互连逻辑和I/O逻辑。建议将由三个BUFR提供时钟的逻辑划分为独立的子集,每个子集由其专用的BUFR驱动。如果使用了BUFR的分频功能,则必须在BUFMRCE被禁用期间复位所有BUFR实例。

5)每个时钟区域使用多个缓冲器

①驱动多个BUFR(带分频)和BUFIO:当驱动ISERDES/OSERDES的CLK和CLKDIV引脚时,需结合使用BUFIO与已启用分频功能的BUFR。BUFIO为ISERDES/OSERDES的CLK端口提供洁净、低偏移的时钟,而BUFR则为速度较慢的CLKDIV输入提供时钟。例如,当一个250MHz输入时钟通过MRCC引脚进入FPGA时,BUFIO以全速率250MHz驱动CLK输入,而设置BUFR_DIVIDE=2的BUFR则以半速率 125MHz驱动CLKDIV输入。

②驱动多个BUFR(带分频和不带分频):如果BUFIO不可用(被用于其他用途),ISERDES/OSERDES的CLK输入可由BUFR驱动。当一个BUFMR驱动超过三个BUFR时,需使用LOC约束手动放置这些BUFR。由BUFR驱动的逻辑会自动放置在合适的位置。

6)BUFR对齐:当使用BUFR的内置分频功能时,为了对齐多个时钟区域间的BUFR分频计数器,必须在BUFMR处停止时钟,并对BUFR施加复位信号。这需要使用BUFMRCE原语,该原语允许在复位期间禁用BUFMR的输出。要成功对齐相邻区域的BUFR,必须遵循以下步骤:将时钟使能连接到BUFMRCE的CE端口→将BUFMRCE的CE引脚保持在其无效状态,以禁用BUFMRCE的输出→通过向BUFR的CLR引脚施加复位信号来复位所有BUFR→在BUFR复位/CLR信号施加后,重新使能BUFMRCE→释放BUFR上的复位/CLR信号。所有BUFR必须在同一时钟周期内释放,以确保所有BUFR输出时钟的相位对齐。

7)多个BUFR的时钟输入都来自同一个BUFMR,而BUFMR又由同一个MRCC或GT时钟驱动,因此它们的时钟根源是同一个物理信号。此架构(BUFMR -> 多个BUFR)的设计初衷,正是为了在物理上跨越多个时钟区域的同时,逻辑上保持一个统一的、相位对齐的时钟域。这常用于超宽位宽(例如64位、128位)的源同步接口,其中数据和配套逻辑必须分布在多个区域,但需要由同一个时钟控制。如果所有 BUFR的分频比设置相同,并且执行了对齐操作(复位BUFR、同步使能BUFMR),那么所有BUFR的输出时钟将是相位对齐的。它们之间的偏移极小(仅由芯片内专用布线的微小差异引起)。在这种情况下,逻辑上位于不同子集(即不同时钟区域)的寄存器之间传输数据,属于同步逻辑。只要满足常规的建立和保持时间,无需使用异步FIFO、双寄存器同步器等跨时钟域处理技术。如果不执行BUFR对齐流程(即在BUFMR禁用时复位所有BUFR,再同步使能),各个BUFR的分频计数器可能起始于不同的相位。这时,它们的输出时钟虽然频率相同,但会有固定的相位差,实际上就变成了同频不同相的时钟域,这时在不同区域间传输数据就需要进行跨时钟域处理了。

时钟网络架构图

a)

1)物理结构与区域划分

①垂直列:时钟主干列位于最左侧,是全局时钟网络的物理支柱。BUFG和BUFH的输入级均在此列。它也是连接芯片上半部和下半部、不同超级逻辑区域的关键;CMT列包含一个CMT,负责所有时钟信号的生成、调制、分发;IO列包含一个完整的IO组以及对应的IO时钟缓冲器(BUFIO/BUFR)和时钟引脚(CC),这是外部时钟进入和高速数据进出的门户;GT列包含一个吉比特收发器四通道组,在V7器件中,此列与CMT列在垂直方向上对齐,使得GT时钟能直接低延迟地连接到CMT。

②水平行:BUFH和BUFG的网络通过HROW横向分发到该区域的所有时钟目标点。一个区域只有12条HROW轨道,因此最多只能有12个不同的全局/水平时钟在该区域同时活动。

2)核心时钟资源

①BUFG:物理上位于时钟主干列,但其驱动网络通过HROW覆盖整个区域。可以驱动区域内所有逻辑的时钟端口CLK以及控制端口(如CE, SR)。这是实现高扇出、芯片级控制信号(如软复位)的最高效资源。输入来源多样,包括同侧(上/下半部)的CC引脚、CMT、相邻BUFG、GT、BUFR。

②BUFH/BUFHCE:同样位于时钟主干列,但作用范围严格限定本区域及一个水平相邻区域。拥有独立的时钟使能,是实现区域级动态时钟门控以节省功耗的理想选择。与BUFG共享HROW的12条轨道。

③CMT:位于CMT列。MMCM是核心,PLL是其功能子集。可接受来自同区域CC引脚、BUFG、BUFH、BUFR、GT的直接连接。CLKOUT[0:3]有专用HPC路径直接驱动同区域的BUFIO和BUFR,这是实现超低抖动源同步接口的关键。CLKFBOUT等输出可驱动BUFG/BUFH,用于全局时钟去偏斜或频率合成。

④BUFMR:位于CMT列。专用作多区域I/O时钟分发。只能由本区域的MRCC引脚或GT时钟驱动。输出专门用于驱动本区域及紧邻的上下区域的BUFIO和BUFR,是实现宽位总线跨越多个Bank的核心。

⑤BUFIO&BUFR:位于I/O列,与I/OBank一一对应。BUFIO仅驱动本I/O Bank内的I/O逻辑(ILOGIC/OLOGIC、ISERDES/OSERDES)的时钟端口,是速度最快、抖动最小的I/O专用时钟。BUFR可驱动本时钟区域内的所有时钟目标(包括I/O逻辑和Fabric逻辑),具有可编程分频功能(1-8),是串并转换和区域时钟生成的理想选择。

⑥MRCC&SRCC:位于I/O列,共4对(8个引脚)。MRCC可驱动BUFMR(进而支持多区域),也可像SRCC一样直接驱动BUFIO、BUFR、CMT、同侧BUFG。SRCC只能驱动本区域内的BUFIO、BUFR、CMT、同侧BUFG。

3)专用互连与数据路径

①GT收发器时钟路径:这是Virtex-7的优势所在。GT Quad的恢复时钟(RXOUTCLK)、发送时钟(TXOUTCLK)、参考时钟可以专用地连接到相邻的CMT和BUFMR,延迟和抖动最小化。

②CMT、CC引脚、GT时钟可以驱动水平相邻(左侧)区域的BUFH和BUFG。这体现了时钟资源的横向可扩展性。

③从HROW出来的时钟,垂直向上和向下分布到所有CLB行、BRAM列、DSP列。每个BRAM和DSP切片都有独立的时钟端口(CLKA, CLKB, CLK),均可由该网络驱动。

4)无GT列

下面内容参考Xilinx UG899

IO和时钟规划概述

a)

1)I/O分配的合理性取决于FPGA的结构、PCB设计的需求,以及两者之间的交互关系。通过可视化FPGA与PCB之间的逻辑及物理交互,可优化信号在器件内部的数据流。I/O端口分配(定义PCB与FPGA设计的信号输入输出关系)与时钟资源分配(定义设计中时钟树结构)需协同推进,例如器件部分引脚更适配时钟功能,其他引脚则更适合DCI级联或VREF相关应用。

2)I/O规划可灵活启动于设计流程任一阶段,支持基于顶层端口列表、RTL设计、综合后网表开展工作,提供了灵活切入点。最佳实践是基于综合后设计进行I/O分配(仅综合后设计支持复杂I/O布局DRC检查)。

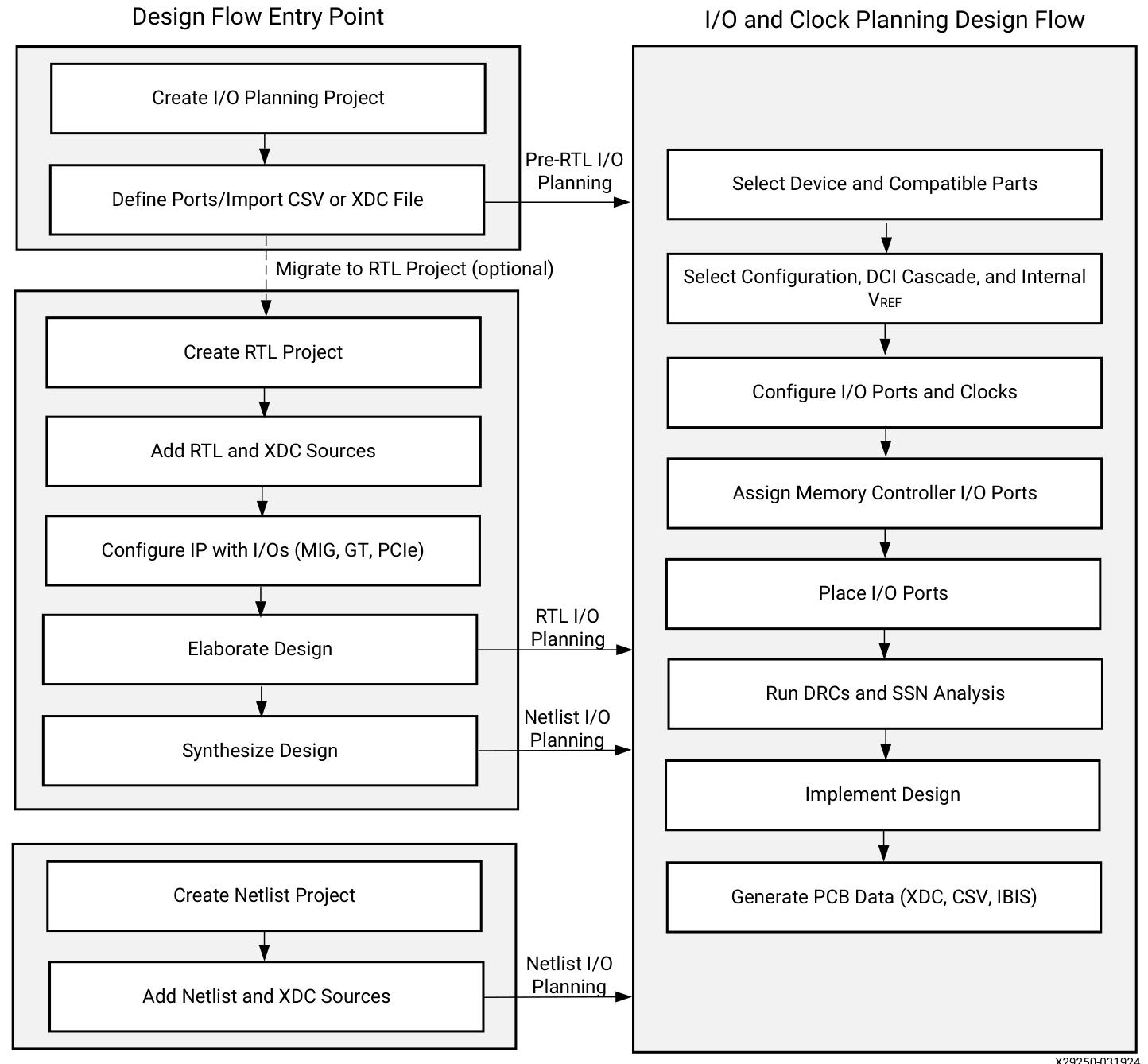

b)IO与时钟规划流程

1)RTL前IO规划

①设计源文件未就绪时,可创建空的I/O规划项目,开展早期I/O端口分配工作。此方法无需依赖RTL源文件或网表,仅聚焦初始I/O规划与板级集成。这能帮助PCB设计师与FPGA设计师提前锁定引脚分配方案,从根源上避免设计后期因引脚分配变更引发的迭代返工。

②通过I/O规划项目,可实现以下核心操作:i)导入PCB设计师提供的器件与I/O端口分配方案,或手动创建I/O端口;ii)导出器件与I/O端口分配方案,供PCB设计师使用或留存至设计后续阶段;iii)端口定义与引脚分配确定后,将I/O规划项目迁移为RTL项目;iv)基于端口定义,生成设计顶层的Verilog或VHDL模块定义。

③完成端口分配后,I/O规划项目可直接迁移为RTL项目,并同步生成顶层模块定义,使已确认的I/O规划方案成为RTL设计的基础。

2)RTL后IO规划

①精化后的设计会触发Vivado的DRCs,自动校验端口分配、I/O标准、时钟资源等关键设计细节。此时可同步推进初始I/O与时钟规划,导出的器件及I/O端口分配方案可直接用于PCB原理图符号绘制,约束信息也可保存为XDC文件,供后续综合或实现阶段调用。

3)网表IO规划

①网表I/O规划以综合后网表为基础,支持基于综合后的RTL设计或专门的综合后网表项目执行。AMD推荐优先采用综合后设计开展规划,因其能为工具提供更全面的设计信息,不仅支持自动I/O布局和交互式布局,精准管控端口分配,还可通过I/O规划视图直观查看器件封装物理引脚与I/O bank管芯焊盘的对应关系。

②基于综合后设计的规划,能帮助优化PCB与AMD器件的连接效率,提升与PCB设计师、系统级设计师的协同顺畅度,尤其便于整合 MIPI、内存IP等自带I/O布局要求的IP核的引脚方案。同时,综合后所有时钟(含生成时钟)均已明确,工具可更精准地识别时钟需求与资源占用,实现更深度的设计验证。

4)基于实现后的最终IO验证

①最终有效的I/O引脚分配和时钟配置,必须通过完全实现的设计进行验证。时钟资源的合规性验证,需以所有时钟的完整布线实现为前提。验证时可查阅实现报告中的I/O与时钟相关数据,且需与PCB设计师共同复核I/O端口分配,确保FPGA设计与系统级需求完全匹配。注意,I/O布局与位置选择受时钟布局及时钟所属半字节组的影响极大。

5)推荐建议:时钟逻辑验证优先采用综合后设计,时钟时序验证则需基于实现后设计开展。

c)IO与时钟规划设计流程步骤

1)项目设计流程可从空I/O规划项目、RTL设计项目、综合后网表项目切入,无论选择哪种类型,均需按以下8个步骤推进规划:

①选择器件及兼容器件:需根据最终设计的资源估算确定器件尺寸,结合PCB与存储器的关键布线等需求选择封装。Versal器件的专用硬内存控制器引脚不可用于其他I/O操作。除选定器件外,还可按替代兼容器件的要求指定替代兼容器件,也可选择集成AMD器件的目标设计平台板卡,这类板卡可提供评估或快速开发支持。

②选择配置模式、DCI级联、内部参考电压(INTERNAL_VREF):AMD器件上电后需配置,比特流通过专用配置引脚加载(Versal自适应SoC需加载器件镜像)。配置模式会影响I/O规划,需在I/O分配前确定,其不仅决定部分引脚连接方式,还影响含多功能引脚的I/O bank的VCCO电压。DCI可根据I/O标准控制驱动器输出阻抗或添加并联端接,通过每个I/O bank的两个多功能参考引脚实现对该bank I/O的阻抗控制。带差分输入缓冲器的单端I/O标准需VREF,可通过INTERNAL_VREF约束生成内部VREF,无需PCB提供参考电压轨,还能释放7系列和UltraScale中I/O bank的多功能VREF引脚。

③配置I/O及时钟:I/O端口支持IOSTANDARD、SLEW、DRIVE等约束,需按系统级设计要求配置,且I/O标准会影响引脚布局(部分标准可在同一I/O bank组合使用)。AMD器件划分为多个时钟区域,每个区域包含CLB、I/O bank等资源及时钟资源,I/O bank的时钟输入引脚可引入外部时钟并接入布线资源。需规划时钟资源分配。Versal高速I/O采用专用时钟,需确保配置正确。注:I/O规划项目不支持时钟规划,推荐使用MMCM/PLL模块定义时钟连接,或通过高级I/O向导结合I/O接口设计生成时钟。

④分配内存控制器I/O端口:内存IP通过预设计控制器和PHY实现FPGA与外部存储器件的接口,高速内存控制器、以太网IP、PCIe IP等受时钟和偏斜需求影响,有特定引脚分配要求。添加IP内核时,需在自定义阶段定义GT、PCIe、内存IP的I/O物理引脚分配,部分IP需重新自定义以修改I/O分配。UltraScale架构内存IP的I/O分配已集成到标准流程,无需自定义。

⑤布局I/O端口:支持多种交互式布局方式,在I/O端口窗口选择端口或接口组,分配至封装引脚或I/O焊盘。Versal器件的高级I/O规划器支持半字节级和银行级自动布局,可一次性优化所有I/O接口,也可让工具基于综合后设计信息自动布局I/O端口。

⑥运行DRCs与SSN分析:分配后需执行DRCs和SSN分析。DRCs按设计规则集验证设计并报告违规。SSN分析结合I/O bank电气特性,预估同时切换输出对其他端口的干扰,识别潜在噪声问题(不可作为最终签核依据)。推荐在综合后、实现前、实现后均运行两项分析,提前发现问题。

⑦实现设计:需先完成设计实现,再生成器件配置比特流。实现过程中,工具会将设计元素布局到器件资源、布线网络,并优化功耗与时序。

⑧生成PCB数据(XDC、CSV、IBIS):规划为迭代过程,需与PCB/系统设计师交互信息,可从PCB端导入CSV文件中的引脚分配。完成规划后,通过CSV文件和IBIS模型反馈引脚分配及器件模型,用于PCB端信号完整性分析。

配置器件

选择兼容器件

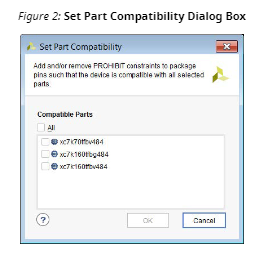

a)为应对设计过程中可能的器件调整需求,可为当前设计选定兼容的AMD器件,实现设计的跨器件重新定向。Vivado工具会自动筛选与目标器件封装一致的兼容器件,核心目的是最大限度保留已完成的I/O分配,确保替代器件无需重新调整引脚分配即可直接适配。

b)工具→I/O规划→设置器件兼容性

Vivado会自动识别所有选定替代器件的公共引脚,并为非公共引脚分配禁止约束。需注意:选择的替代器件数量越多,可用于布局的引脚数量可能越少。同时,Vivado会主动禁止将信号分配至选定替代器件的未绑定引脚,并弹出对话框提示被禁止的封装引脚总数。这些禁止约束可在封装窗口、封装引脚窗口、器件窗口中查看,被禁止的引脚统一以带斜杠的圆形图标标记。

选择器件配置模式

a)AMD器件的配置数据存储于CMOS锁存器中,这意味着器件每次上电后都需重新进行配置。比特流通过专用的模式配置引脚载入器件,这些引脚可适配多种配置模式。具体采用哪种模式,只需在专用输入引脚上设置对应的电压电平即可。

b)每种配置模式均对应一组接口引脚,这些引脚分布于器件的一个或多个I/O bank。其中,Bank0内置专用配置引脚,是所有配置接口的必备组成部分;UltraScal/UltraScale+器件的Bank65、7系列器件的Bank14/15,均搭载用于多种配置模式的多功能引脚。

c)勾选禁止将配置引脚用作用户I/O且配置后保持该状态,可锁定配置引脚功能,避免其在配置后被用作通用I/O,选中后保存设计会生成以下约束:set_property BITSTREAM.CONFIG.PERSIST YES [current_design]

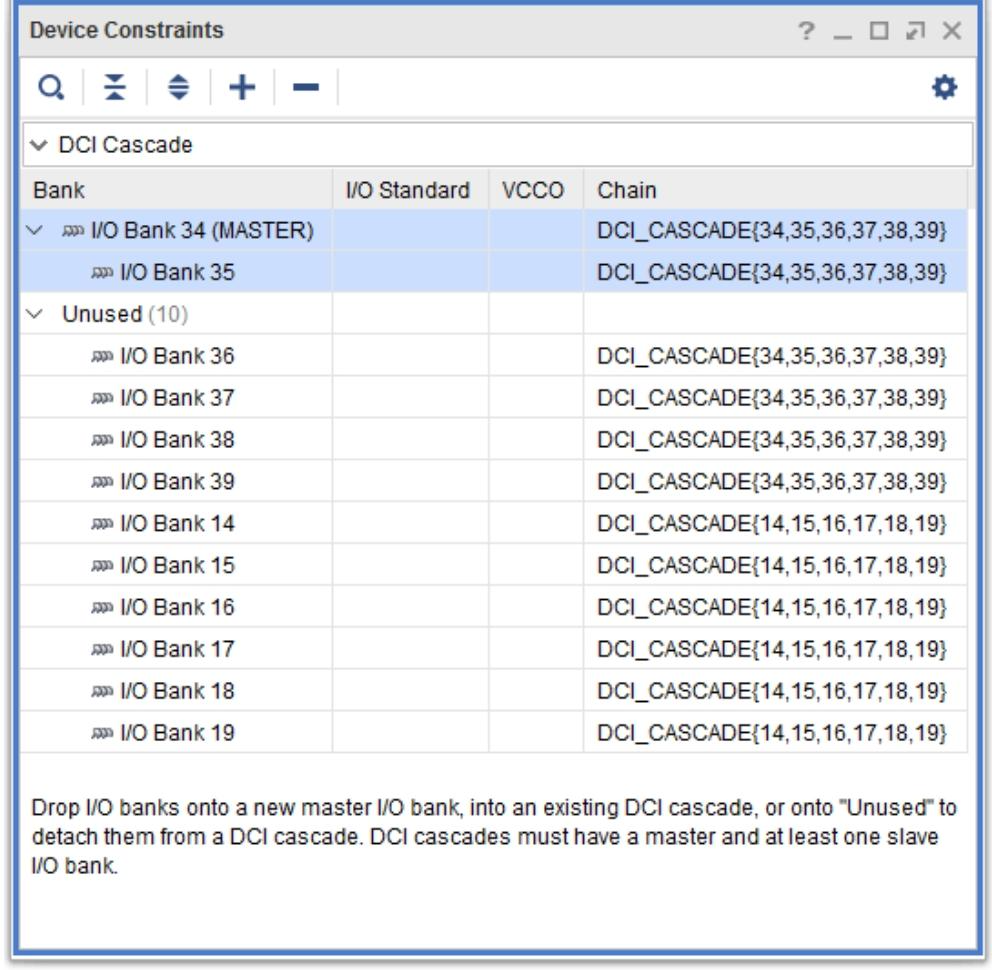

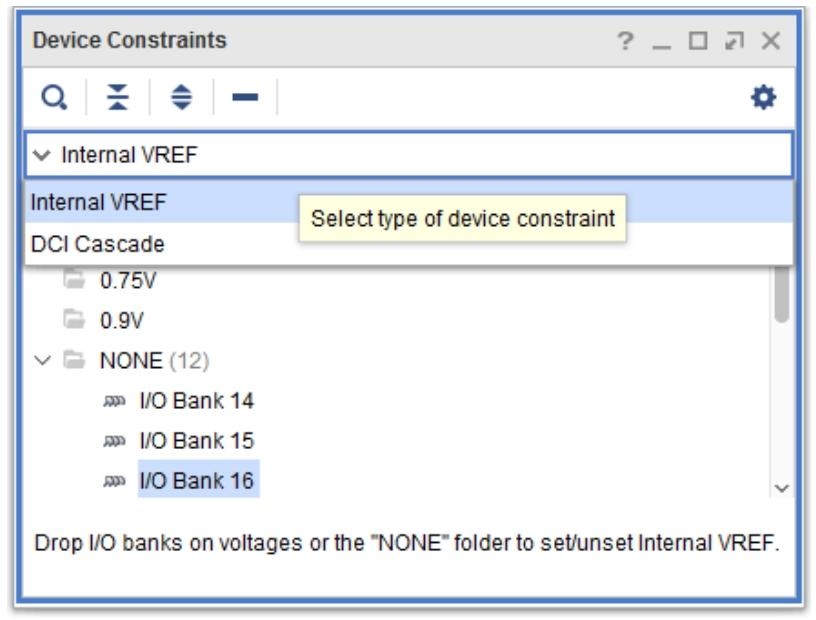

器件约束

a)器件约束窗口支持配置数字控制阻抗级联(DCI_CASCADE)和内部参考电压(INTERNAL_VREF)两类核心约束。AMD器件的 SelectIO接口驱动器与接收器具备可配置特性,可支持多种标准接口,核心功能包括可编程输出强度、转换速率调节、基于DCI的片上端接,以及内部参考电压INTERNAL_VREF生成。

b)根据I/O标准的不同,DCI可实现两大功能:①控制驱动器的输出阻抗,②在驱动器、接收器的一端或两端添加并联端接,最终实现与传输线特征阻抗的精准匹配。其工作原理是通过I/O bank中两个多功能参考引脚,结合VRN和VRP引脚上的外部精密参考电阻进行校准,动态调整bank内部阻抗,从而补偿工艺差异、温度变化、电源电压波动带来的I/O阻抗偏差。

c)带差分输入缓冲器的单端I/O标准需依赖参考电压VREF,供电输入方式因器件架构而异:UltraScale架构器件使用专用VREF引脚,7系列器件则使用两个多功能VREF引脚。此外也可通过INTERNAL_VREF约束生成内部VREF,这种方式无需在PCB上额外部署VREF供电轨,还能释放I/O bank中的多功能VREF引脚,用于其他I/O端口分配。需注意,每个I/O bank仅含一个VREF平面,INTERNAL_VREF约束需设置为整个bank统一的电压电平。

d)DCI_CASCADE约束

1)DCI_CASCADE约束的核心功能是将两个及以上相邻I/O bank进行级联,实现DCI参考电压的共享,从而优化信号完整性。级联关系中,提供DCI参考电压的I/O bank为主bank,其余参与级联的bank均为从bank,且所有bank必须位于器件的同一I/O列。约束tcl命令:set_property DCI_CASCADE {31 32} [get_iobanks 36]

e)INTERNAL_VREF约束

1)VREF作为参考电压输入。当Bank内的某些IO引脚被配置为特定的单端输入标准(如HSTL、SSTL、LVCMOS等需要参考电压的标准)时,该VREF引脚需要连接一个精确的直流电压。这个电压用于确定输入缓冲器的逻辑高/低阈值。当该Bank没有任何IO引脚需要使用参考电压标准时,这个VREF引脚可以作为普通用户IO使用。一个Bank的VREF引脚是整个Bank共享的。只要Bank内有任何一个IO使用了需要VREF的输入标准,该Bank的VREF引脚就必须连接到正确的参考电压,并且不能再作它用。

2)VREF电压的作用是为某些单端输入缓冲器提供一个可调的判决门限,以提高噪声容限、适配不同的接口电平,并减少信号摆动带来的功耗。主要用于像HSTL、SSTL这类伪差分或中心参考电压标准。例如,DDR内存接口(SSTL)就使用VREF。当输入信号电压>VREF+一个容差VIH 时,逻辑被判定为1;当输入信号电压<VREF-一个容差VIL)时,逻辑被判定为0。VREF通常设置在信号摆幅的中间点附近(例如,1.8V的SSTL,VREF典型值为0.9V)。

3)注意!VREF和SYSMON是功能独立物理分离的模块。SYSMON模块本身需要一个高精度、高稳定度的内部ADC参考电压源来确保其测量精度。这个参考源通常是内部产生的(例如1.25V),在较新器件中非常稳定。一些型号也支持连接外部更精确的参考源,这个外部参考源连接到名为VREFP/VREFN的专用引脚(注意:不是IO Bank的VREF引脚!)。

4)AMD器件支持通过启用INTERNAL_VREF约束,选择使用内部生成的参考电压VREF,核心优势在于无需在PCB上额外设计VREF供电轨,同时能释放I/O bank中的多功能VREF引脚,提升I/O端口资源的利用率。

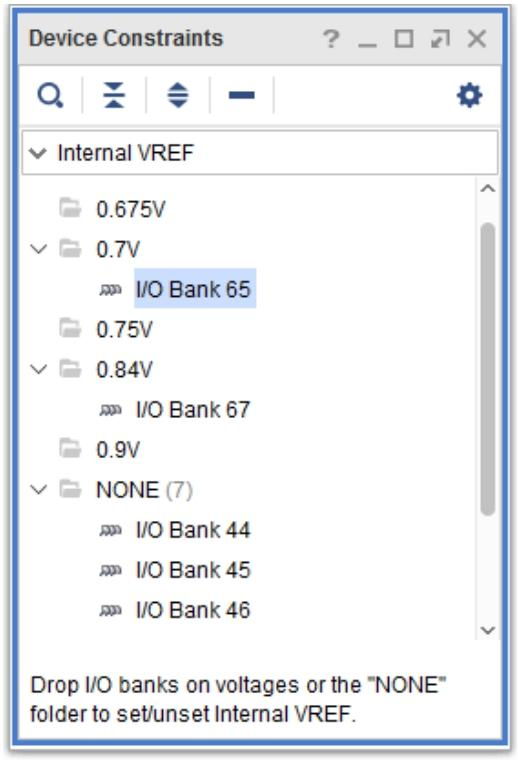

5)约束创建操作极为便捷:在器件约束窗口中,找到目标I/O bank,直接将其拖放至对应电压等级的文件夹(如0.7V、0.84V等),即可完成INTERNAL_VREF约束的创建。Tcl命令:set_property INTERNAL_VREF 0.7 [get_iobanks 65]

设置CFGBVS引脚

a)配置bank电压选择CFGBVS逻辑输入引脚的参考电压范围介于VCCO_0和GND之间。需将CFGBVS引脚设置为高电平或低电平,以确定 Bank0引脚支持的I/O电压。在Vivado中,可通过Tcl命令将CFGBVS的绑定为VCCO或GND,同时可将配置电压(即VCCO_0电压)设置为1.5V、1.8V、2.5V或3.3V。基于上述设置,工具会对不同架构器件的指定bank运行DRCs。7系列器件针对Bank0、14、15;UltraScale器件针对Bank0、65。这些电压设置也会在导出I/O缓冲器信息规范IBIS模型时被调用。

b)Tcl命令:set_property CFGBVS VCCO [current_design] // set_property CONFIG_VOLTAGE 3.3 [current_design]

c)默认情况下,CFGBVS属性为空。Vivado先检测CFGBVS属性是否设置为VCCO或GND,若该属性已赋值,则会进一步检查 CONFIG_MODE属性,并基于bank I/O标准(IOSTANDARD)和配置电压(CONFIG_VOLTAGE)设置执行DRC检查并报告违规。

d)导出CSV文件时,Vivado会根据CONFIG_MODE属性的设置,为相关bank提供VCCO信息:7系列器件对应Bank 0、14、15;UltraScale器件对应Bank0、65。例如,若使用JTAG/边界扫描模式,且CFGBVS设置为GND、CONFIG_VOLTAGE设置为 3.3V,工具会触发严重警告(DRC CFGBVS-4),提示CONFIG_VOLTAGE需改为VCCO对应的1.8V。特殊说明:UltraScale+™器件不支持手动设置CFGBVS或CONFIG_VOLTAGE,默认配置为CFGBVS=GND、CONFIG_VOLTAGE=1.8V。

IO逻辑和低速IO规划

a)对于已完成细化(Elaborated)、综合(Synthesized)、实现(Implemented)的设计,均可在Vivado中使用I/O规划视图布局。该布局主要包含器件窗口、封装窗口,同时,以下窗口会提供更多I/O相关信息:时钟资源窗口、时钟区域窗口、封装引脚窗口、I/O端口窗口、器件约束窗口、属性窗口。

b)针对新一代的Versa器件,Vivado引入了全新的高级I/O规划器工具,它允许以半字节和I/O组为粒度,进行更精细、更高效的I/O布局与调整。而对于低速I/O的规划,则继续采用经过验证的传统设计方法论。若需深入了解低速I/O引脚规划的架构细节与最佳实践,请参考《Versal Adaptive SoC SelectIO资源架构手册(AM010)》。

查看器件资源

a)通过以下任意一种方式进入该布局:

1)从主菜单栏选Layout→I/O Planning;

2)在IDE顶部的布局选择器中,直接点选I/O Planning;

3)通过新建项目向导,创建一个全新的I/O规划项目,该类型项目将默认启用此布局。

b)在 Vivado中,器件窗口和封装窗口直观地呈现了目标器件的物理布局以及设计中已放置的逻辑资源。在这两个窗口中选择任一逻辑对象或物理站点时,其详细的配置与状态信息会实时同步显示在属性窗口中。下文将对这些核心窗口进行详细说明。如需快速定位特定设计对象或器件站点,可利用编辑 → 查找功能。查找对话框支持按多种对象类型进行检索,并提供了灵活的过滤选项。定位后,可直接在查找结果窗口中进行选择,实现高效导航。

c)属性窗口

1)属性窗口是查看和编辑所选对象各项参数的核心面板。窗口标题会动态更新,以反映当前选中对象的类型(如I/O端口、逻辑单元等)。该窗口通常提供多个标签视图,以便从不同维度审视对象。例如,当选中一个I/O端口时,窗口可能会展示常规、属性、配置等视图,分别对应其基本定义、约束参数、具体配置选项。除图形界面外,也可通过Tcl命令快速查询引脚属性,这对自动化脚本编写很有帮助。例如:

report_property [get_package_pins <pin_number>] // report_property [get_package_pins <pin_number>]

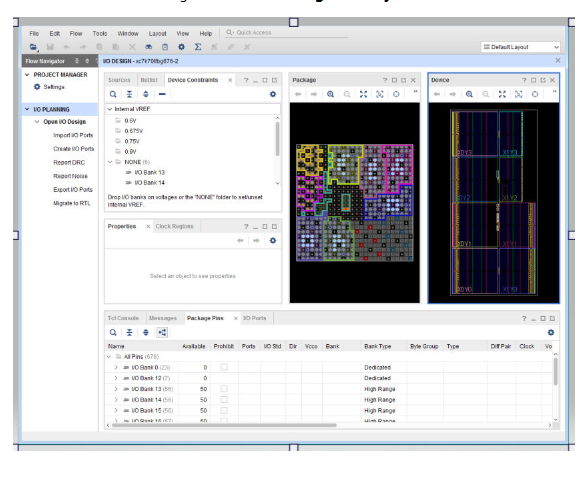

d)时钟区域窗口提供了便捷的时钟区域选择入口。在此窗口中选择特定时钟区域时,与其关联的I/O组和区域时钟资源会在封装窗口及器件窗口中同步高亮显示,如上图所示,形成了直观的视觉联动。一旦有时钟区域被选中并高亮,界面将激活时钟区域属性选项卡。通过该选项卡,可以深入查看所选时钟区域的详细属性:统计视图展示该时钟区域内的资源利用率统计数据,并列出该区域中包含的逻辑设计内容,帮助快速评估资源余量与分布;资源视图以列表形式清晰呈现该区域内所有可用的器件时钟资源(如BUFG、BUFR等),方便为设计中的时钟逻辑精确指定物理位置。

e)I/O组资源:在Vivado的I/O规划视图中,选择任意窗口(如器件、封装、封装引脚窗口)中的一个I/O组资源时,该资源会在所有其他相关窗口中同步高亮显示。这种视觉联动机制,清晰地揭示了物理封装引脚、I/O组边界、内部芯片焊盘之间的空间映射关系。

定义和配置IO引脚

a)导入IO端口

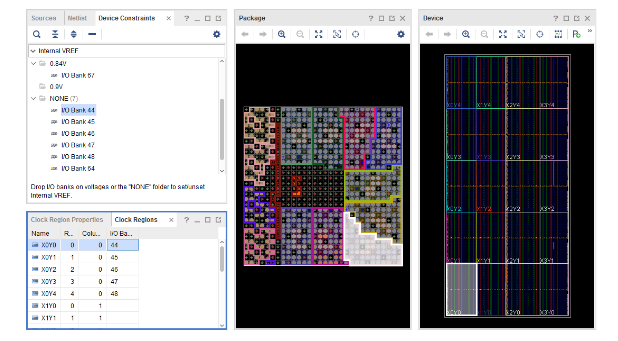

1)早期协同与规划(I/O规划项目):当设计处于早期概念阶段,RTL代码尚未就绪时,可以创建一个专门的I/O规划项目。在此类项目中,可以直接导入由PCB设计师提供的CSV文件,或包含初步约束的XDC文件,从而快速建立引脚规划的起点。这实现了与硬件团队的早期并行协作。CSV是一种在FPGA设计与PCB设计团队之间交换器件引脚信息和引脚分配方案的通用标准格式。为确保兼容性,Vivado要求导入的CSV文件遵循特定的格式规范。工具具备一定的智能推断能力。例如,当文件中仅列出了差分对的一端,或两个端口的命名符合某种成对惯例时,Vivado能够自动识别并尝试为其创建差分对。在这种情况下,系统会弹出对话框,请求您确认自动推断的配对关系。导入的CSV文件可以包含超出Vivado标准字段的额外信息列。这些非标准内容不会被忽略,而是会作为用户自定义列显示在封装引脚窗口中。可以通过右键菜单中的设置用户列值选项,查看、修改、利用这些自定义数据,这为团队间传递特定备注信息提供了灵活性。

2)基于现有设计推进(RTL项目):如果已经拥有部分或完整的RTL设计,则可以通过创建标准的RTL项目来开始I/O规划。项目创建后,I/O端口窗口将自动列出RTL源文件中定义的所有顶层端口。可以在此基础上,进一步添加 IP 核或进行配置。

3)从规划到实现的平滑过渡(项目迁移):当在I/O规划项目中完成了初步的引脚定义与分配后,可以将其迁移为一个完整的RTL项目。此过程会自动将规划好的端口列表转换为可用的Verilog或VHDL顶层模块文件,从而无缝地将规划成果转入详细设计阶段。

b)由于XDC文件格式本身不包含端口方向信息,因此导入后端口方向将处于未定义状态。需要后续手动为其指定方向。

c)AMD器件支持可配置的SelectIO接口驱动器和接收器,这些接口支持多种标准。这些标准接口包括可编程的输出强度、压摆率控制、使用DCI的片上终端、内部VREF的生成。可以配置一个或多个I/O端口以定义I/O标准、驱动强度、压摆率类型、上拉类型、输入终端。这对于配置从CSV或XDC文件导入但缺少相应特性的端口非常有用。将这些端口配置为支持系统级设计所需的标准。例如,可以在单个I/O组内组合使用某些I/O标准,但不能组合其他标准。

IO布局

a)在I/O规划视图布局 中,可以通过多种方式将I/O端口分配至物理封装引脚。操作的基本模式是:先在I/O端口窗口中选择目标(单个端口、端口组、接口),然后将其指定到封装窗口中的具体引脚或器件窗口中的I/O焊盘。

时钟规划

a)在时钟规划中,需要确定如何使用AMD器件上的各种时钟资源来将时钟分布到整个器件。AMD器件被细分为按列和行排列的时钟区域。一个时钟区域包含CLB、DSP、BRAM、互连、相关的时钟资源。时钟区域的大小和内容因器件类型而异。例如,在AMD UltraScale器件中,时钟区域横跨60个 CLB、24个DSP片、12个BRAM,其中心有一条水平时钟主干HCS。在7系列器件中,时钟区域横跨50个CLB、1个 I/O组(包含50个 I/O),其中心有一条水平时钟行HROW。

b)系统时钟或板级时钟是通过输入端口或千兆位收发器输出引脚进入设计的原始时钟。每个I/O组都包含时钟输入引脚,用于将系统时钟引入器件并接入时钟布线资源。与专用时钟缓冲器结合,这些时钟输入引脚将系统时钟引入:全局时钟线、同一I/O组及相邻I/O组内的I/O时钟线、同一时钟区域及垂直相邻时钟区域内的区域时钟线、CMT。

c)在处理综合后或已实现的设计时,可以使用时钟资源窗口手动放置全局和区域时钟相关逻辑,例如BUFGCTRL、MMCM、BUFR、IDELAYCTRL。也可以在器件窗口中手动放置时钟逻辑。AMD建议在选择引脚分配之前优先选择时钟资源。这是因为时钟资源的选择可能决定特定的引脚分配,并引导相关逻辑的布局。正确的时钟选择可以产生更优的结果。Vivado在实现过程中会自动处理时钟规划。然后可以使用交互式时钟规划来手动处理时钟问题。

验证IO和时钟规划

a)在完成I/O与时钟规划后,对其进行严格验证是确保设计最终成功的关键步骤。Vivado为此提供了两大核心验证手段:设计规则检查DRC和同步开关噪声SSN分析。前者用于检查设计是否符合一系列预设的物理与电气规则,后者则用于预估并优化由大量I/O同时开关所引起的噪声影响。完成这些前期验证后,还必须通过完整的设计实现并生成比特流,才能对最终的引脚分配与时钟配置进行终极的、基于实际布局布线的有效性确认。

DRCs

a)运行DRC是引脚规划中最关键的步骤之一。DRC会根据一组特定的设计规则来检查当前设计,并报告任何错误或违规情况。

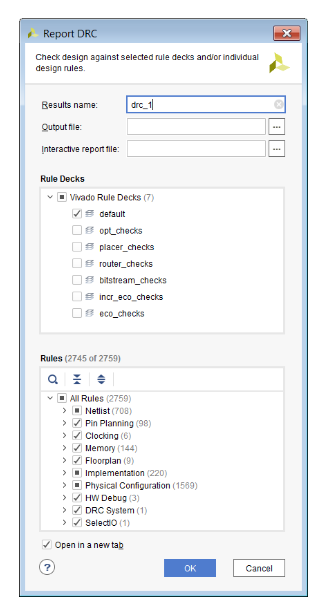

b)Rule decks指定要在设计上运行的规则套件。规则套件是为了方便而分组的设计规则集合。一条设计规则可以存在于多个规则套件中。例如,同一规则可以同时存在于opt_checks和placer_checks规则套件中。Vivado会在FPGA设计流程的相应阶段(例如综合后或实现后)运行规则套件:

1)default:运行AMD推荐的一组默认检查;

2)opt_checks:运行与逻辑优化相关的检查;

3)placer_checks:运行与布局相关的检查;

4)router_checks:运行与布线相关的检查;

5)bitstream_checks:运行与比特流生成相关的检查;

6)timing_checks:运行与时序约束相关的检查;

7)incr_eco_checks:检查增量工程变更单设计的修改有效性;

8)eco_checks:在完成修改网表的工程变更单ECO后,对连接性和布局运行检查。例如,当使用connect_net Tcl命令修改网表时,通常会在已实现的设计上运行此检查;

9)Rules:指定规则套件后,根据需要修改要运行的规则。

c)启用或禁用交互式DRC

1)在I/O规划期间,Vivado会运行基本检查以确保引脚分配的合法性。但是,完整的DRC签核仅在Vivado实现过程中运行。因此,需要将设计通过Vivado实现流程,以确保最终的引脚分配完全合法。

2)交互式I/O布局规则包括:

①禁止:放置到与GT相关的噪声敏感引脚上,或放置到可能产生噪声敏感的I/O封装引脚上;I/O标准违规。

②允许:不在不支持特定I/O标准的组中使用该标准;组没有分配不兼容的VCC端口;需要VREF端口的组有可用的VREF引脚;(仅在导入网表和XDC文件时)正确分配全局时钟和区域时钟;差分I/O端口被设置到正确的极性引脚;不会在仅支持输入的引脚上放置输出引脚。

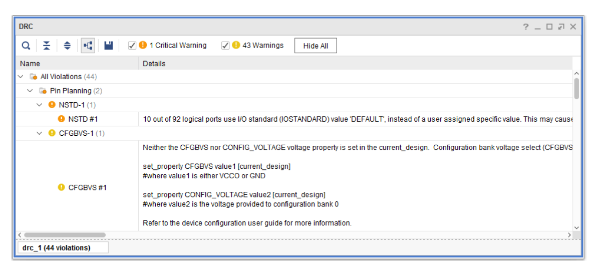

d)查看DRC违规

1)如果发现违规情况,DRC窗口将打开。DRC窗口根据Report DRC对话框中定义的各个规则类别对违规情况进行分组。同时违规情况还会按严重程度进行分类和颜色编码,以便快速审阅:

建议:提供设计处理的一般状态和反馈;

警告:指示由于约束或规范可能未按预期应用,设计结果可能未达到最优;

严重警告:指示某些用户输入或约束未被应用,或未遵循最佳实践。AMD强烈建议您检查这些问题并进行修改;

错误:指示导致设计结果无法使用的问题,未经您的干预无法解决。设计流程将停止。

e)除了使用预设规则,Vivado还支持通过Tcl脚本创建完全自定义的DRC规则。可以使用create_drc_check、create_drc_violation等Tcl命令,根据团队内部规范或特定项目需求,定义专属的设计检查规则。若想了解当前设计环境中所有已定义的DRC规则(包括内置规则和已加载的自定义规则),可以使用get_drc_checks这一Tcl命令来获取完整列表。

f)自Vivado 2016.1版本开始,一部分原先通过report_drc执行的检查,被分离出来并整合到了新的report_methodology命令中。这些检查主要涵盖与AMD UltraFast设计方法学 相关的约束合规性、逻辑映射合理性等更侧重设计方法论的内容。建议在设计首次完成综合后,以及每次约束条件、时钟结构、主要逻辑发生重大变更后,运行report_methodology命令。这有助于及早发现并修正那些不符合推荐设计流程的常见问题。

SSN

a)Vivado提供了对不同器件I/O相关的开关噪声水平的分析功能。SSN分析用于估计同一I/O组内多个输出端口同时开关时,对其他输出端口可能造成的干扰。该分析在预测中融入了特定I/O组的电气特性,以更好地模拟封装对SSN的影响。

b)I/O端口被划分到各自独立的I/O组中,每个I/O组都具有独特的电源分布网络,并对开关活动产生独特的响应。由于封装的FPGA内部电源分布网络对噪声的响应各不相同,因此理解设计中使用的I/O标准、I/O数量、器件电源系统对此开关活动的响应至关重要。

c)AMD通过三维提取和仿真对所有I/O组进行了特性表征,并将这些信息整合到SSN分析中。SSN分析利用器件的预期开关活动特性,来预测开关行为如何影响系统的电源网络,进而预测I/O组内其他输出端口会受到何种影响。SSN分析仅分析输出信号(包括双向端口的输出),在计算中忽略输入信号。只要I/O组留有足够的噪声裕量,输入和输出电平就不会受到影响。SSN分析是当前用于预测输出开关如何影响接口噪声裕量的最准确方法。其计算和结果基于一系列变量。这些估计旨在帮助您识别设计中潜在的噪声相关问题,而不作为最终的设计签核标准。

d)当SSN分析报告指出某个I/O组裕量不足时,可以采取以下一种或多种措施进行优化:

1)降低单端口噪声贡献:为问题组内的端口选择SSN影响更小的电气配置。例如:①降低驱动强度;②采用具有片上并行终端的DCI I/O标准;③换用驱动等级更低的标准(如SSTL Class I替代Class II)。

2)分散噪声源:①跨组分散:将问题引脚重新分配到多个不同的I/O组,避免大量高驱动端口集中在单一电源域内;②跨时域分散:利用时钟相位,将同步翻转的端口分配到不同的时钟相位上,使它们的开关时刻错开。

3)启用精确建模:为分析添加相位信息(见下文),以获得更真实(通常更乐观)的裕量评估,从而可能消除因保守假设而产生的虚假违规。默认的SSN分析采用最坏情况假设,即所有输出端口完全同步翻转,这可能导致结果过于悲观。相位分析功能则允许工具利用设计中真实的时钟关系,模拟输出在不同时刻翻转的效果,从而提供更精确的噪声估算。

与系统工程师的接口

a)I/O与时钟规划是一个需要迭代的协同过程。在此过程中,FPGA设计工程师需要与PCB设计工程师、系统架构师紧密协作,交换关键的物理接口信息。

b)在Vivado中完成初步或最终的引脚规划后,可以导出CSV文件(包含详细的引脚分配清单)和IBIS模型(用于信号完整性仿真),并将其提供给硬件团队。同样地,如果PCB布局或系统需求发生变化,硬件团队可能会提供更新的引脚需求。

生成IBIS模型

a)IBIS是一种国际通用的行为级建模标准,用于描述集成电路输入/输出缓冲器的电气特性。与SPICE等晶体管级结构模型不同,IBIS模型通过V/I曲线和时序数据来描述I/O行为,能够有效保护芯片设计的知识产权,同时满足系统级信号完整性分析的需求。对于FPGA器件,每个支持的I/O电平标准都有对应的IBIS缓冲器模型,而一个完整的IBIS文件则是所有这些模型的集合。该文件还包含一个引脚-模型映射表,将设计中实际使用的每个物理引脚与其配置的I/O标准所对应的IBIS模型精确关联起来。

b)IBIS格式文件包含标准化的文件头和组件描述段。其合规性可由IBIS开放论坛提供的Golden Parser工具进行验证,确保语法和语义符合规范。在Vivado中执行导出操作时,工具会生成一个扩展名为.ibs的文件。此文件整合了三大关键信息:设计中使用的引脚列表、这些引脚连接的内部信号名称、驱动/接收这些信号的I/O缓冲器的精确行为模型。

c)为了在PCB设计阶段进行精确的系统级信号完整性(SI)分析(如评估串扰、地弹、SSN),PCB工程师需要FPGA设计师提供对应的 IBIS模型。这些模型能精确表征FPGA封装引脚的电气行为。也可以直接从AMD官方网站下载与您器件型号匹配的通用IBIS模型,但通过Vivado基于您的具体设计生成的是包含您特定配置的定制化模型,通常更准确。

PCB设计协同

a)提前规划器件兼容性:在项目初期,即通过定义备选兼容器件功能,设定可能替换的器件型号。Vivado会自动对非共用的引脚施加禁止约束,这能从源头避免因更换器件型号而导致的引脚不兼容问题,为PCB布局提供稳定基础。

b)严格执行设计规则检查:务必在锁定引脚方案前,运行全面的DRC。这是检验当前I/O分配电气与物理合规性的基石,必须解决所有报出的警告和错误,才能进入下一阶段。

c)预先分析同步开关噪声:利用SSN分析功能,预估并优化由大量I/O同时开关引发的噪声风险。在板级布线前识别并缓解这些问题,能显著提升系统稳定性。分析时需结合器件对应的SelectIO和存储器资源手册(UG471/UG571/UG573/UG586),以理解具体的电气约束。

d)提供准确的仿真模型:通过生成IBIS模型功能,为PCB工程师提供用于信号完整性仿真的定制化IBIS文件,这是协同进行系统级SI/PI分析的必要条件。

e)获取精确的封装延时数据:Vivado提供的是封装引脚的迹线延迟数据,而非简单的物理长度,这是进行精确时序协同分析(如源同步接口)的最可靠依据。可通过导出CSV文件或使用write_csv Tcl命令获取。

f)导出清晰的引脚分配表:完成所有验证后,最终通过导出I/O引脚和封装数据功能,生成包含全部分配和约束信息的CSV文件,作为与PCB设计团队交接的权威文档。

下面内容参考Xilinx UG872

大型FPGA设计方法学概述

a)设计策略:系统级规划→设计创建→实现→分析;运用策略有助于在布线资源利用率、设计性能、功耗、项目成本上实现最佳效果。

b)

系统级设计

引脚布局

a)引脚布局选择的后果

1)不良引脚布局 → 布局不佳 → 路径延长 → 功耗增加,性能下降。

b)使用xilinx工具做引脚布局

c)通用引脚布局建议

1)总体而言,应选择使相关信号保持紧密布局、并更靠近其最终驱动负载的引脚方案。在进行板级布局调整或后期工程变更而优化引脚布局时,此细节极易被忽视。然而,创建并维持一个良好的引脚布局对于成功的FPGA设计至关重要,对于可能消耗超过1000个接口引脚的大型FPGA设计而言,更是如此。需要指出的是,在器件封装上位置接近的引脚,在器件内部阵列中未必相邻。就内部时序而言,引脚在阵列中的物理邻近性比在封装上的邻近性更为重要。

d)具体引脚布局选择建议

1)接口数据、地址、控制引脚:①应将同一接口的数据、地址、控制引脚集中布局在同一I/O组内;②若无法放置于同一组,则应该放置在相邻组内;③对于SSI器件,应将特定接口的所有引脚布局在同一超逻辑区域内。

2)接口控制信号:应将时钟、使能、复位、选通等接口控制信号,放置在其所控制的数据总线中央位置。

3)极高扇出、全设计范围的控制信号:①应将极高扇出、全设计范围的控制信号布局在器件中央区域;②对于SSI器件,应将这些信号置于其所驱动的多个超逻辑区域的中间那个超逻辑区域内。

4)包含I/O接口的赛灵思IP核:对于如存储器接口生成器等包含I/O接口的赛灵思IP核,应使用其工具生成接口并采用其推荐的引脚布局。

5)CCIO与CMT资源的使用:①应在器件的上下半部分之间平衡CCIO和CMT资源的使用,以平衡对上下半部分BUFG资源的访问;②对于SSI器件,应在一个超逻辑区域内平衡上下半部分的CCIO或CMT资源与其他超逻辑区域的需求。

6)位于特定超逻辑区域内的组件:①对于SSI器件,在为位于特定超逻辑区域的组件规划引脚布局时,应将其引脚布局在同一超逻辑区域。例如,若将器件DNA序列信息用于外部接口,则该接口的引脚应布局在存有DEVICE_DNA的主超逻辑区域内。

e)器件迁移

控制集

a)控制集概念

1)控制集是驱动特定RAM或寄存器的一组控制信号的集合。这些控制信号包括:置位/复位、时钟使能、时钟。每个独特的控制信号组合都会形成一个独特的控制集。由于一个切片内的寄存器共享相同的控制信号,只有具有相同控制集的寄存器才能被打包到同一个切片中。如果设计中存在多个独特的控制集,则可能导致:器件利用率低、布局选项减少。

b)复位

1)由同步代码推断出的设计元素可能不仅仅是查找表和寄存器,还可能包括许多其他元件。移位寄存器查找表、BRAM、查找表存储器、DSP48寄存器以及其他资源都可能由通用的同步代码推断而来。然而,复位方式的选择和使用会影响这些元件的推断结果,可能导致为特定设计使用非最优的资源。例如:①在存储器阵列上不恰当地使用复位,可能导致推断出数千个寄存器,而非单个BRAM组件;②在延迟线上不必要地描述复位,可能导致使用数百个寄存器,而非几个移位寄存器查找表;③在乘法器的输入或输出端描述异步复位,可能导致寄存器被放置在切片中,而非DSP块中。

2)限制复位信号的使用可带来的收益:限制复位网络扇出、减少布线复位信号所需的互连资源、简化复位路径的时序分析、提升性能并降低功耗。

3)定义推断出的同步单元的初始状态:GSR网络会依据HDL代码中的指定值初始化所有寄存器。若未提供初始值,综合工具可将其分配为0或1。初始状态通常默认为0,但存在少数例外(如独热码状态机编码)。任何推断出的SRL、存储器、其他同步单元,同样可以定义初始状态,该状态将在配置时编程到相应单元中。所有主流FPGA综合工具均可完全推断寄存器的初始状态。配置完成后,FPGA器件中的所有同步单元均以已知值启动。

4)有效极性:为实现最佳的布线和布局灵活性,请勿混合使用高扇出控制信号(如时钟使能、复位)的极性。赛灵思推荐使用高有效复位。高有效信号通常能以更少的逻辑和更少的逻辑层级映射到FPGA架构中。保持极性一致在整个设计中至关重要。混合极性会产生混合控制集,从而对布局和布线产生负面影响,在最坏情况下可能导致时序问题或器件适配失败。在Virtex-6和Virtex-7器件的切片及内部逻辑中,所有时钟使能和复位本质上都是高有效的。描述低有效复位或时钟使能,将导致额外的查找表被用作这些路径上的简单反相器。

c)HDL代码风格

1)优秀的代码风格具有优势:综合工具更轻松、仿真和综合更快速、在不同FPGA架构具有更好的移植性、能高效映射到目标架构、易于阅读和调试。

2)优秀代码风格的途径:采用能够高效推断映射到器件资源的HDL结构、仔细思考逻辑设计/时钟方案/控制信号、层次化决策、谨慎使用综合属性。

3)大于4位的加法、减法、加减混合运算:通常使用进位链实现,同时每2位加法需要1个查找表。例如:一个8位与8位的加法器将使用8个查找表及相应的进位链。对于三操作数加法,每3位加法使用1个查找表。一8 位、8位、8位的三数加法器同样使用8个查找表及进位链。若需进行多次加法运算,在每两级加法后插入寄存器可能更为有利。这可通过生成三操作数加法实现,从而将器件利用率降低一半。

4)乘法运算:通常映射到DSP模块中。有符号乘法,位宽小于18×25时,可映射到单个DSP模块。无符号乘法,位宽小于17×24时,可映射到单个DSP模块。需要更大乘积的乘法可能映射到多个DSP模块。为推断到DSP模块中的逻辑进行适当的流水线设计能极大提升性能和降低功耗。描述乘法运算时,在其周围设计三级流水线能获得最佳的时钟频率、建立时间、时钟输出时间、功耗特性。流水线过浅(一级或无)可能导致这些模块出现时序问题并增加功耗。

5)移位寄存器或延迟线:无需复位或多个抽头的移位寄存器或延迟线通常映射到移位寄存器查找表组件中。单个查找表可实现:两个深度 ≤16位的SRL,单个深度≤32位的SRL。为最优利用SRL,需仔细考虑这些模块的复位设置。若复位非必需,则可能获得更好的器件利用率、性能及功耗。

6)深度不超过64位的存储器阵列:描述深度不超过64位的存储器阵列通常使用LUTRAM实现。深度≤32位时,每个查找表映射2位。深度≤64位时,可做到每个查找表映射1位。更深的RAM也可用LUTRAM实现,具体取决于可用资源及综合工具设置。此类模块编码风格的微小偏差可能导致使用错误的资源。例如,异步写入或导致阵列值改变的复位编码,可能使其由寄存器阵列实现,而非LUTRAM。

7)深度超过256位的存储器阵列:深度超过256位的存储器阵列通常使用块存储器实现。此类模块编码风格的微小偏差同样可能导致使用错误的资源。例如,异步读取或导致阵列复位的编码,可能使其由寄存器阵列而非LUTRAM或块存储器实现。

8)4选1使用单个查找表;8选1使用2个查找表+1个MUXF7;16选1使用4个查找表+MUFX7和MUXF8资源组合。逻辑层次均为1级。

9)设计层次结构指导原则:在数据路径的输出端进行寄存器、将时钟元件置于靠近顶层的位置、采用推断方式实现IO元件。在数据路径的输出端进行寄存,始终将关键路径约束在模块内部或模块之间的边界上,避免了路径可能跨越多个层次的情况。

时钟

时钟资源选择

a)赛灵思建议将时钟资源选择作为设计的第一步,并应远早于引脚布局选择。时钟方案选择会决定特定的引脚布局,并能引导相关逻辑的布局。恰当的时钟资源选择可带来更优的结果。

全局时钟

a)BUFG组件易于由综合工具推断,且限制较少,适用于大多数通用时钟场景。如果时钟需求超出了BUFG的能力范围,或者希望获得更好的时钟特性,赛灵思建议:根据可用的时钟输入资源,仔细分析时钟需求。

b)全局时钟缓冲器包括

1)BUFGCE:具有同步、无毛刺的时钟使能(门控)功能,无需额外逻辑或资源。

2)BUFGMUX:用于在不同时钟源之间实现无毛刺、无时序风险的切换,可为不同运行阶段或条件生成不同频率的时钟。

3)BUFGCTRL:提供对全局时钟网络全部功能的访问,适用于更复杂的时钟场景(如时钟丢失或切换电路)。

4)IP与综合:部分IP(如存储器接口生成器MIG)会使用特殊时钟缓冲器以实现高速I/O的数据收发。在规划时钟架构时,必须考虑这些IP所使用的时钟资源。

区域时钟

a)主要的缓冲器包括

1) 水平时钟区域缓冲器(BUFH / BUFHCE):可与BUFG配合使用,也可作为独立缓冲器。BUFHCE提供与BUFGCE相同的无毛刺时钟使能,适用于对单个时钟区域进行简单、安全的时钟门控。作为BUFG的补充,对可约束在单个时钟区域内的较小时钟域提供低偏斜资源。独立使用时,BUFH驱动的所有负载必须位于同一时钟区域内。

2)区域时钟缓冲器(BUFR):通常用作低速I/O和逻辑阵列的时钟,用于捕获和提供高速I/O数据。支持时钟使能(门控)和常见的分频时钟生成。其性能通常低于BUFG和BUFH,不推荐用于超高速时钟,但非常适合中低速时钟需求。内置时钟分频功能使其特别适用于来自外部高速I/O接口时钟的分频时钟网络。

3)IO时钟缓冲器(BUFIO):将I/O数据捕获到输入逻辑中。为设备的输出逻辑提供输出时钟。在Bank内捕获高速源同步数据。与BUFR及ISERDES/OSERDES逻辑配合使用时,可将数据速率降低至更易管理的速度。BUFIO只能驱动其所在I/O Bank内的输入/输出组件(如IDDR、ODDR、ISERDES、OSERDES、专用的输入/输出寄存器)。

控制时钟相位、频率、占空比、抖动

a)使用CMT

1)MMCM的最常见用途是消除时钟的插入延迟(即将时钟相位与输入的系统同步数据对齐)。此外MMCM还可用于:精确相位控制、滤除时钟抖动、合成时钟频率、校正或调整时钟占空比。

2)如果仅需微调相位,可以使用IDELAY或ODELAY,而无需动用MMCM和PLL。

b)使用门控时钟

①避免在代码中直接描述时钟门控逻辑:当代码专门针对FPGA设计时,不应在时钟路径中编写时钟门控结构。相反,应通过编码技术来推断时钟使能,以此实现基于功能或功耗考虑的部分电路停止运行。

②代码转换:如果代码已包含时钟门控结构,或代码原本针对其他需要此类编码风格的技术,则应使用能够将时钟路径中的门控逻辑重映射到数据路径时钟使能的综合工具。这样可以更好地映射到时钟资源,并简化电路进出门控域的时序分析。

③若需要长时间关闭较大范围的时钟网络,可使用以下组件来启用或禁用时钟:BUFGCE、BUFHCE、BUFR、BUFMRCE。

④降低时钟频率:若需在特定时段降低时钟速度,除了使用上述组件配合额外逻辑来周期性启用时钟网络外,也可使用BUFGMUX将时钟源从高速时钟切换到低速时钟。

c)降低动态功耗

1)BUFR:外部生成、低于200MHz、需驱动最多三个垂直相邻时钟区域;

2)BUFMRCE:在V7中需用于超过一个时钟区域,垂直最多三个时钟区域;

3)BUFHCE:可约束在单个时钟区域内的高速时钟;

4)BUFGCE:可跨越整个设备,最灵活,但非功耗最优选择。

时钟输出

a)使用ODDR组件是一种将时钟从FPGA器件中转发出去、以供外部器件使用的有效方法。要生成一个在相位关系和占空比方面都得到良好控制的时钟:将其一个输入置为高电平;将另一个输入置为低电平。还可以利用其置位/复位和时钟使能端,来停止时钟并将其极性保持在一定状态。

b)如果需要对外部时钟进行更精确的相位控制,可以结合使用MMCM或PLL,并采用以下一种或两种方式:外部反馈补偿、相位补偿(可以是粗调或细调,固定或可变)。

跨时钟域

a)由于工艺、电压、温度的变化,数据在两个不同时钟域之间传递时,其时钟和相位的不确定性要高于在单一时钟域内传递。这种跨时钟域的切换会增加建立时间和保持时间计算的复杂度,即使在较低速的设计中也可能使时序收敛变得更加困难。

b)同步时钟域交叉

1)当时钟之间存在已知的相位关系,并且该关系在不同实现运行中保持不变时,我们称其为同步时钟域。这种情况通常发生在以下场景:两个时钟域彼此衍生、由同一个内部或外部时钟源提供,或两者兼有。在此类情况下,我们可以分析数据路径,并在考虑某些因素后,安全地将数据从一个时钟域传输到另一个时钟域。

2)时钟偏斜:根据到达源寄存器和目的寄存器的时钟路径在缓冲器中的公共节点和传输距离,时钟偏斜的计算可能非常显著。对于小的数据路径(例如寄存器到寄存器路径),时钟偏斜可能长于数据延迟。如果处理不当,则可能导致保持时间违规。如果路径中存在多个逻辑层级,额外的偏斜会使时序收敛更加困难。赛灵思建议,在此类跨时钟域路径中,需密切关注逻辑层级数,并充分考虑逻辑层级过少或过多所带来的影响。

3)同步时钟域交叉例子:①从同一个MMCM、PLL或器件引脚驱动、且位于芯片同一半区的两个BUFG网络之间;②水平相邻放置的两个BUFH网络之间;③由同一个BUFMR驱动、且配置相似的两个BUFR之间(如果BUFR不处于旁路模式,则必须通过同步所有相关BUFR的复位来确保它们相位对齐);④在同一时钟区域内,来自同一时钟源的BUFIO与BUFR之间。

c)异步时钟域交叉

1)对于异步时钟域交叉,必须采取特殊措施来降低可能影响设计数据完整性的各种因素,包括不正确的总线数据捕获和亚稳态问题。

2)有两种主要方法可以确保数据安全地跨越异步时钟域:①单比特/格雷码同步:可通过插入寄存器同步器来降低电路的平均故障间隔时间MTBF;②多比特数据总线:对于多位数据(即总线)传输,应使用一个独立时钟的异步FIFO来完成跨时钟域的数据传递。

4)异步时钟域交叉例子:①在两个不存在任何已知相位关系的时钟网络之间进行数据传输;②在使用MMCM/PLL的时钟网络与未使用MMCM/PLL的时钟网络之间进行数据传输;③在BUFH网络与任何其他时钟网络之间进行数据传输(除了与其水平相邻的BUFH网络);④在未由专用时钟资源(如外部时钟引脚、MMCM或PLL)直接驱动的时钟网络与其他时钟网络之间进行数据传输;⑤在位于器件上半区的BUFG与位于下半区的BUFG之间进行数据传输。

控制与同步设备启动

a)FPGA器件完成配置后,将退出配置状态,进入正常工作模式。在大多数配置序列中,最后的步骤包括:撤销全局置位/复位GSR信号后,撤销全局写使能GWE信号。在撤销GWE时刻,设计处于已知的初始状态,并释放运行。

b)未知状态风险:如果GWE的撤销释放点未能与特定时钟域同步,或者时钟运行速度快于GWE能够安全撤销的时序,设计的某些部分可能会进入未知状态。对于一些设计,进入未知状态无足轻重;但对于另一些设计,进入未知状态可能导致系统运行不稳定或对初始数据集处理错误。当设计必须从一个已知状态启动时,必须对启动同步过程进行控制。

c)如果设计只有一个时钟域,可以将配置后序列与系统时钟同步,从而实现相对于设计的同步释放。实现方法:例化STARTUP原语→将系统时钟连接到其CLK引脚。这种配置序列能够由该公共时钟驱动,从而简化设备启动的同步过程。

d)在其他多时钟域情况下,可以在GWE有效后,延迟所有设计时钟一段时间。实现方法:例化以下带使能端的时钟缓冲器,如BUFGCE、BUFHCE、BUFR→利用这些缓冲器的使能信号,在配置完成后延迟若干个时钟周期再开启时钟。对于MMCM,应对其输出时钟进行此类延迟控制,但切勿对反馈时钟实施延迟。

时钟缓冲器用于非时钟网络中

a)时钟缓冲器能够提供均匀、低偏斜的信号,非常适合时钟分配。当全局时钟需求已满足,仍有闲置的时钟缓冲器时,它们可以作为额外的布线资源,用于驱动高扇出信号。

b)当选择时钟缓冲器驱动非时钟信号时,需考虑以下关键因素:

1)设计性能考量:BUFG的设计目标是实现低偏斜,而非追求最短的传播延迟。根据目标时钟频率和时序路径的特性,在某些情况下,使用BUFG可能反而导致设计无法满足时序要求。

2)使用数量限制:当使用BUFG驱动非时钟信号时,信号在某些节点必须离开全局时钟网络才能到达最终目的地。如果在一个单独的引出点上,只有一个或两个BUFG需要离开全局时钟网络,则不会产生路径冲突,设计在任何情况下都能可靠布线。如果三个或更多BUFG需要到达同一位置,则可能出现资源冲突,导致设计无法完成布线。

建议:对于非时钟信号,最多使用两个BUFG。这样可以完全避免布线冲突。此限制同样适用于:在同一时钟区域内,使用两个BUFH驱动非时钟信号;BUFH与BUFG的组合需要驱动同一时钟区域内的相同逻辑。

c)避免使用BUFG驱动以下类型的信号:混合极性信号(部分为高有效,部分为低有效)、需要为网络的大部分额外添加逻辑(如反相器)的信号。示例:一个高扇出复位信号,在设计中部分为高有效,部分为低有效。此时插入BUFG可能对低有效部分无益,甚至有害,因为低有效部分仍需要一个LUT或其他逻辑来完成反相。

d)使能端的高效使用

1)使用BUFHCE时,为加快传播延迟,可以:将其输入端接逻辑1;使用使能端来改变网络的电平值。为实现此操作,必须:将CE_TYPE属性设置为ASYNC(异步)、将INIT_OUT属性设置为0。

2)若想在该路径中无成本地实现反相功能,可以:将输入端接地;将INIT_OUT属性设置为1。

3)使用BUFGMUX也可实现相同目标:当CLK_SEL_TYPE 设置为ASYNC,且在其输入端放置固定电平时,可通过其选择S引脚进行控制。

e)缓冲器类型选择

1)选择合适的缓冲器类型可以控制逻辑分组和布局,从而带来积极影响。使用BUFH或BUFR会将所驱动的元件限制在单个时钟区域内。这种限制能够促使布局更优化,有助于满足设计中紧约束部分的时序要求。在某些情况下,特别是对于高速路径,可能需要手动指定缓冲器的位置,以达到预期效果。

时钟资源选择总结

a)BUFG适用场景:

1)需要向整个器件的多个时钟区域提供高扇出时钟时;

2)不希望手动例化或控制时钟结构时(由工具自动推断);

3)驱动极高扇出的非时钟网络,例如用于中低速时钟的全局复位信号(前提是网络中不存在混合极性信号)。赛灵思建议,在任何设计中,此类用途最多仅限于两个BUFG;

4)SSI器件特别提示:对于时钟必须跨越多个SLR的设计,将其置于中心的SLR中。这可以使时钟网络在整个器件中分布更均匀,从而最小化时钟偏斜。

b)BUFGCE适用场景:

1)用于暂停一个扇出大、跨越多个时钟区域的时钟域。

c)BUFGMUX和BUFGCTRL适用场景:

1)用于切换时钟频率或更改时钟源。

d)BUFH适用场景:

1)适用于可以约束在单个时钟区域内的较小逻辑时钟域;

2)适用于极高速的时钟域;

3)适用于那些不太可能与BUFG组件竞争时钟资源的时钟域;

4)SSI器件特别提示:在SSI器件中,可在上部或下部的SLR组件中使用BUFH,这有助于减少其与放置在中心SLR中的BUFG组件之间的资源竞争。

e)BUFHCE适用场景:

1)用于暂停可以放置在单个时钟区域内的、中等规模的时钟网络部分;

2)用于驱动可以约束在单个时钟区域内的高扇出非时钟信号(例如复位信号)。

f)BUFR适用场景:

1)适用于性能要求不高于200MHz的中小型时钟网络;

2)适用于由外部提供、可以约束在最多三个垂直相邻时钟区域内且需要时钟分频的时钟;

3)SSI器件特别提示:在SSI器件中,在顶部或底部的SLR组件中使用BUFR,这有助于减少其与放置在中心SLR组件中的BUFG组件之间的资源竞争。

g)BUFIO(I/O时钟缓冲器)适用场景:

1)通常用于外部提供的高速I/O时钟,特别是在源同步数据采集场景中。

h)BUFMR(多区域时钟缓冲器)适用场景:

1)仅适用于Xilinx 7系列FPGA器件。当需要为单个时钟源在多个垂直相邻的时钟区域中使用BUFR或BUFIO组件时;

2)SSI器件特别提示:对于SSI器件,将BUFMR及其相关引脚置于SLR的中心时钟区域。这样在需要时,BUFMR可以访问全部三个时钟区域。

i)BUFMRCE(带时钟使能的多区域时钟缓冲器)适用场景:

1)仅适用于Xilinx 7系列FPGA器件。当需要为单个时钟源在多个垂直相邻时钟区域中使用BUFR或BUFIO组件,且需要周期性地暂停该时钟时;

2)如果使用了多个进行时钟分频的BUFR,可使用BUFMRCE来确保所有相连BUFR组件启动时的相位正确性。

j)MMCM(混合模式时钟管理器)适用场景:

1)用于系统同步输入/输出时,以消除时钟插入延迟(将时钟与输入数据相位对齐);

2)用于源同步数据采集时的时钟相位控制,以将数据与时钟对齐;

3)用于改变输入时钟的频率或占空比;

4)用于滤除时钟抖动。

k)PLL(锁相环)适用场景:

1)用于高速输入时钟的相位对齐。

l)IDELAY 与 IODELAY(输入/输入输出延迟单元)适用场景:

1)在输入时钟上使用,以添加少量的额外相位偏移(延迟);

2)在输入数据上使用,以为数据添加额外延迟,这实际上是相对于时钟减少了数据的相位偏移。

m)ODDR(输出双数据速率寄存器)适用场景:

1)用于从器件内部生成一个供外部使用的前向时钟。

下面内容参考Xilinx UG949

时钟指南

Ultrascale器件时钟

a)UltraScale器件的时钟架构与先前器件架构有所不同,它模糊了全局时钟与区域时钟之间的界限。UltraScale器件不再像7系列器件那样配备独立的区域时钟缓冲器,而是采用统一的缓冲器与时钟路由结构,无论负载是本地/区域性的还是全局性的。UltraScale器件具有更小且固定尺寸的时钟区域,这些时钟区域在水平方向上不再横跨半个器件宽度。每一行中时钟区域的数量因UltraScale器件的不同而有所差异。每个时钟区域包含一个时钟网络路由结构,该结构划分为24条垂直与水平路由轨道以及24条垂直与水平分布轨道。

b)主要时钟类型及相关时钟结构

1)高速IO时钟:此类时钟与高速SelectIO接口位片逻辑相关联,由PLL生成,并通过专用的低抖动资源路由至位片逻辑,以支持高速I/O接口。通常,这类时钟结构由AMD IP(如存储器IP或高速SelectIO向导)创建和控制,用户无需手动指定。

2)通用时钟:此类时钟应用于大多数时钟树结构中,其源可以是GCIO、MMCM/PLL、可编程逻辑单元(通常不建议使用)。通用时钟网络必须由BUFGCE、BUFGCE_DIV、BUFGCTRL缓冲器驱动,这些缓冲器存在于任何包含I/O列的时钟区域中。每个时钟区域最多可支持24个独立的时钟,而大多数UltraScale器件根据其拓扑、扇出及负载布局,可支持超过100个时钟树。

3)千兆位收发器时钟:千兆位收发器的发送、接收和参考时钟在使用专用的时钟资源,这些资源位于包含收发器的时钟区域内。可利用收发器时钟实现以下功能:使用BUFG_GT缓冲器驱动通用时钟网络,从而连接可编程逻辑中的任意负载;在同一收发器四连组内或不同四连组之间共享时钟。

c)时钟原语

1)大多数时钟通过全局时钟输入GCIO引脚进入器件。这些时钟经由时钟缓冲器直接驱动时钟网络,或者由位于I/O列旁的CMT进行处理和转换。

2)全局时钟缓冲器包括:24个带有时钟使能的全局时钟缓冲器、8个全局时钟控制缓冲器、4个带分频功能的全局时钟使能缓冲器。吉比特收发器用户时钟通过BUFG_GT缓冲器驱动全局时钟网络,每个邻近GTH/GTY列的时钟区域提供24个BUFG_GT缓冲器。

d)全局时钟缓冲器连接与布线

1)在UltraScale架构中,每个时钟区域内的24个BUFGCE缓冲器各自只能驱动一条特定的时钟布线轨道。然而,BUFGCTRL和BUFGCE_DIV的输出则可以通过一个多路复用器结构,灵活选用24条轨道中的任意一条。具体来说,每个BUFGCE_DIV与一个特定的BUFGCE站点共享输入连接性,而每个BUFGCTRL则与两个特定的BUFGCE站点共享输入连接性。因此,当在时钟区域中使用BUFGCE_DIV或BUFGCTRL缓冲器时,会相应地限制该区域内BUFGCE缓冲器的可用数量。

2)在器件中,一个全局时钟网络会被分配一个特定的轨道ID(0至23),供其所有的垂直、水平布线及分配资源使用。除非该时钟信号经过另一个时钟缓冲器,否则它不能更改其轨道ID。

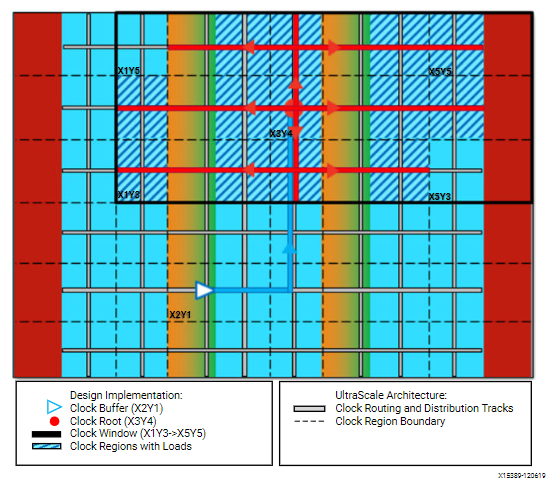

e)时钟布线、时钟根、时钟分配

1)从时钟缓冲器到时钟根:时钟信号经过一段或多段垂直和水平布线进行传输。每一段都必须使用相同的轨道ID(0至23之间)。

2)在时钟根处:时钟信号从布线轨道过渡到具有相同轨道ID的分配轨道。为了降低偏移,时钟根通常位于时钟窗口中心的时钟区域内。时钟窗口是包含该时钟网络所有负载所在时钟区域的矩形区域。出于优化偏移的考虑,Vivado可能会将时钟根调整到非中心位置。

3)从时钟根到负载所在的CLB列:时钟信号沿着垂直分配资源(根据需要向上和向下传输),然后转入水平分配资源(根据需要向左和向右传输)。

4)CLB列的结构:每个CLB列被水平分配资源分隔为上下两半。每一半都包含若干末端时钟布线资源,这些资源可以由任何水平分配轨道接入。

5)在某些情况下,时钟缓冲器可以直接驱动到时钟分配轨道上。这通常发生在时钟根与时钟缓冲器位于同一时钟区域,或者时钟缓冲器仅驱动非时钟引脚(例如,高扇出网络)时。由于时钟布线资源是分段式的,因此只消耗那些用于穿越时钟区域或到达时钟区域内负载所需的路由段和分配段。

f)时钟树布局与布线:在以下阶段中,Vivado布局器在遵循物理XDC约束的同时,确定MMCM/PLL、全局时钟缓冲器和时钟根节点的放置位置:

1)IO与时钟放置:布局器基于连接规则和用户约束放置I/O缓冲器和MMCM/PLL。布局器将时钟缓冲器分配到时钟区域,但除非使用LOC属性进行约束,否则不会分配到具体站点。仅驱动非时钟负载的时钟缓冲器,可以在流程后期根据其驱动器和负载的放置位置移动到不同的时钟区域。此阶段出现的任何布局器错误均源于冲突的连接规则、用户约束或两者兼有。必须详细查看日志文件以了解错误的可能根本原因,从而做出适当的设计或约束更改。

2)SLR分区(仅限SSI技术器件)与全局布局:布局器基于早期的驱动器和负载放置执行初始时钟树实现。每个时钟网络都与一个时钟窗口相关联。时钟窗口的过度重叠可能导致因预期的时钟布线竞争而引发布局器错误。当时钟分区错误发生时,日志文件会显示每个时钟网络的最后时钟预算解决方案以及每个时钟区域中存在的独立时钟网络数量。请详细查看日志文件,以确定应从过度使用的时钟区域中移除哪些时钟。可通过以下方法移除时钟:①通过合并相同的同步时钟、移除不必要的MMCM反馈时钟或将低扇出时钟与高扇出时钟整合,来减少设计中的时钟数量;②将时钟原语移动到不同的时钟区域,特别是那些没有基于连接的放置规则的时钟原语;③对时钟负载添加布局规划约束,使扇出较小的时钟更靠近其驱动器或远离使用率高的时钟区域。布局器会多次优化时钟树实现,以帮助提升时序质量。例如,在后续的布局优化阶段,布局器会分析每个具有挑战性的时钟,以确定更好的时钟根节点位置。

3)时钟树预布线:布局器指导后续的实现步骤,并为布局后时序分析提供准确的延迟估计。布局完成后,Vivado工具可以按以下方式修改时钟树实现:①Vivado物理优化器可以复制单元并将其移动到没有关联时钟的时钟区域;②Vivado布线器可以进行调整以改善时序质量并使时钟布线合法化。

g)时钟规划

1)时钟规划必须基于目标器件中高扇出时钟和低扇出时钟的总数量。

2)高扇出时钟几乎跨越整个SSI技术器件的SLR,或几乎跨越单片器件的所有时钟区域。设计中使用的时钟数量超过24个可能导致问题,需要特殊设计考虑或其他前期规划。注意: 在ZHOLD和BUF_IN补偿模式下,MMCM反馈时钟路径在布线轨道、时钟根节点位置、分布轨道方面与CLKOUT0时钟路径相匹配,因此,当时钟缓冲器和时钟根节点相距较远时,反馈时钟可被视为高扇出时钟。

3)在大多数情况下,低扇出时钟是指连接少于5,000个时钟引脚,且这些引脚放置在3个或更少的水平相邻时钟区域内的时钟网络。时钟布线、时钟根节点、时钟分布都包含在局部区域内。在某些情况下,布局器预期能识别出低扇出时钟但可能失败。这可能是由于设计规模、器件大小、物理XDC约束(如LOC约束或Pblock)阻止了布局器将负载放置在局部区域所致。为了解决此问题,可能需要通过手动创建Pblock或修改现有物理约束来指导工具。由BUFG_GT驱动的时钟是低扇出时钟的一个例子。Vivado布局器会自动识别这些时钟网络,并将其负载限制在GT接口相邻的时钟区域内。

4)高扇出时钟与低扇出时钟的均衡使用:与先前的AMD器件系列相比,UltraScale器件支持更多的时钟数量。当存在24个或更少的时钟时,除非存在冲突的用户约束,否则所有时钟都可以被视为高扇出时钟,而不会冒发生布局或布线冲突的风险。接近300个时钟时,对于一个目标器件具有6行时钟区域且仅包含低扇出时钟的设计(每个时钟最多覆盖3个时钟区域),可能需要的时钟数量为:6行 x 每行2个时钟窗口 x 每个区域24个时钟 = 288个时钟。低扇出时钟窗口没有固定大小,但通常在1到3个时钟区域之间。高扇出时钟很少跨越整个器件或整个SLR。高扇出时钟单片器件最多12个,SSI技术器件最多24个。低扇出时钟最多12个加上每个已使用的GT Quad8个。

h)时钟约束

1)对I/O、MMCM、PLL、GT使用LOC约束:为全局时钟输入引脚分配PACKAGE_PIN约束,或为IOB分配LOC约束,都会影响时钟网络,直接连接到该输入端口MMCM/PLL和时钟缓冲器必须被放置在同一个时钟区域。直接连接到MMCM或PLL输出的时钟缓冲器,以及连接到其输入端的输入时钟端口,会被自动放置在同一时钟区域。如果某个输入时钟端口与一个 MMCM 或 PLL 直接相连,但被约束到了不同的时钟区域,则您必须手动插入一个时钟缓冲器,并为其输出网络设置CLOCK_DEDICATED_ROUTE约束。AMD不建议对时钟缓冲器单元使用LOC约束。此方法会强制时钟使用特定的轨道ID,可能导致无法合法完成布线。仅当您完全了解设计的整个时钟树结构,且布局在整个设计中保持一致时,才考虑在UltraScale器件中对高扇出时钟缓冲器使用LOC约束。即使采取了这些预防措施,由于设计或约束的更改,仍可能在实现过程中发生冲突。

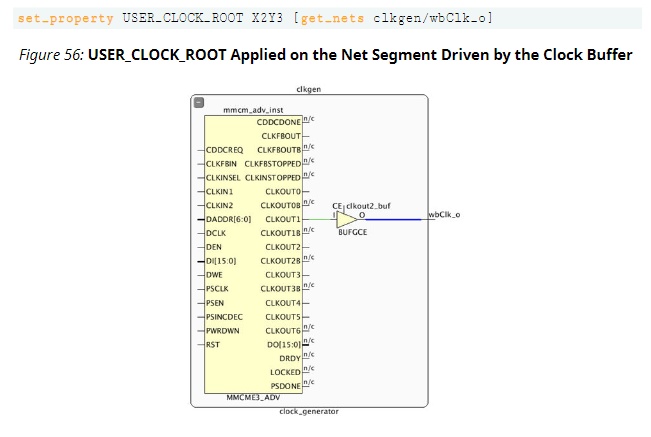

2)在时钟缓冲器上使用CLOCK_REGION属性:可以使用CLOCK_REGION约束将时钟缓冲器分配到一个时钟区域,而无需指定具体站点,这为布局器在优化所有时钟树和确定合适的缓冲器站点以成功布线所有时钟时提供了更大的灵活性。也可以使用CLOCK_REGION约束来指导级联时钟缓冲器或由非时钟原语(例如逻辑单元)驱动的时钟缓冲器的布局。注意:在大多数情况下,时钟缓冲器由已约束到某个时钟区域的输入时钟端口、MMCM、PLL、GT*_CHANNEL直接驱动。如果是这种情况,时钟缓冲器会自动放置在同一时钟区域,无需使用 CLOCK_REGION 约束。set_property CLOCK_REGION X2Y2 [get_cells clkgen/clkout2_buf]。

3)使用Pblock限制时钟缓冲器布局范围:当时钟缓冲器不需要放置在特定时钟区域时,可以使用Pblock来指定一个时钟区域范围。例如,当需要一个BUFGCTRL来复用两个位于不同区域的时钟时,可以将该BUFGCTRL分配到包含这两个时钟驱动区域之间时钟区域的Pblock中,让布局器寻找一个合法的位置。注意: AMD不建议对单个时钟区域使用Pblock。

4)在时钟网络上使用USER_CLOCK_ROOT属性:可以使用USER_CLOCK_ROOT属性来强制指定由时钟缓冲器驱动的时钟的根位置,设置USER_CLOCK_ROOT属性会影响设计布局,因为它通过修改时钟布线从而影响插入延迟和偏移。USER_CLOCK_ROOT的值是一个时钟区域,并且必须设置在由高扇出时钟缓冲器直接驱动的网络段上。

布局完成后,可以使用CLOCK_ROOT属性查询实际的时钟根。report_clock_utilization -clock_roots_only。

5)在多个时钟网络上使用CLOCK_DELAY_GROUP约束:可以使用CLOCK_DELAY_GROUP约束来匹配多个相关时钟网络的插入延迟,这些网络由不同的时钟缓冲器驱动。此约束通常用于最小化源自同一MMCM、PLL、GT的时钟之间在同步CDC时序路径上的偏移。必须将该约束设置在直接连接到时钟缓冲器的网络段上。set_property CLOCK_DELAY_GROUP grp12 [get_nets [clk1_net clk2_net]]。

6)使用CLOCK_DEDICATED_ROUTE约束:CLOCK_DEDICATED_ROUTE约束通常用于当从一个时钟区域的时钟缓冲器驱动到另一个时钟区域的MMCM/PLL时。默认情况下,该约束设置为TRUE,此时缓冲器/MMCM或缓冲器/PLL对必须放置在同一时钟区域。注意: 在 UltraScale器件上使用7系列器件的CLOCK_DEDICATED_ROUTE值BACKBONE,会产生与SAME_CMT_COLUMN相同的行为。

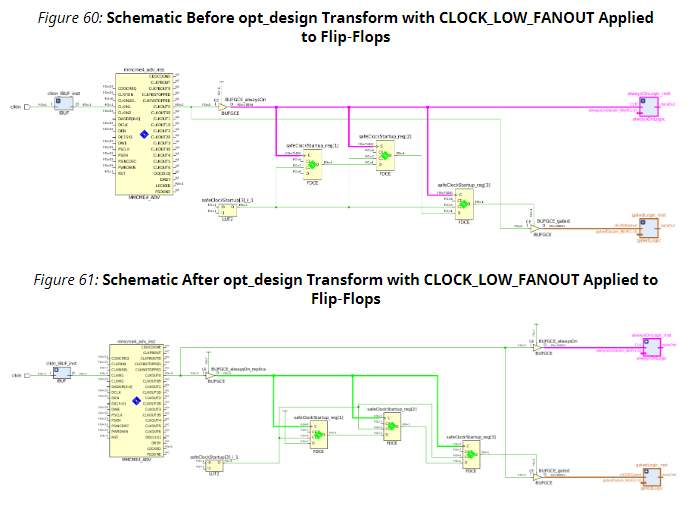

7)使用CLOCK_LOW_FANOUT约束:

①可以使用CLOCK_LOW_FANOUT约束将时钟缓冲器的负载限制在单个时钟区域内。此约束可应用于由全局时钟缓冲器直接驱动的时钟网络段,也可应用于一组触发器。CLOCK_LOW_FANOUT约束在与USER_CLOCK_ROOT、CLOCK_DELAY_GROUP、CLOCK_DEDICATED_ROUTE等其他时钟约束冲突时,优先级较低。若发生冲突,CLOCK_LOW_FANOUT将不会被遵守。

②在触发器上应用约束的示例:对由全局时钟缓冲器驱动的一组触发器设置CLOCK_LOW_FANOUT约束,会导致opt_design工具创建一个新的并行全局时钟缓冲器来隔离这些触发器。在place_design阶段,由这个新创建的并行全局时钟缓冲器驱动的、被隔离的触发器,将被限制在单个时钟区域内。set_property CLOCK_LOW_FANOUT TRUE [get_cells safeClockStartup_reg[*]]

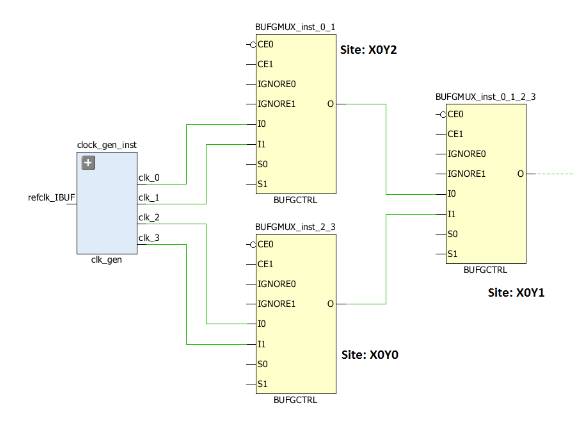

i)时钟拓扑建议

1)AMD建议采用结构简单、所需时钟缓冲器数量最少的时钟树拓扑。使用额外的时钟缓冲器会占用更多布线轨道,在时钟布线需求接近最大容量的时钟区域,可能导致布局错误或布线冲突。这对于时钟资源使用率较高、可能发生时钟竞争的设计尤为重要。

2)使用并行时钟缓冲器,可实现以下目标:

①确保跨多次实现运行的布局可预测性:当并行时钟缓冲器由相同的输入时钟端口、MMCM、PLL、GT*_CHANNEL直接驱动时,无论网表变更或逻辑布局如何变化,这些缓冲器始终与其驱动源放置在同一时钟区域;

②匹配时钟树各分支间的插入延迟:在处理分支间存在同步路径的情况时,AMD推荐使用并行缓冲器而非级联缓冲器。使用级联缓冲器时,即使采用CLOCK_DELAY_GROUP或USER_CLOCK_ROOT约束,各分支间的时钟插入延迟也难以匹配。这可能导致高时钟偏移,使时序收敛极具挑战性甚至无法实现。

3)避免适用级联时钟缓冲器:

①通常,AMD不建议使用级联缓冲器来人为增加延迟或减少不相关时钟树分支间的偏移。与BUFGCTRL之间的连接不同,其他时钟缓冲器之间的连接在架构上并无专用路径。因此,未加约束的级联缓冲器的相对布局位置是不可预测的,所有布局规则都将优先于对它们的布局。然而,在以下特定情况下,可以考虑使用级联时钟缓冲器:

②将时钟布线至位于另一时钟区域的时钟缓冲器:当需要为位于不同时钟区域的MMCM生成的时钟实现时钟复用时,常会用到此方法。虽然其中一个MMCM可以直接驱动BUFGCTRL(BUFGMUX),但另一个MMCM则需要一个中间时钟缓冲器才能将其时钟信号路由到另一个区域。

③平衡时钟树分支间的时钟缓冲层级(当存在同步路径时):当两个时钟树分支之间存在同步路径时,需要平衡其时钟缓冲的层级数量。注意:Vivado的逻辑优化命令opt_design无法感知时序时钟与时钟网络分支之间的时序关系。因此,opt_design会尽可能地移除级联或冗余的时钟缓冲。在此示例中,除非设置DONT_TOUCH="TRUE"属性,否则opt_design将移除BUFGCE_inst_1。如果时钟树分支之间仅存在异步路径,则只要接收时钟域配备了适当的同步电路,就无需平衡这些分支。

④当平衡时钟树分支时,将所有同一层级的时钟缓冲分配到同一时钟区域。将级联的缓冲保持在同一或相邻的时钟区域内。注意:如果确实需要,AMD建议使用两个级联的BUFGCTRL,而非级联的BUFGCE。利用专用布线资源,当两个BUFGCTRL都放置在同一时钟区域内时,可以以最小延迟实现二者的级联。

4)时钟复用

①可以通过组合使用并联和级联的BUFGCTRL缓冲器来构建时钟复用器。布局器会根据时钟缓冲器站点的可用性寻找最优的布局方案。在可能的情况下,布局器会将BUFGCTRL放置在相邻的站点,以利用其专用的级联路径。如果无法实现,布局器会尝试将同一层级的BUFGCTRL放置在相邻的时钟区域内。

j)PLL/MMCM反馈路径与补偿模式

1)PLL不支持延迟补偿,始终工作在INTERNAL补偿模式下,这意味着它们不需要反馈路径。同样地,设置为INTERNAL补偿模式的MMCM也不需要反馈路径。在这两种情况下,Vivado并不总是自动移除不必要的反馈时钟缓冲器。为了减少高扇出时钟资源的使用量,尤其是在时钟资源使用率高、可能发生时钟争用的设计中,必须手动移除这些时钟缓冲器。

2)当MMCM的补偿模式设置为ZHOLD或BUF_IN时,布局器会为反馈缓冲器驱动的网络以及所有直接连接到CLKOUT0引脚的缓冲器驱动的网络分配相同的时钟根。这确保了插入延迟相互匹配,从而使连接到CLKOUT0的I/O端口和时序单元相位对齐,并满足器件接口的保持时间要求。Vivado会综合考虑这些网络的所有负载,以最优方式定义时钟根。

3)Vivado不会自动匹配其他MMCM输出所驱动的网络的插入延迟。要匹配其他MMCM输出缓冲器所驱动网络的插入延迟,可以使用以下属性:

①CLOCK_DELAY_GROUP:为反馈时钟缓冲器、CLKOUT0缓冲器以及其他所需的MMCM输出缓冲器直接驱动的网络,应用相同的CLOCK_DELAY_GROUP属性值。这是首选方法。

②USER_CLOCK_ROOT:如果需要强制指定特定的时钟根,可以在反馈时钟缓冲器、CLKOUT0缓冲器以及其他所需的MMCM输出缓冲器驱动的网络上,使用相同的USER_CLOCK_ROOT属性值。

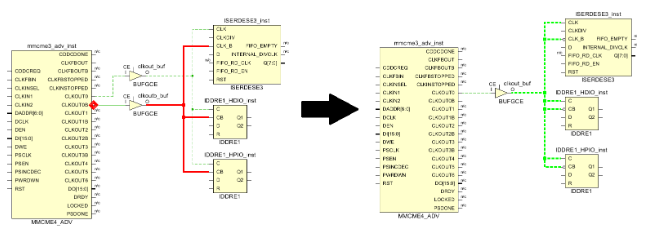

k)对于UltraScale和UltraScale+器件中的ISERDESE3和IDDRE1时钟,时钟引脚和反相时钟引脚之间存在最大偏斜要求。为了满足最大偏斜要求,当使用本地反相时,AMD建议对时钟引脚和反相时钟引脚使用单一网络。

l)ZHOLD/BUF_IN补偿模式概述

1)ZHOLD补偿表示MMCM被配置为向整个I/O列的所有I/O寄存器提供负保持时间裕量。当一个CCIO驱动一个单独且配置为ZHOLD补偿模式的MMCM时,布局器会尝试将该MMCM与该CCIO放置在同一时钟区域。在此情况下,CCIO可直接驱动MMCM,无需经过BUFG缓冲,从而确保ZHOLD补偿效果持续有效。

2)然而,如果一个CCIO除了驱动ZHOLD模式的MMCM外,还驱动另一个MMCM,逻辑优化工具通常会尝试在CCIO后插入一个BUFG以规范时钟路由。这将导致ZHOLD补偿模式更改为BUF_IN。为避免此问题,必须确保CCIO直接驱动配置为ZHOLD模式的MMCM,而通过一个BUFG来驱动其他MMCM。同时,需将BUFG输出网络的CLOCK_DEDICATED_ROUTE属性设置为ANY_CMT_COLUMN。

3)时钟插入延迟会随时钟根位置的变化而变化,而时钟根的布局又取决于负载的物理分布,这可能导致不同设计实现运行间的时序结果存在差异。这种差异会影响器件内部时序以及I/O接口时序。

m)

1)重要提示:为确保并行BUFGCE_DIV单元之间的时序安全(当BUFGCE_DIVIDE属性设置为大于1的值时),两个缓冲器必须使用相同的使能信号CE和相同的复位信号RST。否则,分频时钟在硬件中可能会彼此产生相移,而Vivado不会报告此情况。

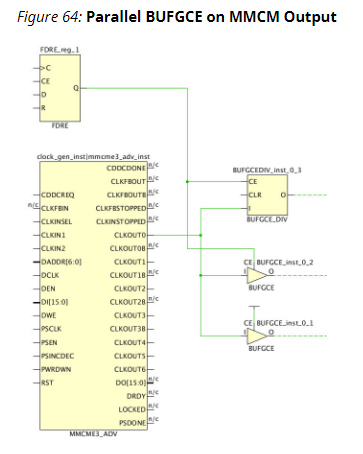

7系列器件时钟

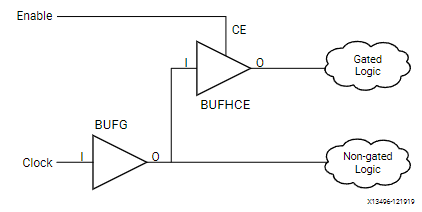

a)利用水平时钟区域缓冲器实现时钟门控

1)可以将水平时钟区域缓冲器(BUFHCE)与全局时钟缓冲器(BUFG)配合使用,以实现中等粒度的时钟门控功能。对于需要在特定时段暂停时钟、且负载规模在数百至数千范围内的时钟域局部电路,BUFHCE是一种高效的时钟资源。单个BUFG可以驱动位于相同或不同时钟区域的多个BUFHCE,从而支持对多个低偏斜时钟域进行独立的启停控制。

2)当BUFH独立使用时,连接到它的所有负载必须位于同一时钟区域内。这使其非常适用于对高速、细粒度(负载较少)的时钟需求。利用BUFHCE可以在特定时钟区域内实现中等粒度的时钟门控。设计时,必须确保由BUFH驱动的资源总量不超过该时钟区域的容量,且不存在其他冲突。

3)BUFH时钟域与由BUFG、其他BUFH、其他时钟资源驱动的时钟域之间,其相位关系可能不同。唯一的例外是当两个BUFH由同一时钟源驱动,并分别位于水平相邻的两个时钟区域时。在这种情况下,左右区域间的时钟偏斜具有高度可控的相位关系,数据可以安全地跨越这两个BUFH时钟域。BUFH也可用于访问与时钟输入或高速收发器位置相对的时钟管理模块(MMCM)或锁相环(PLL),但采用此方案时,必须确认目标MMCM或PLL资源可用。

(未完待续!)

下面内容参考Xilinx PG065

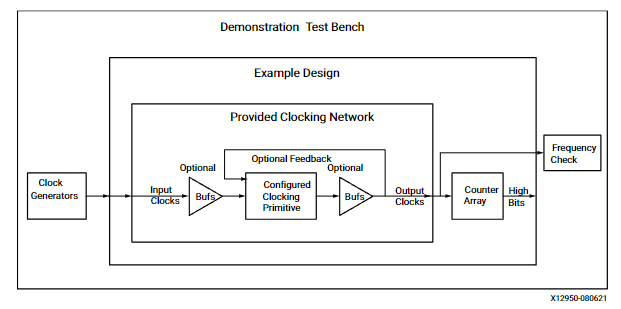

clock_wizard概述

a)特性:

1)支持多种时钟原语:提供MMCM/PLL原语选项,并在IDE中启用对应原语所支持的功能配置;

2)安全时钟启动与序列化输出:Safe Clock Startup功能可确保输出时钟稳定有效,启用Sequencing功能后,还可实现按指定顺序使能的序列化输出时钟;

3)灵活的时钟接口:每个时钟网络最多支持2路输入时钟和7路输出时钟;

4)动态重配置接口:提供AXI4-Lite接口,支持在运行时动态重配置时钟原语的倍频、分频、相位偏移、空比参数;

5)智能自动配置:根据所选时钟功能自动配置相应的时钟原语;

6)自动频率计算:对含振荡器的原语,自动计算VCO频率,并依据输入与输出频率需求提供相应的倍频与分频值。

b)功能

1)频率合成:允许输出时钟频率与当前输入时钟频率不同;

2)扩频:提供调制输出时钟,可降低电子设备EMI的频谱密度。此功能仅适用于MMCM(E2/E3/E4)_ADV原语。目前UNISIM仿真库暂不支持此功能;

3)相位对齐:允许输出时钟相位锁定至参考时钟,例如器件的输入时钟引脚;

4)最小化功耗:允许最小化原语所需功耗,但可能以牺牲频率、相位偏移、占空比精度为代价;

5)动态相位偏移:允许改变输出时钟之间的相位关系;

6)动态重配置:允许在器件配置完成后更改原语的编程。选择此选项时,默认使用AXI4-Lite接口来重新配置时钟原语;

7)平衡模式:选择平衡模式将导致软件选择正确的带宽以优化抖动性能;

8)最小化输出抖动:此功能可最小化输出时钟上的抖动,但会以增加功耗和可能引入输出时钟相位误差为代价。此功能与最大化输入抖动滤波功能不可同时使用;

9)最大化输入抖动滤波:允许输入时钟具有更大的输入抖动,但可能会对输出时钟的抖动产生负面影响。此功能与最小化输出抖动功能不可同时使用;

10)安全时钟启动与序列化:可用于在输出端获得稳定有效的时钟。它还可按配置中指定的特定顺序启用时钟;

11)时钟监控:监控Clocking Wizard的时钟输入。它最多可监控四个时钟。可以监控输入频率是否超出预期范围,并检测时钟停止和时钟毛刺;

12)自动选择原语:根据需求实例化合适的时钟原语。无需了解MMCM或PLL的规格来判断哪个原语符合要求,向导将完成此工作。此功能仅适用于UltraScale™和UltraScale+™器件。

c)应用场景

1)创建具有所需频率、相位、占空比、抖动较低的时钟网络。利用扩频功能降低电子设备中的电磁干扰。

d)

d)功耗

1)可能牺牲频率、相位偏移、占空比精度的情况下,将时钟原语所需的功耗降至最低。

2)当断电输入引脚被置位时,时钟原语将进入低功耗状态,此时所有输出时钟均停止工作。

MMCM/PLL寄存器空间

a)

1)软件复位寄存器 (SRR):写入值0x0000_000A可激活软件复位。任何其他读写访问将产生未定义结果。

2)状态寄存器 (SR):位[0] = 锁定:为1时表示MMCM/PLL已锁定并可进行重配置。重配置过程中此位为0。

3)时钟监控器错误状态寄存器:此寄存器提供时钟监控功能对应的错误状态位。

4)中断状态寄存器:时钟停止、时钟超限、时钟欠限的中断状态。这些位受中断使能位控制。仅当中断使能寄存器中对应位被使能时,其中断状态才会更新到此寄存器。

5)中断使能寄存器:用于控制中断状态寄存器中时钟停止、时钟超限、时钟欠限位的中断使能。

clock_wizard设计方法

通用设计

a)提供输入时钟的频率和抖动信息。抖动可在GUI中以UI(单位间隔)或PS(皮秒)单位指定。

b)如果设计中其他逻辑模块也使用同一输入时钟,且该时钟来自全局缓冲器输出,则源类型应选择无缓冲;否则应选择全局缓冲。如果仅该内核使用输入时钟,则源类型应选择时钟专用引脚。

复位

a)时钟向导为时钟原语提供了一个高电平有效的异步复位信号。

b)在时钟切换期间,必须保持内核处于复位状态。

c)当输入时钟或反馈时钟丢失时,clkinstopped或clkfbstopped状态信号会置位。时钟恢复后,clkinstopped信号将取消置位,此时必须施加一次复位。

功能概述

a)经验丰富的用户可通过向导明确配置其选定的时钟原语;而经验较少的用户则可以让向导根据其各个时钟网络所需的功能,自动确定最佳的原语和配置。

b)默认情况下为一个输入时钟,但通过选择辅助时钟源,可以配置两个输入时钟。仅需提供指定单位的输入时钟时序参数;向导将根据需要使用这些参数来配置输出时钟。

c)输入所需的时序参数(频率、相位、占空比),时钟向导将自动选择和配置时钟原语及网络,以满足所请求的特性。如果由于可用输入时钟数量的限制无法完全满足所请求的参数设置,则会提供最佳近似设置。在这种情况下,时钟会进行排序,clk_out1是最高优先级时钟,最有可能满足请求的时序参数。向导会提示在设置相位和占空比之前,先进行频率参数设置。

d)除了配置器件内的时钟原语,向导还协助构建时钟网络。它为输入和输出时钟都提供了缓冲选项。原语的反馈可由用户控制,或交由向导自动连接。如果选择自动反馈,反馈路径的时序将与clk_out1匹配。

e)时钟监控器

1)时钟监控器功能允许监控系统中的时钟(通常是MMCM/PLL的输入)。它能检测时钟频率变化、时钟毛刺、时钟停止。还可以选择指定所需的容差。例如,如果仅当频率比请求值高出1MHz时才报错,则必须指定1MHz的容差。

2)时钟停止:当时钟信号持续平坦(无跳变)超过10个时钟周期时,时钟停止信号变高。一旦时钟停滞达到或超过10个周期,它将启动检测停止的计算,并将clock_stop信号置高。时钟停止信号不会立即变高,从时钟变平开始,最多可能需要256个时钟周期。此计算需要一组参考时钟周期时间,clock_stop变高的具体时间取决于user_clk与ref_clk的比率。

3)时钟毛刺:时钟监控器可以检测用户时钟中的毛刺。它能检测到的最小毛刺宽度为参考时钟的一个周期。时钟毛刺条件可能与时钟超限条件重叠。

4)时钟超限:时钟监控器检测用户时钟频率是否超出或低于所需频率。注意: 如果信号频率远低于期望频率,时钟欠限信号也可能在时钟停止条件下变高。如果最大用户时钟频率与最小用户时钟频率差异极大,可能会出现无法检测到超范围或毛刺的情况。

(未完待续!)