一、板卡概述

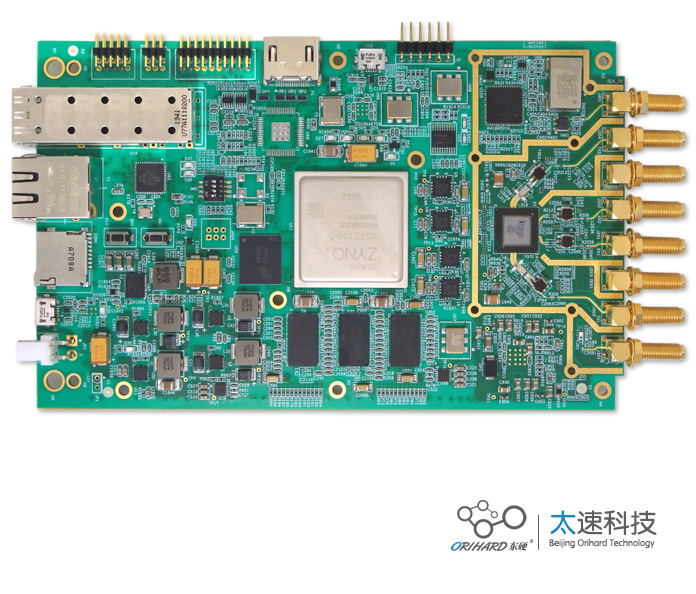

基于XC7Z100+ADRV9009的双收双发无线电射频板卡是基于Xilinx ZYNQ FPGA和ADI的无线收发芯片ADRV9009开发的专用功能板卡,用于5G小基站,无线图传,数据收发等领域。

二、板卡原理及功能

板卡使用XC7Z100 作为主处理器,包含Dual ARM Cortex-A9核处理器的嵌入式处理。PS端32bit 1GB容量DDR3存储、1路RS232接口、1路USB接口、1路10-100-1000网络接口,PS端32M QSPI flash存储、SD卡接口、8G eMMC存储;PL端64bit 2GB容量DDR3存储,PL端扩展HDMI 输出实现视频显示应用,PL端扩展9路I/O,2路SPI_LVDS接口、2路RS232接口、4个LED指示灯。

PL端外扩ADRV9009芯片,ADRV9009是一款高集成度射频(RF)、捷变收发器,提供双通道发射器和接收器、集成式频率合成器以及数字信号处理功能。这款IC具备多样化的高性能和低功耗组合,具有2路输入,2路输出,两路观测输入配合FPGA工作满足3G、4G和5G宏蜂窝时分双工(TDD)基站应用要求。

板卡数字接口:

● PS 端32bit 1GB 容量 DDR3 存储

● PS端RS232接口

● PS端USB接口

● PS端1路 10-100-1000 Mbps Ethernet (RGMII) 网络接口

● PS端QSPI flash 存储

● PS端 SD卡,Emmc存储

● PL端64bit 2GB 容量DDR3 存储

● PL端扩展HDMI 输出实现视频显示应用

● PL端扩展9路 I/O、2路SPI_LVDS、2路RS232、4路LED指示灯

● PL端扩展1路10G SFP+光纤接口

板卡模拟接口:

● 双接收:RX1、RX2

● 双发送:TX1、TX2

● 双观测接收:ORX1、ORX2

● 外部本振接口:EXT_LO

● 外部时钟参考:REF_CLK_IN

板卡性能指标:

物理特性

● 尺寸:110x162.4mm,带外壳尺寸180*125*48 ;

● 工作温度:工业级 -40℃~ +85℃。

● 工作电压+12V ±1V;整板功耗20W。

● 重量裸板0.3KG,带散热外壳0.8KG。

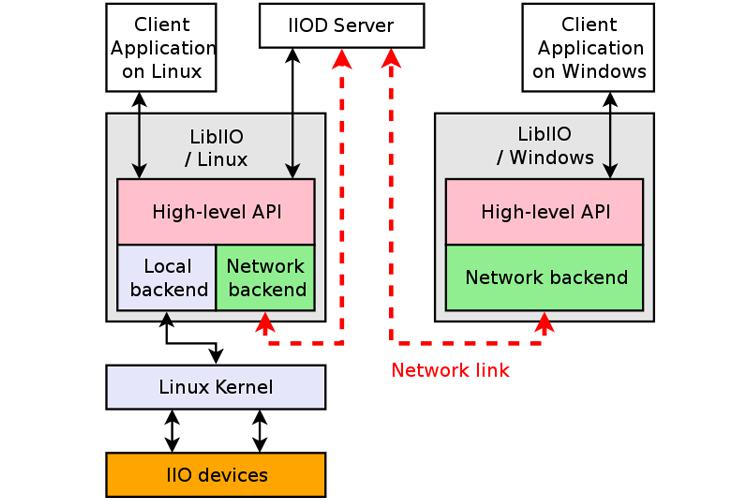

三、软件系统

参考ADI的整体软件架构:

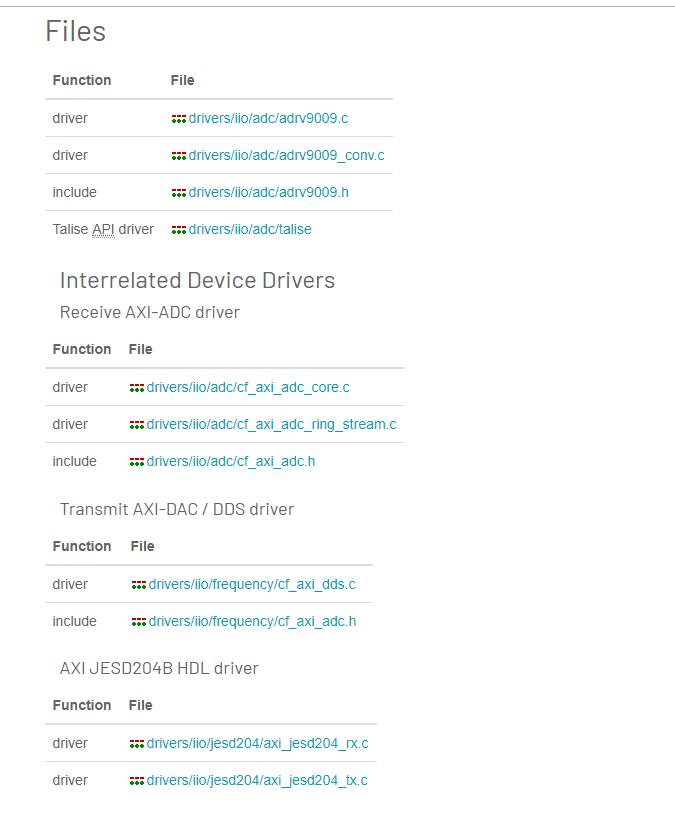

AD9009设备树及驱动 SPI访问,AD,DA访问

驱动文件https://wiki.analog.com/resources/tools-software/linux-drivers/iio-transceiver/adrv9009

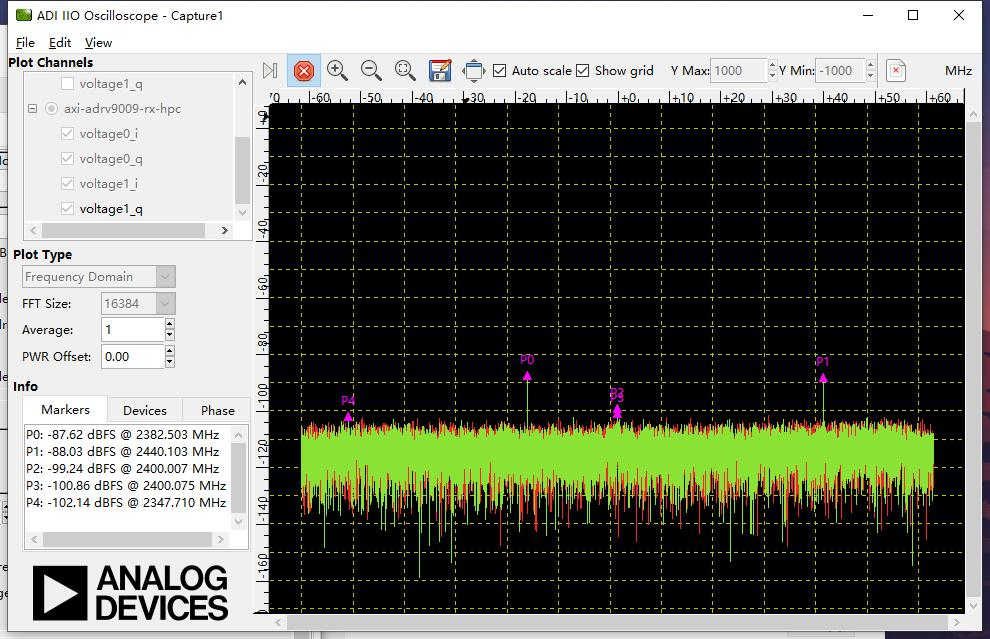

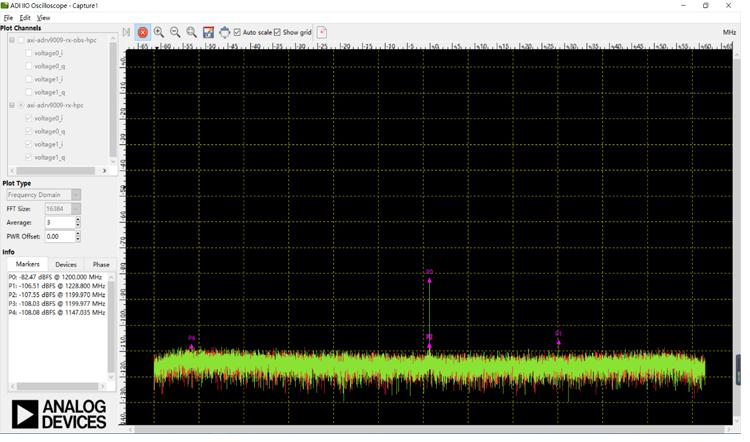

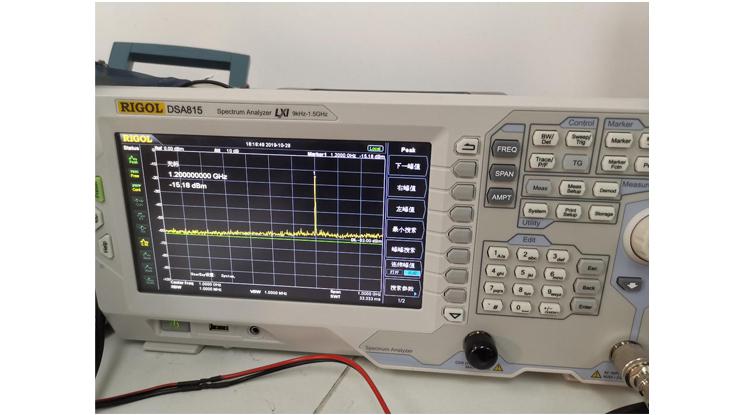

AD采集1.2G波形:

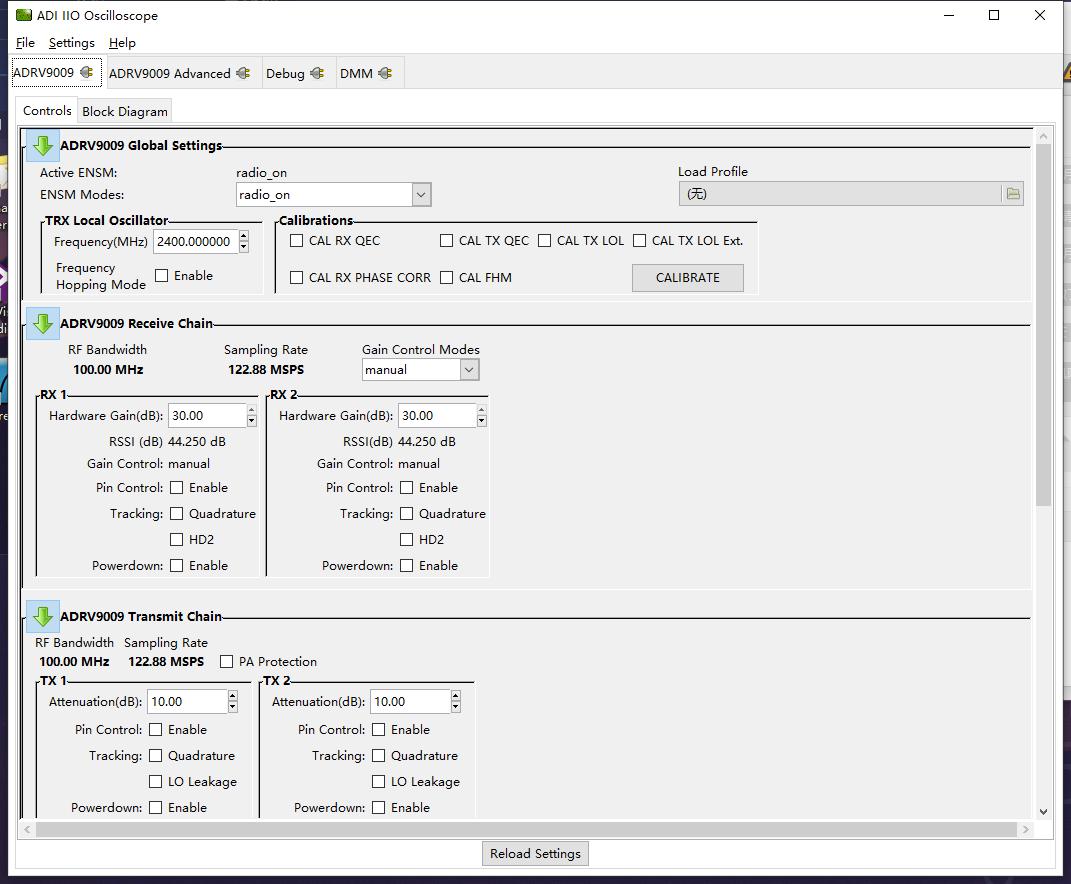

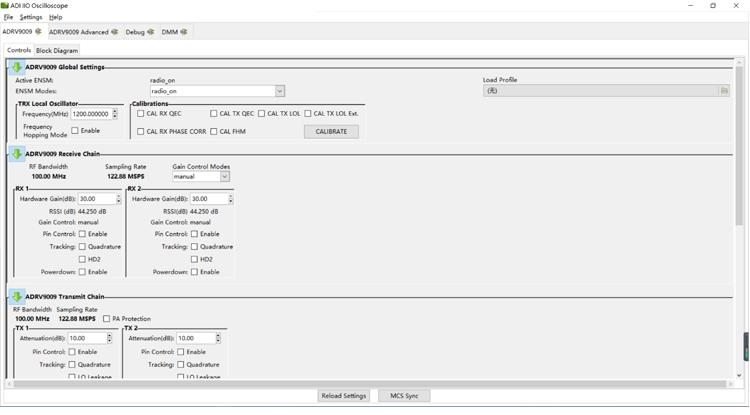

DA 输出设置1.2G及波形:

标签: 9009开发板 , XC7Z100板卡 , 视频数据收发卡 , 无线图传

标签: XC7Z100板卡, zynq XC7Z100板卡, 视频数据收发卡, 无线图传, 9009开发板