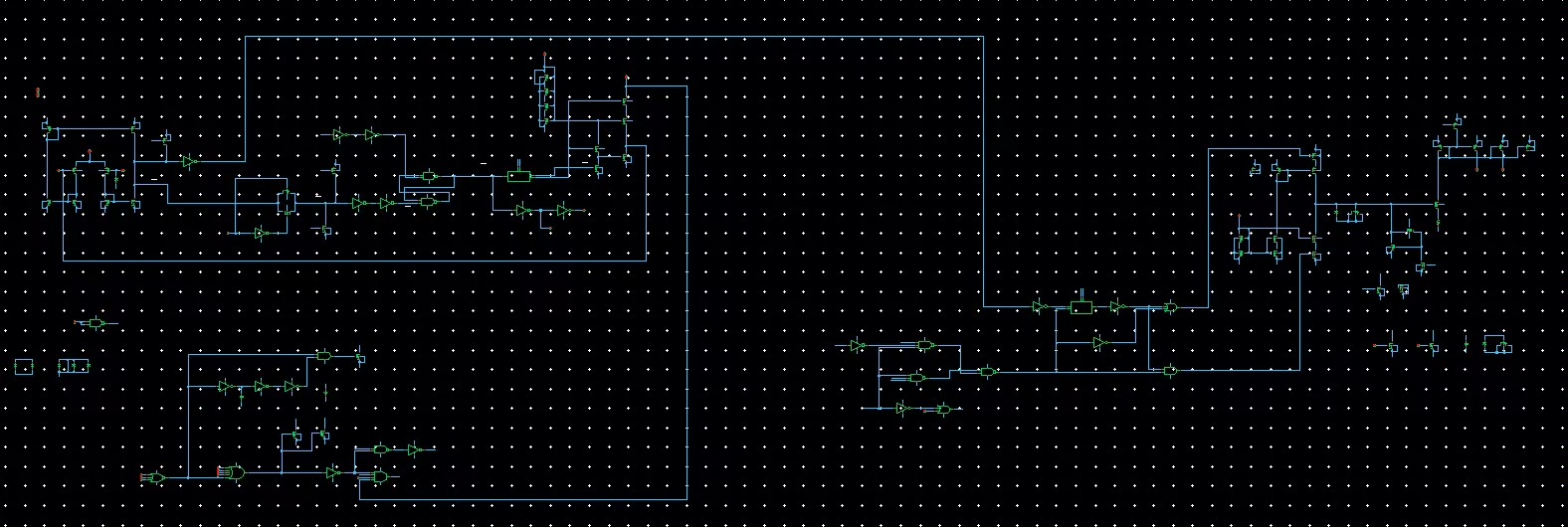

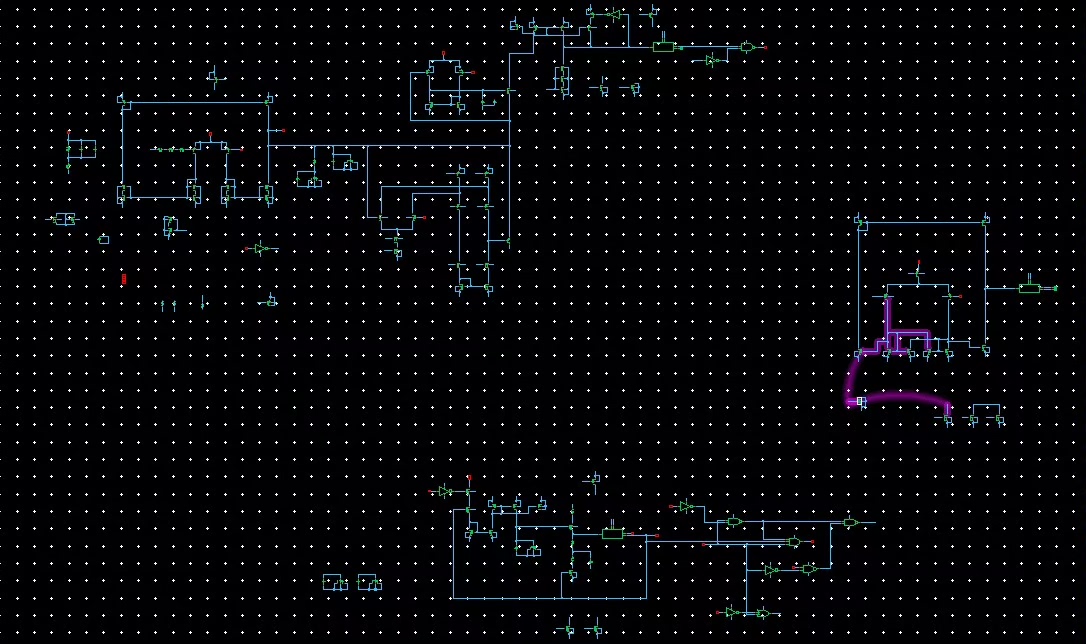

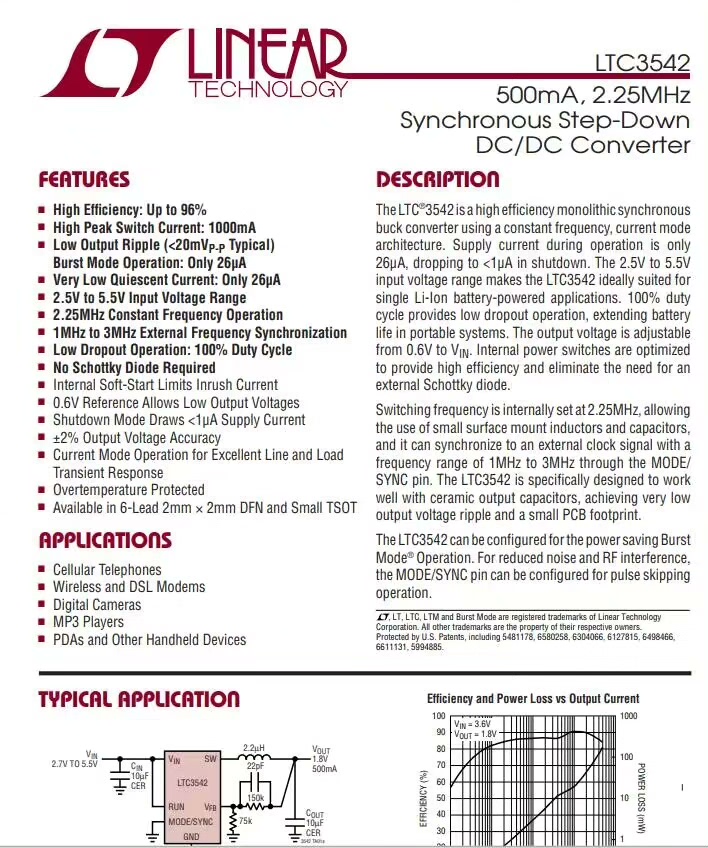

某国际知名大厂Buck型DCDC电路,LTC3542逆向电路,具有高转化效率,峰值电流模,输入2.5-5.5,输出0.6V,纹波较小,2.25MHZ的恒定频率,可以直接导入到cadence查看结构,轻载下有两种模式Burst和PSM,适合有一定电源管理基础的兄弟使用。 学习方法是:可以直接查看里面的电路结构,还有管子的宽长比参数等。 拿到原理图之后需要自己换成自己所持有的PDK就可以跑仿真了,国内大部分公司都是这样设计芯片产品的,参考价值非常大,整个芯片里面有非常多的模块,适合研究生没有项目的同学,可以拿里面的一些模块当做项目,也适合工作的拿来参考对比设计

嘿,各位电源管理领域的小伙伴们!今天来聊聊一款超有意思的国际知名大厂 Buck 型 DCDC 电路------LTC3542 的逆向电路,绝对干货满满。

电路亮点剖析

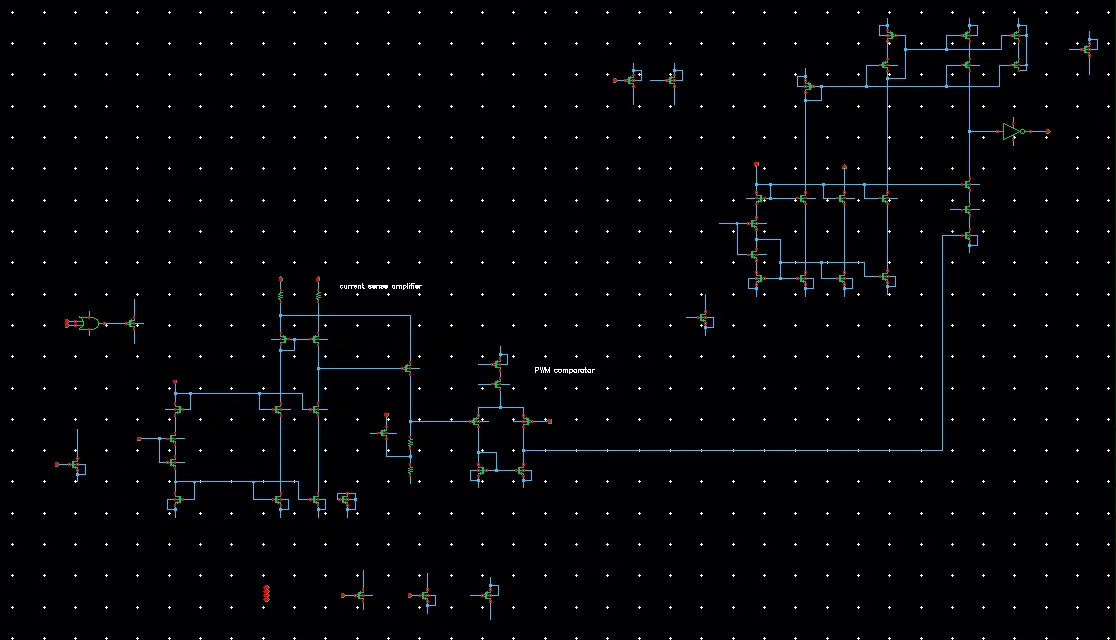

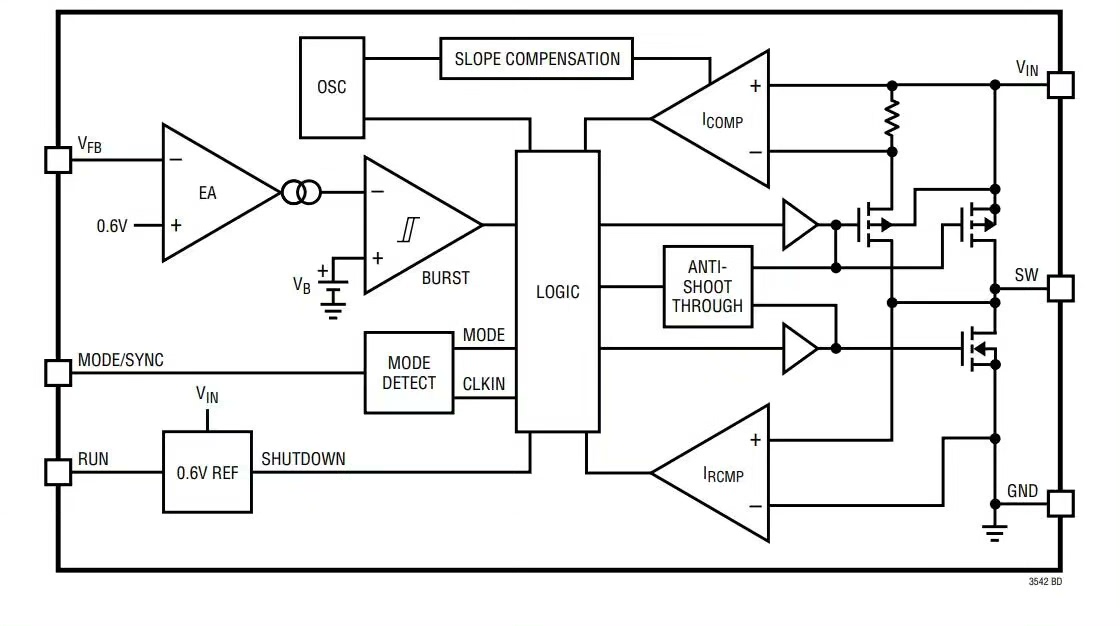

LTC3542 逆向电路可是有着不少闪光点。它具备高转化效率,在能耗利用上那叫一个出色,这对于如今追求高效节能的电子产品来说,简直是刚需。它采用峰值电流模控制方式,这种方式能够让电路对电流的变化响应迅速,保证输出的稳定性。

输入电压范围在 2.5 - 5.5V,输出却能精准地稳定在 0.6V,而且纹波还较小,这意味着在输出电压的纯净度上表现优秀。工作频率恒定在 2.25MHZ,稳定的频率能让整个电路的性能更加可控、可预测。

并且,这个电路还有个贴心设计,在轻载的情况下,它有 Burst 和 PSM 两种模式。这就好比一辆车,在不同路况下可以切换不同的驾驶模式,节能又高效。适合有一定电源管理基础的兄弟上手研究,因为理解和掌握这些特性,就能更好地发挥这个电路的优势。

电路结构探秘与代码结合

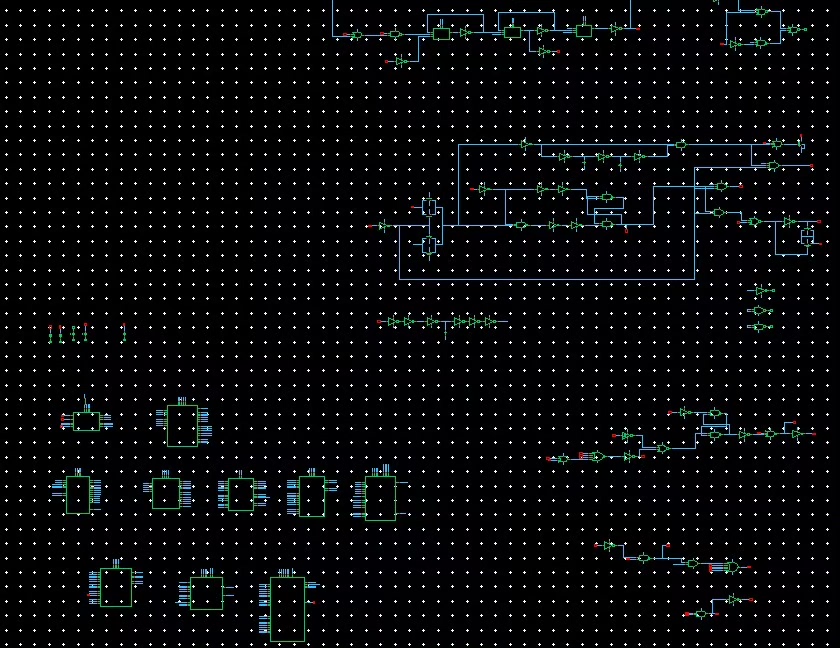

这电路牛就牛在,还能直接导入到 cadence 查看结构。比如说,在 cadence 里,你能清楚地看到各个模块之间的连接关系,就像在玩一个复杂的积木拼图,每个模块都有它独特的位置和作用。

下面咱们假设有一段简单的 Verilog 代码来描述它的某个控制模块(实际可能更复杂,但这里只为方便理解):

verilog

module control_module(

input wire clk, // 2.25MHZ 的时钟信号

input wire enable, // 使能信号

input wire [7:0] input_voltage, // 输入电压信号

output reg [7:0] output_voltage // 输出电压信号

);

always @(posedge clk or negedge enable) begin

if (!enable) begin

output_voltage <= 8'b00000000;

end else begin

// 简单的电压转换逻辑,实际会更复杂

output_voltage <= input_voltage / 4;

end

end

endmodule分析一下这段代码,clk 时钟信号就是来自电路中 2.25MHZ 的恒定频率,它像一个指挥家,控制着整个模块的节奏。enable 使能信号决定模块是否开始工作,就像开关一样。input_voltage 输入电压信号进来后,在 always 块里,根据 enable 的状态,要么把输出电压清零,要么按照简单的转换逻辑(这里是除以 4,实际肯定更贴合真实电路转换)输出电压。这段代码虽然简单,但可以类比理解电路中控制模块对电压信号的处理逻辑。

学习方法与实际应用

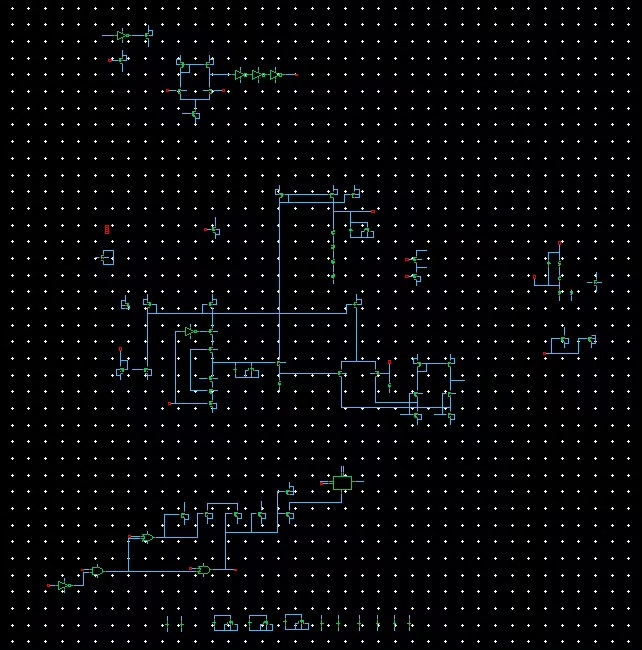

学习这个电路也不难,直接查看里面的电路结构,还有管子的宽长比参数等,这些细节可都是宝贝。管子的宽长比参数就像做菜的调料,多一点少一点,整个电路的"味道"可能就变了。

当你拿到原理图之后,还有关键一步,就是要自己换成自己所持有的 PDK 就可以跑仿真了。这就好比你拿到一个通用的食谱,得根据自己手头有的食材(PDK)来调整,才能做出符合自己口味(设计需求)的"菜"(芯片产品)。国内大部分公司都是这么设计芯片产品的,可见其参考价值非常大。

对于研究生没有项目的同学来说,这整个芯片里面有非常多的模块,随便拿出几个模块来,就能当做自己的项目,锻炼自己的实践能力。对于已经工作的朋友,也能拿来参考对比设计,看看大厂的设计思路和自己的有什么不同,取其精华,让自己的设计更上一层楼。

总之,LTC3542 逆向电路就像一座宝藏,等待着各位电源管理爱好者去挖掘和探索,希望大家都能从中学到有用的知识,提升自己的设计水平!