#灵感#一些概念

目录

[MSI 的工作原理(简化版)](#MSI 的工作原理(简化版))

[什么是 BAR?](#什么是 BAR?)

[Prefetchable vs Non-Prefetchable 的区别](#Prefetchable vs Non-Prefetchable 的区别)

[ELBI 和普通 BAR 访问有什么区别?](#ELBI 和普通 BAR 访问有什么区别?)

[misc ctrl](#misc ctrl)

[idle 状态](#idle 状态)

[pad 信号](#pad 信号)

QoS

Quality of Service,服务质量

指确保系统中的不同任务或数据流能够按照其优先级和需求获得相应的资源和服务。

QoS机制广泛应用于SoC(System on Chip)设计中,特别是在多核处理器、网络-on-Chip(NoC)、存储器子系统以及外设接口等领域。

QoS的主要目标包括:

1.带宽保障:为高优先级的数据流(如实时视频、音频传输)分配足够的带宽,防止低优先级流量占用过多资源。

2.延迟控制:保证关键任务的响应时间满足要求,例如中断请求、DMA传输等需要低延迟处理。

3.公平性与优先级调度:通过仲裁机制合理分配共享资源(如总线、内存控制器),支持多种优先级策略(固定优先级、轮询、加权公平队列等)。

4.拥塞管理:当系统负载过高时,采取丢包、限速或通知上游模块降速等方式避免系统崩溃。

5.可预测性:在安全关键领域(如汽车电子、工业控制)中,QoS需提供确定性的性能表现,便于进行 worst-case execution time (WCET) 分析。

常见的实现方式包括:

•在 AMBA AXI/AHB 总线上配置 QoS 信号(如 ARQOS, AWQOS),供主设备声明访问优先级;

•内存控制器根据 QoS 标签动态调整 DRAM 访问顺序;

•NoC 路由器基于 QoS 等级进行流量整形和路径选择;

•使用 QoS 寄存器组对各个主设备/从设备进行配置和监控。

MSI()

Message Signaled Interrupts "消息信号中断",是 PCI Express(PCIe)总线中用于设备向 CPU 发起中断请求的一种现代机制,通过"写消息"而不是"拉高电平"来触发中断的技术,更高效、更可靠,是现代设备的标准配置。

用来替代传统的引脚中断(如 INTA#、INTB# 等)。

MSI 的工作原理(简化版)

-

1.系统启动时,CPU 会给 PCIe 设备分配一个特殊的内存地址和一个数据值(称为 MSI 向量)。

-

2.当设备需要中断 CPU 时:

-

•它会向这个特殊地址写入指定的数据(就像发送一条消息)

-

•这个写操作通过 PCIe 链路传送到根复合体(Root Complex),然后被路由到对应的 CPU 或中断控制器(如 x86 上的 APIC / IOAPIC)

-

-

3.CPU 收到后就知道:"哦,是这个设备有事要处理",于是调用相应的中断服务程序(ISR)

清理中断:

1.MSI 中断发起方:设备(如 FPGA、ISP 图像处理模块)检测到事件(如一帧图像传输完成),向系统发送 MSI 消息(即往指定地址写数据)。

2.中断传递路径:该消息经由 PCIe 链路传送到 Root Complex。

3.RC 的作用:

•接收 MSI 消息

•将其转换为 CPU 可识别的中断信号(例如注入到 APIC)

•通知操作系统调用中断处理程序(ISR)

4."清中断"(Clear the interrupt):

•当 CPU 处理完中断后,通常需要 在 RC 或设备端进行确认和清理操作,以防止重复触发

•在某些架构中,RC 负责维护中断状态寄存器,必须由软件或硬件显式地 清除这些寄存器中的标志位

-

"MSI由RC清中断",意思是:中断的最终确认和清除动作是在 Root Complex 层面完成

-

清楚方法:向 Root Complex(RC)中的某个内存映射寄存器执行一次 MMIO 写操作,

什么是 BAR?

Base Address Register(基地址寄存器)。

它存在于每个 PCIe 设备的配置空间,用来告诉主机:"我这个设备需要使用哪一段内存或 I/O 地址空间",操作系统会在枚举 PCIe 设备时,根据 BAR 分配资源并映射到 CPU 可访问的地址空间。

一个 PCIe 设备通常有多个 BAR(如 BAR0, BAR1...),每个可以映射不同类型的空间:

•Memory Space(内存空间)

•I/O Space(I/O 空间,现代设备很少用)

而 Memory Space 又分为两种属性:

| 类型 | 英文 | 含义 | |------|------|------| |

可预取 | Prefetchable | 数据可以被缓存、预加载,适合大块数据缓冲区(如帧缓存) | |

不可预取 | Non-Prefetchable | 不能预取,必须按序访问,常用于设备控制寄存器 |

Prefetchable vs Non-Prefetchable 的区别

| 对比项 | Prefetchable(可预取) | Non-Prefetchable(不可预取) |

|---|---|---|

| 是否允许缓存 | ✅ 是 | ⚠️ 一般不缓存或弱排序 |

| 是否允许预读 | ✅ 允许 CPU 提前读取数据以提升性能 | ❌ 禁止预读 |

| 访问语义 | 类似普通内存,适用于大数据块(如图像帧 buffer) | 必须严格按程序顺序访问,适用于寄存器 |

| 性能优化 | 支持流水线、乱序执行、DMA 优化 | 更保守,确保每次写入都立即生效 |

| 典型用途 | 帧缓存、DMA 缓冲区 | 寄存器配置、状态查询、中断控制等 |

ELBI

(External Local Bus Interface外部本地总线接口)

概念:ELBI 是一种轻量级、低延迟的总线接口,用于 CPU 或调试主机通过软件方式直接读写 PCIe 设备的配置空间或内部寄存器,常用于芯片 bring-up 和驱动前初始化。

技术上,ELBI 是一种内存映射型的 CPU 到 PCIe 子系统通信通道,将 PCIe 设备的配置寄存器"映射"到 SOC 的物理地址空间。

通过向特定内存地址写入命令,可以实现对 PCIe 设备的配置空间(Configuration Space)进行读写操作,而无需依赖完整的 PCIe 驱动栈。

ELBI 和普通 BAR 访问有什么区别?

| 对比项 | 普通 BAR 访问(运行时) | ELBI 接口(初始化/调试) |

|---|---|---|

| 使用时机 | 系统正常运行后,驱动已加载 | 芯片上电初期、BIOS/Bootloader 阶段 |

| 是否需要链路训练完成 | ✅ 是(必须 Link Up) | ⚠️ 否(可在 Link Down 时使用) |

| 访问目标 | 设备的功能寄存器、DMA 缓冲区 | PCIe 控制器本身的内部寄存器、PHY、RC 配置 |

| 实现方式 | MMIO / DMA | 内存映射 + 寄存器偏移 |

| 典型用途 | 图像采集、数据传输 | 初始化 PCIe 控制器、修改 Vendor ID、调试链路失败 |

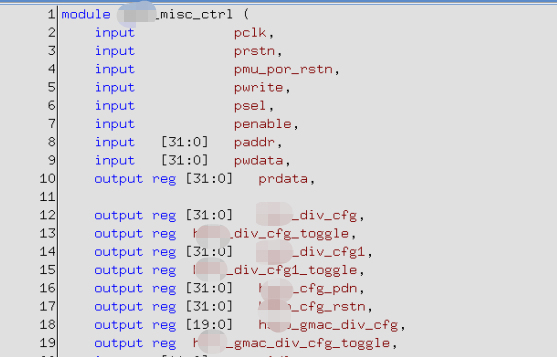

misc ctrl

MISC CTRL 是 Miscellaneous Control 的缩写,中文意思是"杂项控制"或"其他控制"。在RTL设计中,它通常指那些不属于主要功能模块、但又是系统运行必需的各种控制信号。

MISC CTRL 通常包括:

- 测试和调试接口

-

扫描测试模式(Scan Mode)\MBIST(存储器内建自测试)控制\边界扫描(Boundary Scan)

-

JTAG调试接口

- 时钟和复位管理

- 时钟门控使能\ 分频器配置 复位同步控制 \电源管理状态

3.配置寄存器

-

模式选择(如工作模式、低功耗模式)参数配置(如中断使能、超时阈值)

-

状态指示(如错误状态、完成标志)

-

举例子:

-

- 杂项控制

- 看门狗定时器 \中断控制\ 电源域控制 \\温度传感器控制

idle 状态

在时钟设置中,Idle 指的是空闲状态或待机状态,表示模块当前没有执行有效工作,处于低功耗或等待任务的状态。

Idle 的具体含义----------电源管理状态

-

Idle = 1:模块处于空闲状态,可以关闭时钟或降低频率以节省功耗

-

Idle = 0:模块正在工作,需要正常时钟

pad 信号

PAD 信号 是 RTL 设计中用于连接芯片内部逻辑与外部引脚的接口信号,是芯片与外部世界通信的桥梁。

PAD 信号主要承担以下功能:

-

输入信号:将外部信号(如时钟、复位、数据)引入芯片内部

-

输出信号:将芯片内部逻辑结果驱动到外部引脚

-

双向信号:支持输入输出双向传输

-

电源/地:提供电源和接地连接

pin MUX

Pin MUX 是 Pin Multiplexer 的缩写,中文意思是"引脚复用器"。在芯片设计中,它指的是将多个功能信号复用到同一个物理引脚的技术。

核心功能: Pin MUX 允许一个物理引脚在不同时间或不同模式下承载不同的功能信号,通过配置寄存器来选择当前有效的功能。例如,一个引脚可以配置为:

-

GPIO(通用输入输出)

-

I2C 数据线

-

UART 发送

-

PWM 输出