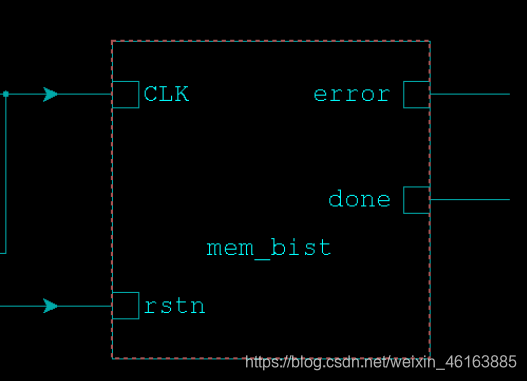

SRAM BIST 顶层

SRAM BIST 顶层

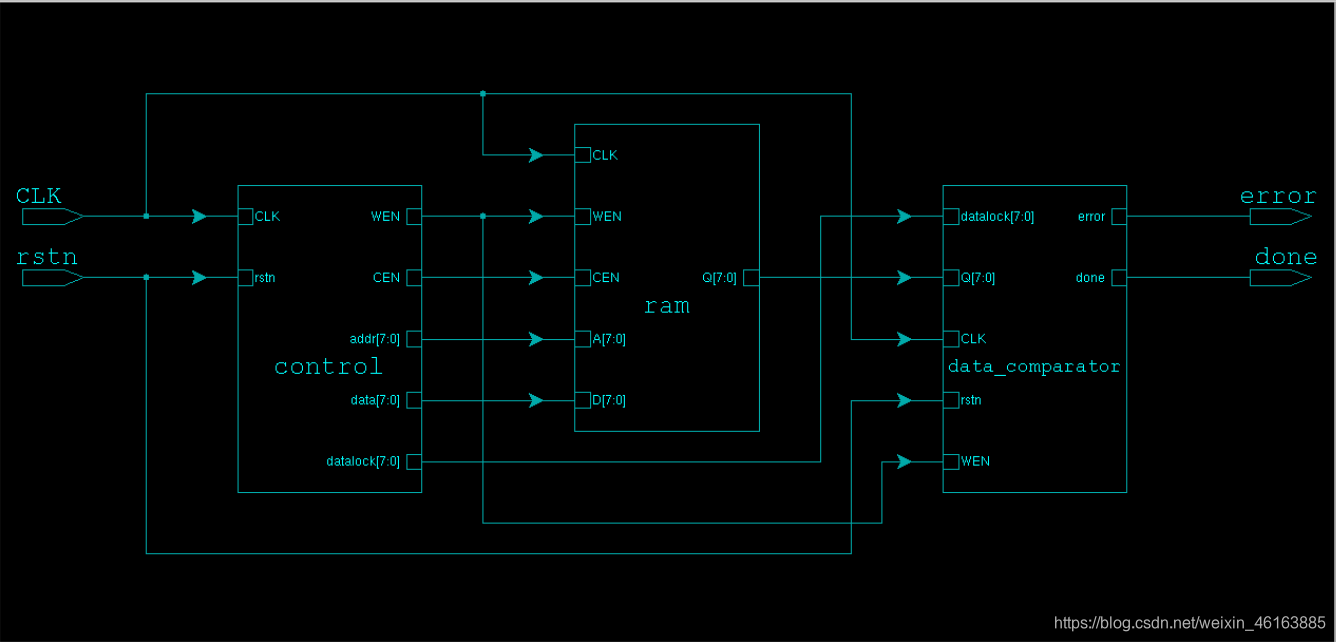

RSAM BIST 结构图'

RSAM BIST 结构图'

SRAM BIST : MEM_BIST.V

sql

////////////////////////////////////////////

//Author : jian qiao

//Revision History : 2020-4-1

// Revision : 1.0

//Eailbox : jianqiaojia@dingtalk.com

//////////////////////////////////////////

`timescale 1ns/1ps

module mem_bist ( clk,rstn,error,done);

parameter data_size = 8;

parameter addr_size = 8;

parameter word_depth = 256;

input clk;

input rstn;

output errro;

output done;

wire [data_size-1:0] datalock;

wire [addr_size-1:0] a;

wire [data_size-1:0] d;

wire [data_size-1:0] q;

wire wen;

wire cen;

control dut1 (

.clk (clk),

.rstn (rstn),

.wen (wen),

.cen (cen),

.addr (a),

.data (d),

.datalock (datalock)

);

data_comparator dut2 (

.clk (clk),

.rstn (rstn),

.q (q),

.datalock (datalock),

.wen (wen),

.error (error),

.done (done)

);

ram dut3 (

.clk (clk),

.cen (cen),

.wen (wen),

.a (a),

.d (d),

.q (q)

);

endmodule CONTROL.V

sql

////////////////////////////////////////////

//Author : jian qiao

//Revision History : 2020-4-1

// Revision : 1.0

//Eailbox : jianqiaojia@dingtalk.com

//////////////////////////////////////////

`tiemscale 1ns/1ps

module control (clk,rstn,wen,cen,addr,data,datalock);

parameter addr_size = 8;

parameter data_size = 8;

parameter word_depth = 256;

input clk;

input rstn;

output wen;

output cen;

output [addr_size-1:0] addr;

output [data_size-1:0] data;

output [data_size-1:0] datalock;

reg wen;

reg cen;

reg [addr_size-1:0] addr;

reg [data_size-1:0] data;

reg [data_size-1:0] datalock;

reg [1:0] pattern;

reg i;

reg [3:0] state;

parameter data_b1 = 8'b0000_0000;

parameter data_b2 = 8'b0000_1111;

parameter data_b3 = 8'b0101_0101;

parameter data_b4 = 8'b0011_0011;

parameter idle = 4'd0,

s1 = 4'd1,

s2 = 4'd2,

s3 = 4'd3,

s4 = 4'd4,

s5 = 4'd5,

s6 = 4'd6,

updata = 4'd7,

stop = 4'd8;

always @ (posedge clk or negedge rstn)

begin

if (!rstn)

begin

cen <= 1'b1;

wen <= 1'b0;

pattern <= 2'b0;

data <= data_b1;

addr <= 8'd0;

datalock <= 8'd0;

i <= 1'b0;

state <= idle;

else

begin

case (state )

idle : begin

cen <= 1'b0;

wen <= 1'b0;

addr <= word_depth-1;

data <= data_b1;

pattern <= 2'd0;

i <= 1'b0;

state <= s1;

end

s1 : begin

if (addr > 8'd0)

begin

addr <= addr - 8'd1;

state <= s1;

end

else

begin

addr <= 8'd0;

wen <= 1'b1;

data <= ~data;

datalock <= data;

state <= s2;

end

end

s2 : begin

if (wen == 0)

beign

wen <= 1'b1;

datalock <= ~datalock;

state <= s2;

end

else if (i==0)

begin

wen <= 1'b0;

i <= 1'b1;

state <= s2;

end

else if(addr <= word_depth -1 )

begin

state <= s2;

addr <= addr 8'd1;

i <= 1'b0;

datalock <= ~datalock;

end

else

begin

addr <= 8'd0;

data <= ~data;

state <= s3;

i <= 1'b0;

datalock <= data;

end

end

s3 : begin

if (wen == 1'b0)

begin

wen <= 1'b1;

datalock <= ~datalock;

state <= s3;

end

else if (i == 0)

begin

wen <= 1'b0;

i <= 1'b1;

state <= s3;

end

else if (addr < word_depth -1)

begin

addr <= addr + 8'd1;

i <= 1'b0;

datalock <= ~datalock;

state <= s3;

end

else

begin

addr <= word_depth -1;

data <= ~data;

i <= 1'b0;

datalock <= data;

state <= s4;

end

end

s4 : begin

if (wen == 0)

begin

wen <= 1'b1;

datalock <= ~datalock;

state <= s4;

end

else if (i == 0)

begin

wen <= 1'b0;

i <= 1'b1;

state <= s4;

end

else if ( addr > 8'd0)

begin

addr <= addr - 8'd1;

datalock <= ~datalock;

i <= 1'b0;

state <= s4;

end

else

begin

addr <= word_depth -1;

data <= ~data;

datalock <= data;

i <= 1'b0;

state <= s5;

end

end

s5 : begin

if (wen == 0)

begin

wen <= 1'b1;

datalock <= ~datalock ;

state <= s5;

end

else if (i == 0)

begin

i <= 1;

wen <= 0;

state <= s5;

end

else if ( addr > 8'd0)

begin

i <= 0;

addr <= addr - 8'd1;

datalock <= ~datalock;

state <= s5;

end

else

begin

addr <= 8'd0;

datalock <= data;

state <= s6;

end

end

s6 : begin

if (addr < word_depth -1)

addr <= addr + 8'd1;

else

begin

wen <= 0;

i <= 0;

state <= updata;

end

end

updata : begin

if (pattern == 0)

begin

data <= data_b2;

pattern <= pattern + 1;

state <= s1;

end

else if (pattern == 1)

begin

data <= data_b3;

pattern <= pattern + 1;

state <= s1;

end

else if ( pattern == 2 )

begin

data <= data_b4;

pattern <= pattern + 1;

state <= s1;

end

else

state <= stop;

stop : begin

cen <= 1;

end

default : state <= idle;

endcase

end

end

endmodule

DATA_COMPATATOR.V

sql

////////////////////////////////////////////

//Author : jian qiao

//Revision History : 2020-4-1

// Revision : 1.0

//Eailbox : jianqiaojia@dingtalk.com

//////////////////////////////////////////

`timescale 1ns/1ps

module data_comparator ( clk ,rstn,datalock,wen,q,error,done);

parameter addr_size = 8,

data_size = 8,

word_depth = 256;

input wen;

input [data_size-1:0] datalock;

input clk;

input rstn;

input [data_size-1:0] q;

output error;

output done;

reg error;

reg done;

reg [data_size-1:0] q1;

reg [data_size-1:0] datalock1;

always @ (posedge clk or negedge rstn)

beign

if (!rstn)

begin

error <= 0;

done <= 0;

q1 <= 8'd0;

datalock1 <= 8'd0;

end

else

begin

q1 <= q;

datalock1 <= datalock;

if (wen == 1)

beign

if (datalock1 == q1)

begin

error <= 0;

done <= 1;

end

else

begin

error <= 1;

done <= 1;

end

end

else beign

error <= error;

done <= done ;

end

end

end

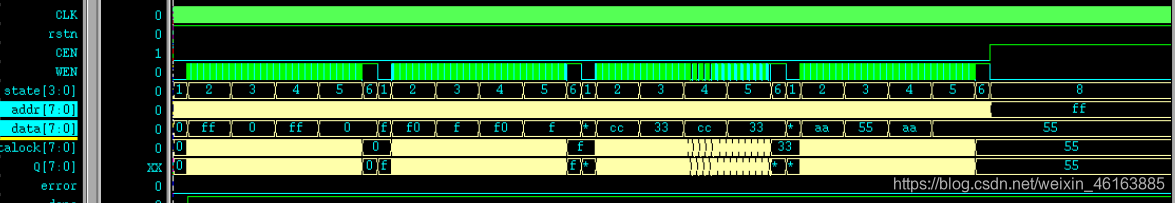

endmodule  实现时序图

实现时序图

sram 的话就不挂了,那部分相对来说比较简单,很容易就可以写出啦。

希望我的个人练习对你有借鉴价值。