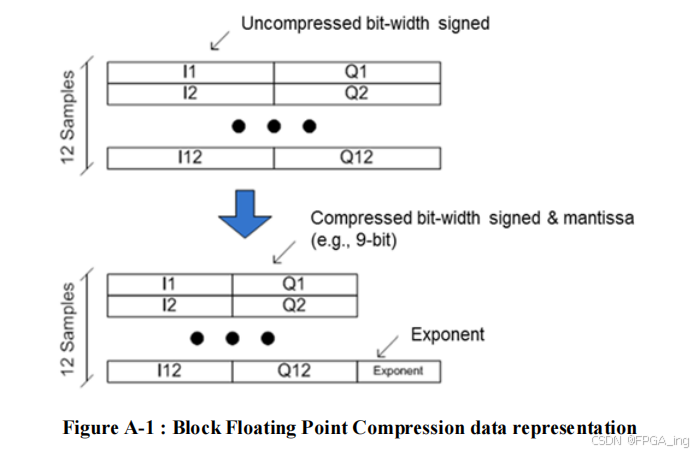

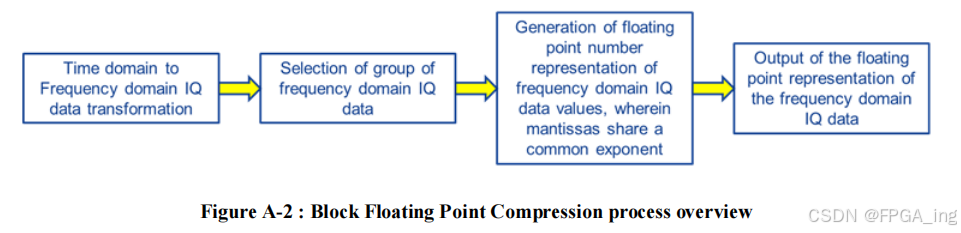

整个算法设计基于ORAN协议中的BFP压缩算法;

对于压缩处理,首先记录无符号最大值的最高有效位(0~14),

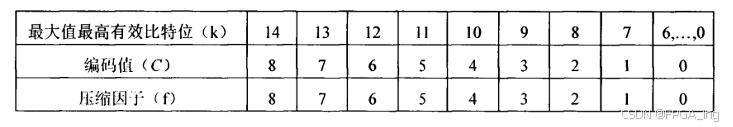

根据最高有效比特位确定压缩处理过程中的压缩因子;

压缩处理过程用于完成对数据的压缩,输出压缩因子;

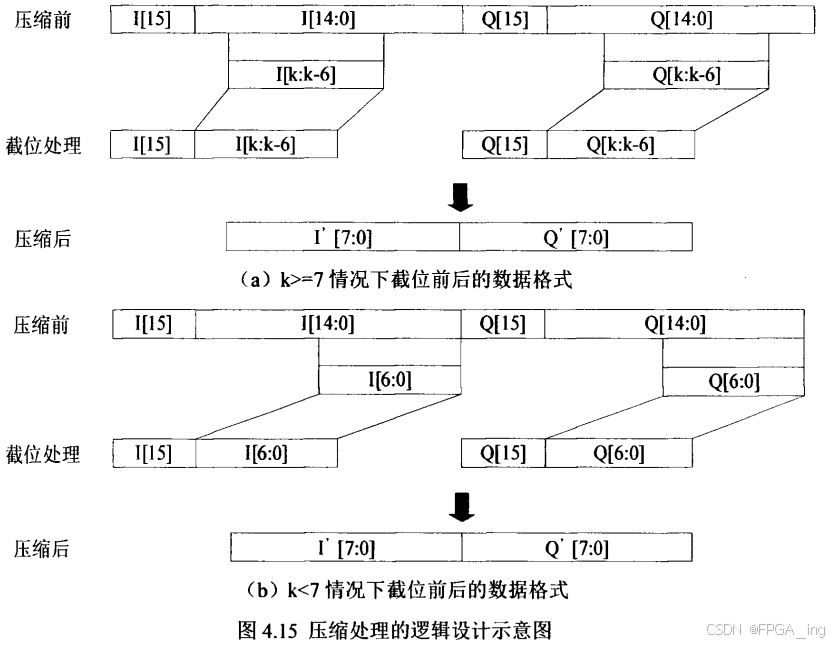

并根据最大值最高有效比特位,对原始数据 I,Q值进行截位处理,

当最大值的最高有效比特位不小于7时,压缩因子为K-6;

当最大值的最高有效比特位小于7时,压缩因子=0;

最大值编码及压缩因子格式表:

压缩算法的实现本质上是进行截位处理,以最高有效比特位K为界限,如果K>=7,保留符号位,其余位为[k:k-6];

如果K<7 则保留符号位取最低7位,进行拼接;

如果Q15的格式,那么最高有效位为bit14;

以BFP-8bit为例,则 I = {I[15],I[14:8]} + i_carry_bit;

FPGA实现(BFP-8bit):

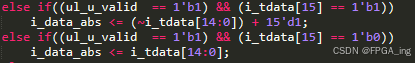

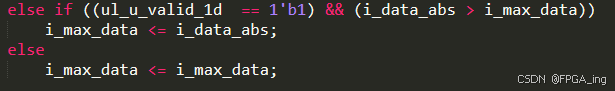

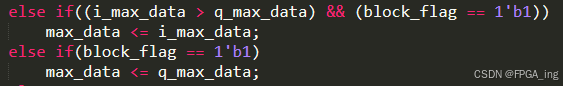

计算 I Q 绝对值的最大值;

首先需要 计算 I 和 Q的绝对值,比较 I Q 绝对值取最大值,对最大值进行计算求压缩因子;

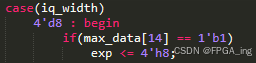

计算压缩因子(数据位宽16位,最高位为符号位,从次高位开始依次往下递减,

压缩因子计算公式为 log2(2^k)-6),以压缩因子等于8为例:

计算截位的近似值(因为压缩的本质是截位,对于BFP-8bit,需要截取低8位[7:0]):

判断符号位为正或者负,

为正:

直接取第(压缩因子-1)位比特位,采用标准的四舍五入;

以压缩因子等于8 为例:

低8位的数值范围:0-255;

舍入边界:128(0.5 * 256);

低8位 >= 128 → 进位到高8位;

低8位 < 128 → 直接截断;

为负:

采用向零舍入;

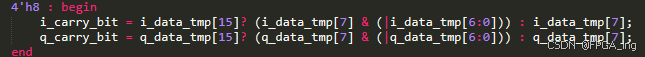

整个逻辑需要满足(以压缩因子等于8 为例):

-

低8位的最高位为1(bit7 = 1);

-

低7位不全为0,至少有一个1;

对于负数,只有当低8位 > 128时才进位;

低8位 > 128 → 进位 (使绝对值变小)

低8位 = 128 → 不进位 (保持)

条件分解:

- rd_i_data_temp[7] = 1:低8位 >= 128

- |rd_i_data_temp[6:0] = 1:低7位至少有一个1

两者同时成立:低8位 > 128(不是等于128)

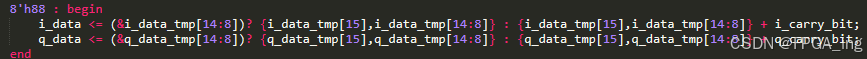

对于数据最后的输出:

根据 IQ 位宽和压缩因子进行数据压缩;

关键点是:数据最低有效比特位是与压缩因子对应;

判断取的数据位如果等于0:表示数据没有达到表示范围的最大值,需要加进位;

判断取的数据位如果等于1:说明数据已经达到该表示范围的最大值,则不加进位,防止溢出;

直接进行数据拼接,即符号位拼接数据部分,

数据部分则是以压缩因为的值作为数据最低有效比特位,向上取6位;

最终得到8比特的结果为:{一位符号位,七位数据位};

最后拼接 IQ 输出;

以压缩因子等于8,iq位宽等于8为例:

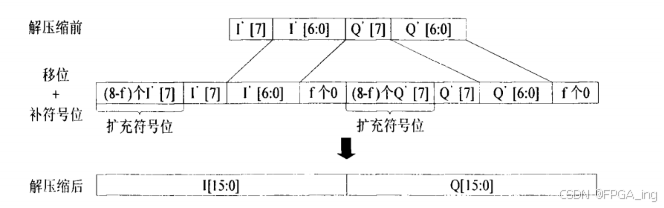

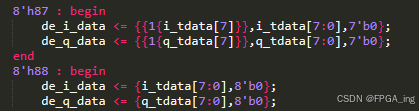

解压缩是将8比特的 I Q 数据解压为16比特,根据压缩因子对数据进行移位操作;

解压缩过程:

根据压缩因子,得到需要补零的个数,再用 iq位宽减去补零的个数,就可以得到高位扩充符号位的个数;

举例:

压缩因子=7,那么数据需要低位补7比特0,高位(8-7)扩充符号位1位,即可实现解压缩;

压缩因子=8,数据直接补8比特0,即可

BFP-8bit 解压缩:以iq位宽等于8;压缩因子等于7和等于8为例

以上就能够实现BPF-8bit的压缩和解压缩;