No.26 基于FPGA的cordic算法实现,输出sin和cos波形(quartusii版本),包括程序操作录像,算法程序 CORDIC为Coordinate rotation digital computer的缩写,来自于J.E.Volder发表于1959年的论文中,是一种不同于"paper and penci\"思路的一种数字计算方法,当时专为用于实时数字计算如导航方程中的三角关系和高速率三角函数坐标转换而开发。 如今看来,CORDIC非但没有局限于以上方面,反而在各个数字计算如信号处理、图像处理、矩阵计算、自动控制和航空航天等各领域获得了广泛的使用并成为了各行业不可替代的基石。 所谓万物皆可信号处理,信号处理相关行业的各位与CORDIC自然难舍难分。 又所谓"为人不识CORDIC,读尽算法也枉然",CORDIC算法并不新鲜.今天老生常谈下CORDIC算法,尽量将每一步公式的变换展示清楚,希望对新手有用。 1.软件版本 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 2.运行方法 使用Quartusi18.0版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。 工程路径必须是英文路径。 具体操作观看提供的程序操作视频跟着操作。 视频播放使用windows media plaver播放。

CORDIC算法,全称是Coordinate Rotation Digital Computer,由J.E.Volder在1959年提出,最初用于实时数字计算,特别是在导航方程中的三角函数关系和高速率三角函数坐标转换。如今,CORDIC算法已经不仅仅局限于导航领域,它在信号处理、图像处理、矩阵计算、自动控制和航空航天等领域都有广泛应用。

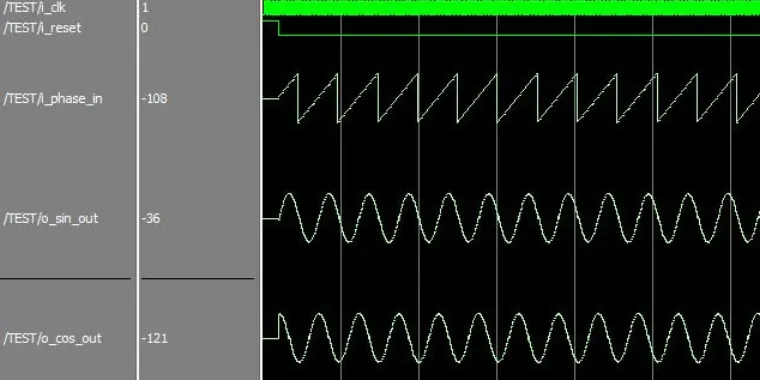

CORDIC算法的核心思想是通过一系列的移位运算和加减运算来实现复杂的数学计算,而无需使用乘法器,这在资源受限的硬件环境中非常有用。今天,我们来探讨一下如何在FPGA上实现CORDIC算法,并输出sin和cos波形。

**软件版本**

- Quartus II 18.0

- ModelSim-Altera 6.6d Starter Edition

**CORDIC算法概念**

CORDIC算法主要通过迭代的方式来计算三角函数、坐标旋转等操作。以计算sin和cos为例,其核心是通过一系列的渐近旋转操作,将输入的角度旋转到接近0的位置,同时记录每次旋转的角度累加值,最后得到sin和cos的值。

公式上,CORDIC的迭代过程可以表示为:

\[

x*{n+1} = x* n - yn \cdot \text{sign}(yn \cdot \theta_n)

\]

\[

y*{n+1} = y* n + x*{n+1} \cdot \text{sign}(y*n \cdot \theta_n)

\]

其中,\\theta_n 是第n次迭代的角度,\\text{sign} 是符号函数。

**CORDIC算法实现步骤**

- 计算旋转角:将目标角度分解为一系列已知的渐近角度(如2\^{-1}, 2\^{-2}, 2\^{-3}, \\dots)。

- 迭代计算:按照分解后的角度,依次进行坐标旋转。

- 波形输出:将计算得到的sin和cos值通过FPGA的输出端口输出,通过示波器观察波形。

**FPGA设计思路**

在Quartus II中,我们可以通过IP核生成CORDIC核心模块,然后通过HDL(硬件描述语言)进行配置。具体步骤如下:

- IP核搭建 :

- 打开Quartus II,创建一个新的FPGA工程。

- 通过菜单栏的

IP->Core Generator,选择CORDIC IP核。 - 配置IP核的参数,如功能选择(旋转模式)、数据位宽等。

- HDL代码实现 :

- 将生成的CORDIC IP核模块实例化到顶层模块中。

- 添加控制信号(如时钟、复位、启动信号)和数据输入输出接口。

- 顶层模块连接 :

- 将CORDIC模块的输入输出与外部接口(如LED、PWM或串口)连接,方便调试和验证。

**代码分析**

以下是一个简化的CORDIC IP核模块和顶层模块的代码示例:

**CORDIC IP核配置(部分代码)**

verilog

// CORDIC IP核实例化

CORDIC myCORDIC (

.clk(clk),

.rst(rst),

.start(start),

.theta(theta),

.x_out(x_out),

.y_out(y_out),

.done(done)

);**顶层模块(部分代码)**

verilog

module top_module (

input wire clk,

input wire rst,

input wire [15:0] theta,

output reg [15:0] x_out,

output reg [15:0] y_out,

output reg done

);

// CORDIC模块实例化

CORDIC myCORDIC (

.clk(clk),

.rst(rst),

.start(start),

.theta(theta),

.x_out(x_out),

.y_out(y_out),

.done(done)

);

// 控制逻辑

always @(posedge clk) begin

if (rst) begin

start <= 1'b0;

end else begin

if (!done) begin

start <= 1'b1;

end else begin

start <= 1'b0;

end

end

end

endmodule这段代码展示了如何将CORDIC IP核与顶层模块连接,并通过简单的状态机控制CORDIC的启动和复位。

**运行和验证**

- 工程编译 :

- 将上述代码和生成的CORDIC IP核添加到工程中。

- 进行编译,确保没有语法错误和时序违例。

- 波形输出 :

- 通过ModelSim运行仿真,观察CORDIC的输出波形。

- 将仿真通过的代码下载到FPGA开发板,使用示波器观察实际输出的sin和cos波形。

**总结**

CORDIC算法虽然看似简单,但在FPGA实现中需要仔细考虑时序和资源的优化。通过本文的介绍,希望读者能够理解CORDIC算法的基本原理,并能够根据实际需求,灵活调整代码和配置参数。

如果有任何问题或需要进一步的探讨,欢迎留言交流!