目录

[2. 通过约束压缩比特流文件](#2. 通过约束压缩比特流文件)

记录目的:优化远程维护及在轨重构效率。由于比特流大小直接挂钩 Flash 烧录带宽与 FPGA 配置耗时,本项研究聚焦于"码流压缩"技术。核心目标是通过缩减文件规模,提升数据链路利用率,并缩短系统重新上电后的配置响应时间。

1.常见的码流文件

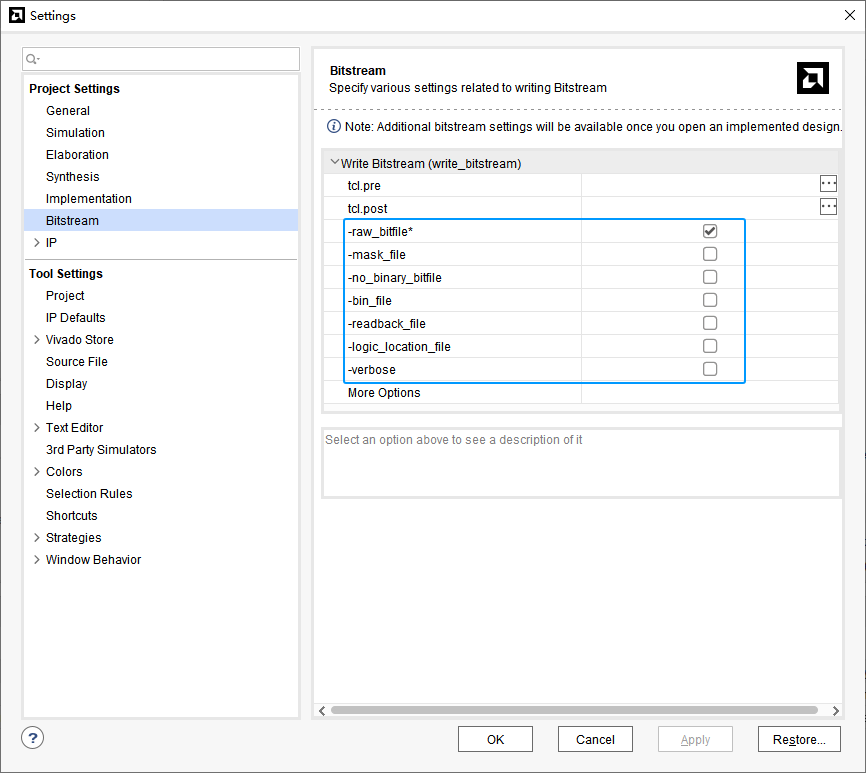

vivado可以导出不同的码流文件,如下图所示:

常见的码流说明如下:

| 文件后缀 | 名称 | 格式 | 包含内容 | 主要用途 |

|---|---|---|---|---|

| .bit | Bitstream 文件 | 二进制 | 含文件头(芯片型号、创建日期等)+ 逻辑配置数据 | 默认格式。用于 Vivado JTAG 直接下载到 FPGA 内部(掉电丢失)。 |

| .bin | Binary 文件 | 二进制 | 纯配置数据(无文件头) | 常用。用于 SPI/BPI Flash 烧录。其起始位置就是第一条配置指令。 |

| .rbt | Raw Bit 文件 | ASCII 文本 | 十六进制/二进制文本 + 文本文件头 | 调试用。可以用记事本打开。你的压缩工具通常要求此格式作为输入。 |

| .msk | Mask 文件 | 二进制 | 屏蔽位信息 | 用于验证码流。区分配置数据中哪些是常数,哪些是会随运行变化的(如回读校验)。 |

| .mcs | PROM 文件 | ASCII (Intel Hex) | 带校验和的配置数据 | 传统的 ISE 时代文件格式,用于固化到外部 PROM/Flash。 |

其中,.bit和.bin文件都可以通过JTAG下载。.rbt文件用于772所的压缩文件功能。其他的码流形式很少用到。

2. 通过约束压缩比特流文件

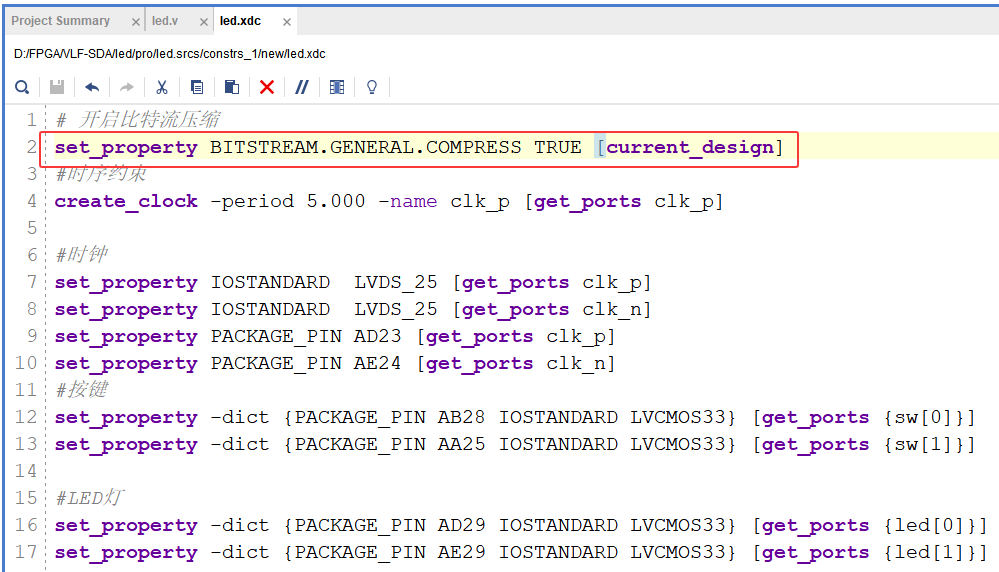

在 Vivado 中,可以通过在 .xdc 文件中添加以下约束来启用压缩功能。XDC 约束代码:

# 开启比特流压缩

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]-

原理:Vivado 使用多帧写(Multi-frame Write)技术。当发现多个配置帧(Frame)的内容完全一致时,比特流指令会指示 FPGA :"将这一份数据同时写入以下 N 个地址"。

-

预期效果 :通常能减小 30% - 60% 的文件体积。

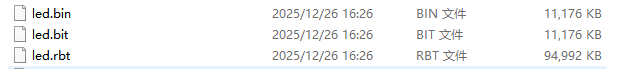

通过开启压缩约束,对比了同一份工程生成的比特流大小变化:

压缩前:

压缩之后:

可以看得到压缩效果还是很厉害的,减少了91%左右的文件体积。

以上就是本次笔记的记录。