前言

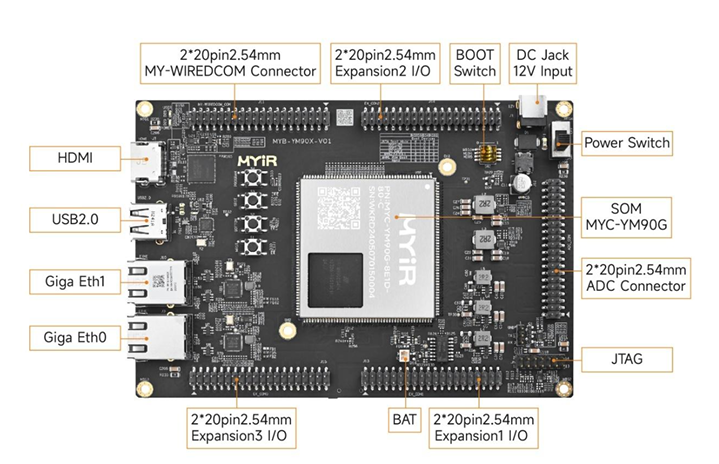

在嵌入式系统开发过程中,开发板的选择往往决定了项目的效率与可扩展性。米尔的 MYD-YM90X 开发板作为一款异构架构平台,集成了高性能处理器与 FPGA 核心,为开发者提供了灵活的硬件设计与应用开发环境。本次测评文章将结合个人的开发过程,围绕硬件设计、应用代码移植以及 FPGA 的实际使用进行分享。

开发板简介

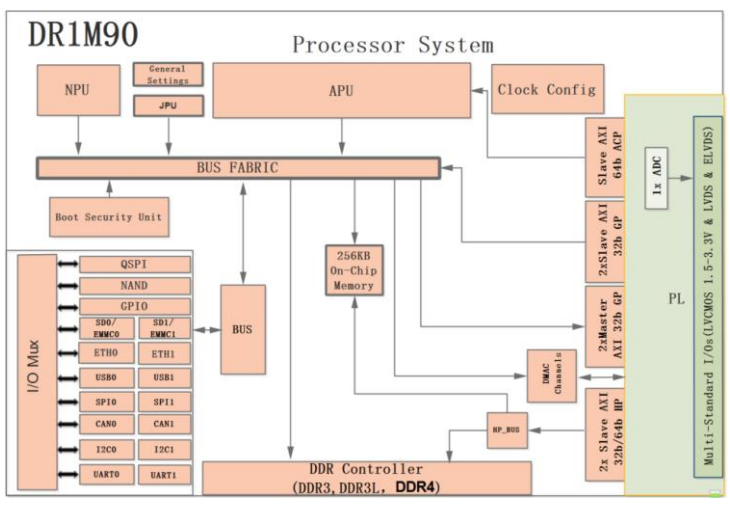

MYD-YM90X 开发板采用异构架构设计,具备以下特点:

- 处理器与 FPGA 协同工作:主控 SoC 提供通用计算能力,FPGA 核心则用于定制化逻辑处理。

- 丰富的外设接口:支持多种通信接口,适合工业控制与信号处理场景。

- 官方文档支持:米尔提供了详细的硬件手册与软件移植指南,降低了开发门槛。

项目背景与问题

在本次开发过程中,目标是对机器编码器信号进行采集与处理。然而实际测试中发现,编码器信号存在明显毛刺,导致数据不稳定,影响后续控制逻辑。传统的软件滤波方法在 MCU 上实现时,存在延迟与资源占用问题,难以满足实时性需求。

FPGA 滤波方案设计

为解决上述问题,我选择利用开发板上的 FPGA 核心来实现滤波逻辑。具体设计思路如下:

- 信号采集:通过 GPIO 接口将编码器信号输入 FPGA。

- 滤波逻辑实现:在 FPGA 内部编写 Verilog/VHDL 模块,采用滑动窗口与去抖动算法对输入信号进行实时处理。

- 结果输出:滤波后的稳定信号再传递给主控处理器,用于后续的运动控制与数据分析。

这种硬件级滤波方式相比软件实现具有以下优势:

- 实时性强:FPGA 并行处理能力保证了信号的快速响应。

- 资源占用低:主控 CPU 不再承担滤波任务,释放了计算资源。

- 灵活可扩展:滤波算法可根据需求在 FPGA 中灵活调整。

应用代码移植与开发

在软件层面,开发过程主要包括以下几个环节:

- 驱动移植:根据官方文档提供的参考代码,将 FPGA 输出信号的驱动接口移植到 Linux 系统中。

- 应用层开发:编写用户态程序,调用驱动接口获取滤波后的编码器数据,并进行实时显示与记录。

- 测试验证:通过示波器与逻辑分析仪对比滤波前后的信号,验证 FPGA 滤波效果。

在移植过程中,官方文档提供的 设备树配置示例 与 驱动框架说明起到了关键作用,使得硬件与软件的衔接更加顺畅。

c

// 对输入信号进行多周期采样,只有在稳定时才更新输出

module encoder_filter (

input wire clk, // FPGA 时钟

input wire rst_n, // 复位信号,低电平有效

input wire encoder_in, // 原始编码器输入信号(带毛刺)

output reg encoder_out // 滤波后的稳定信号

);

// 参数:连续多少个周期稳定才认为有效

parameter STABLE_COUNT = 8;

reg [3:0] counter; // 计数器

reg encoder_sync; // 同步寄存器

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

encoder_sync <= 1'b0;

encoder_out <= 1'b0;

counter <= 4'd0;

end else begin

// 将输入信号同步到时钟域

encoder_sync <= encoder_in;

// 如果输入与当前输出一致,计数器清零

if (encoder_sync == encoder_out) begin

counter <= 4'd0;

end else begin

// 输入与输出不一致时,计数器累加

counter <= counter + 1'b1;

// 当计数器达到阈值时,更新输出

if (counter >= STABLE_COUNT) begin

encoder_out <= encoder_sync;

counter <= 4'd0;

end

end

end

end

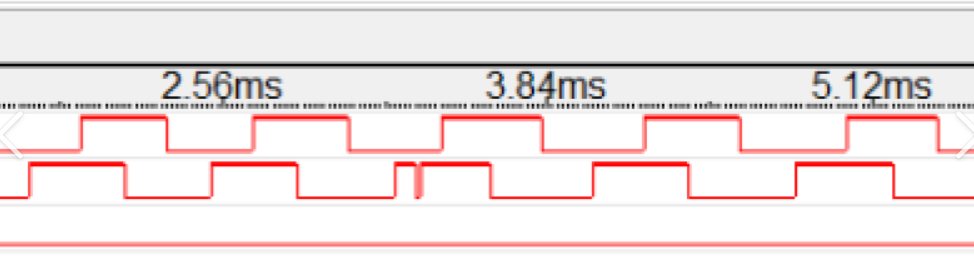

endmodule测试结果与分析

经过多轮测试,滤波后的编码器信号明显更加平稳,毛刺大幅减少,控制系统的稳定性得到提升。以下是测试总结:

- 滤波前:信号存在频繁抖动,导致位置计数不准确。

- 滤波后:信号边沿清晰,计数结果稳定,满足实时控制需求。

总结与展望

通过本次开发实践,米尔 MYD-YM90X 开发板展现了其在异构架构与 FPGA 应用方面的优势。硬件滤波方案不仅解决了编码器信号毛刺问题,也为后续的复杂信号处理提供了可扩展的思路。未来,我计划进一步探索以下方向:

- 在 FPGA 中实现更复杂的数字滤波算法,如 FIR/IIR 滤波器。

- 将滤波模块与运动控制逻辑结合,实现更高精度的闭环控制。

- 探索 MYD-YM90X 在其他工业场景中的应用,如传感器融合与高速数据采集。

本次测评文章希望能为其他开发者在使用 MYD-YM90X 开发板时提供参考与启发。