1.1 项目简介

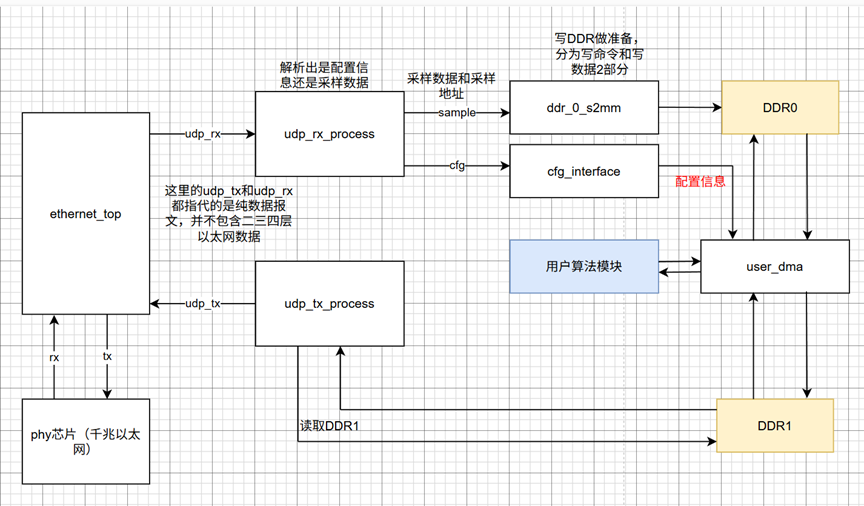

项目的基本流程是用户使用上位机通过UDP包下发数据到FPGA。FPGA将数据分批次传输到用户的算法模块。待算法模块处理完成后,通过UDP包上送至上位机。应用平台基于优数科技的PCIe-404信号处理卡,采用国产的690T FPGA芯片。

1.2 项目架构

1.2.1 基本流程

- 上位机下发数据

(1) 上位机下发基础配置信息

(2) 上位机下发数据信息

- 数据到达FPGA侧,FPGA进行处理

(1) FPGA将配置信息存入cfg_interface

(2) FPGA将数据内容写入DDR0

(3) 写入DDR0后,FPGA向上位机发送写DDR0完成标志

- 上位机收到返回的写DDR0完成标志,下发配置信息。从DDR0读取数据至用户算法模块

(1) FPGA按帧读取数据至用户算法模块

(2) 算法模块处理1帧完成后,处理后的信息写入DDR1

(3) 用户处理完成1帧完成后,FPGA才允许读下一帧到用户算法模块

-

用户算法模块将所有内容处理完成,FPGA向上位机返回写DDR1完成标志

-

上位机收到写DDR1完成标志后,下发读DDR1配置信息

-

FPGA收到读DDR1配置信息,发起读DDR1命令,传送至上位机。

1.3 调试问题

1.3.1 上位机丢包

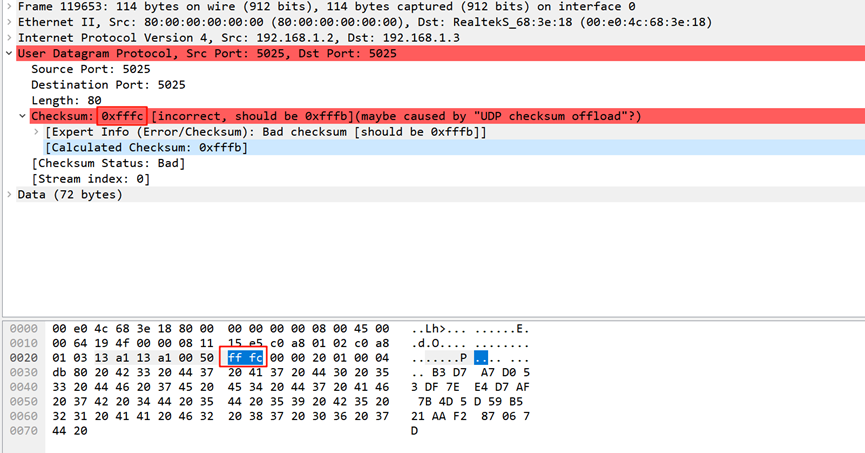

发送200M数据,在上位机侧QT侧发现少收到数据。用wireshark抓包发现丢包以发送至PC端,进一步开启wireshark的checksum校验,发现丢包是由于checksum错误导致的。

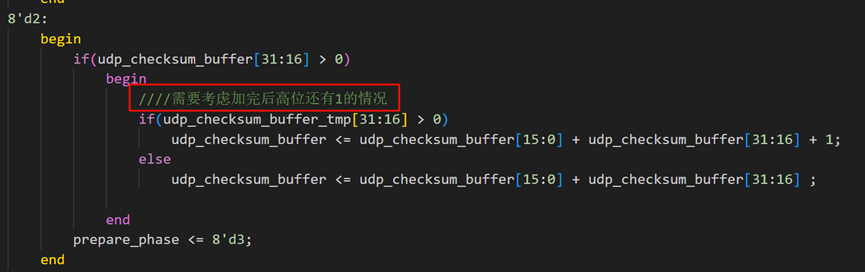

进一步分析,发现checksum错误时,我计算的值始终比正确值大1.

分析逻辑代码,发现由checksum计算在边界处少加1导致的。修改如下:

1.3.2 FPGA侧丢包

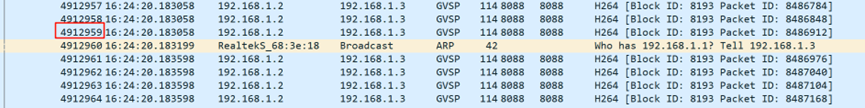

在PCIE404的回环测试实验中,发现上位机收到报文存在异常。用wireshark抓包发现,这些报文的确正常发送了。进一步分析,发现当下发时,如果1个udp包后面紧跟着1个arp包,那么回环后收到的数据大概率是错的。

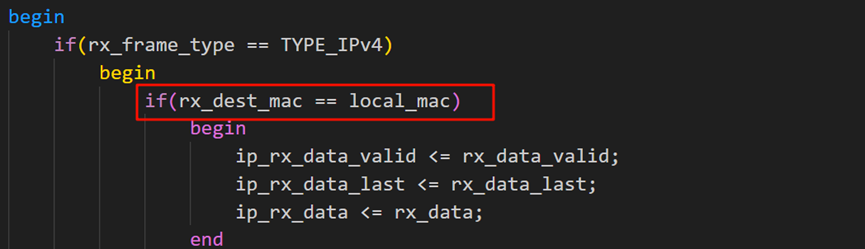

分析代码,发现FPGA内时根据mac地址确定是否为需要处理的udp包的。此逻辑在大压力下存在异常,当两个包相邻近时,发现会存在mac地址与原数据不匹配的现象。

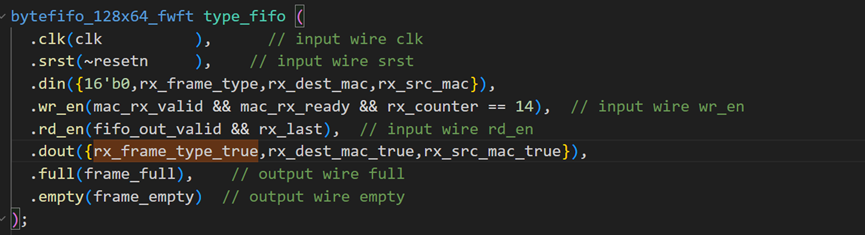

因此,在顶层利用FIFO缓存相关mac信息,FIFO预读1拍,确保时序对应正确。

1.3.3 算法模块连续性

用户要求输入算法模块的数据必须连续,不能中断。

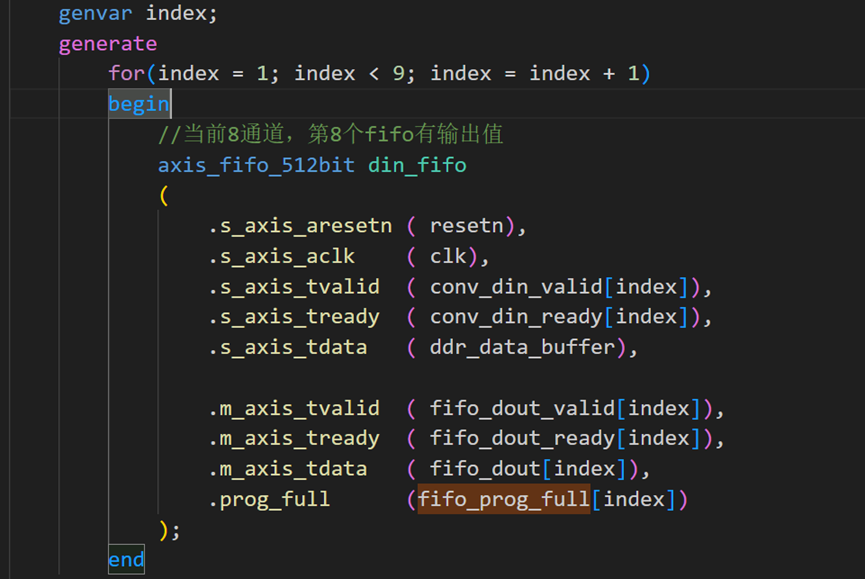

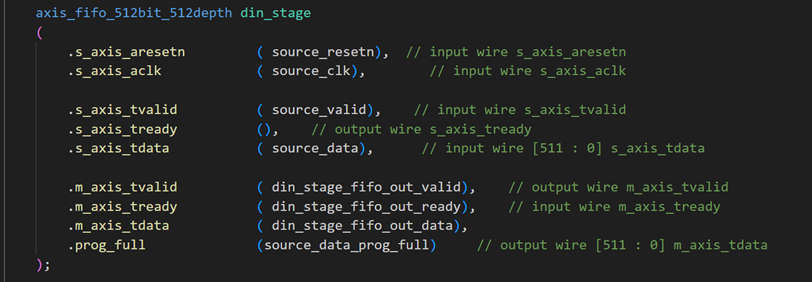

初步设想如下:通过突发读DDR来保证连续与带宽平衡。例如,DDR接口位宽为512bit,用户接口位宽为128bit.突发为16。那我只需要每64个周期发送1个突发为16的ddr读命令就可以保证连续了。

但是,实际测试发现,DDR返回的数据有快有慢,即使我调整到每16个周期发送1个突发为16的ddr读命令。仍概率性的不连.所以,利用周期性发送突发读命令来保证数据连续是不现实的。因此,修改为方案2.

方案2如下:必须存在1个FIFO,将一次性进入用户的数据进行缓存。缓存完毕之后,在连续向用户发送,这样就能保证连续性了。

此FIFO可以根据用户的数据情况进行调整。

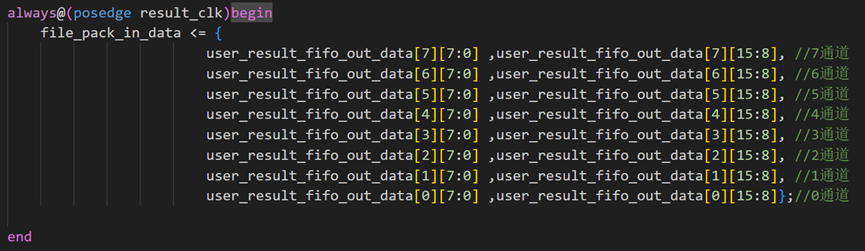

1.3.4 大小端问题

通过千兆以太网下发到FPGA的数据为小端模式。需要在小端模式下进一步调整,适应用户算法模块的数据

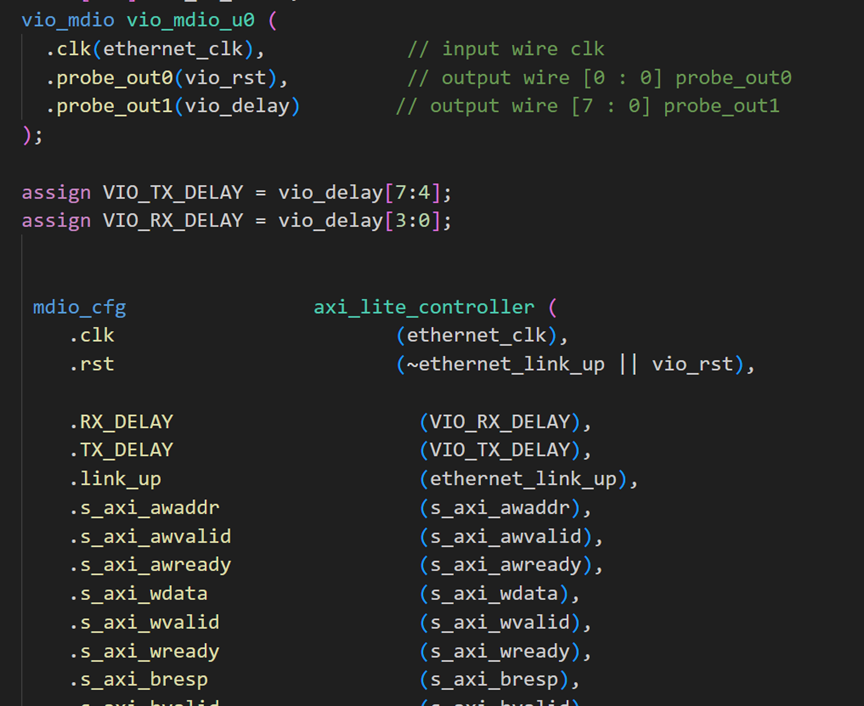

1.3.5 MDIO控制

针对不同的板卡,需要控制千兆以太网PHY的不同的rx_delay和tx_delay。可以在一定程度上解决FPGA侧或上位机侧的误码问题。当前版本支持通过axi_lite接口取控制以太网phy的rxdelay,txdelay。

1.4 优化点

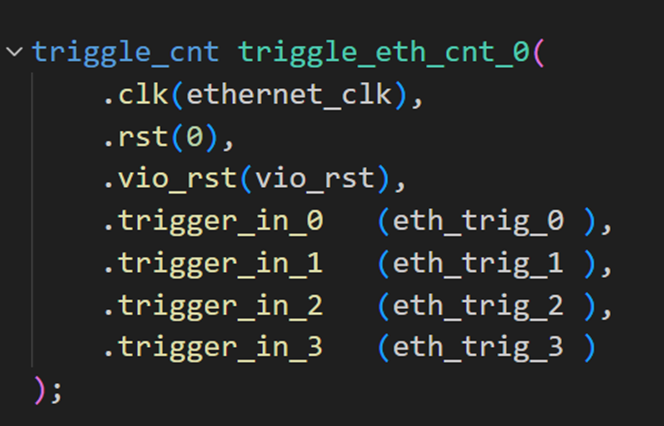

1.4.1 调试接口

补充了关键模块的输入输出计数,便于分析数据流走向和定位问题。如下,通过trigger_cnt读取模块计数。后续可通过继续优化,通过上位机读取fpga内数据状态和计数。

1.4.2 反压逻辑

原架构考虑了普通流量的情况,部分FIFO没有反压信号。未考虑大压力下FIFO可能会挂死。对此处进行优化。确保反压控制逻辑正确性。