使用优数科技的PCIe-404信号处理卡,上位机接收数据时,遇到UDP数据丢包问题。

1.1 丢包原因分析

1.网络层原因:

网络拥堵:路由器或交换机缓冲区满,导致数据包被丢弃。

链路质量差:无线网络不稳定或物理链路问题。

带宽不足:发送速率超过链路承载能力。

2.系统层原因:

操作系统缓冲区满:接收端处理速度慢,导致内核缓冲区溢出。

防火墙或安全软件拦截:某些安全规则可能丢弃UDP包。

资源限制:系统资源(如内存、CPU)不足,影响网络栈处理能力。

3.应用层原因(QT相关):

接收端处理延迟:QUdpSocket的readyRead信号处理太慢,未及时读取数据。

单线程处理瓶颈:在主线程中处理大量UDP数据,导致界面卡顿和丢包。

缓冲区设置不合理:未使用setSocketOption调整接收/发送缓冲区大小。

数据包大小超过MTU:导致IP分片,增加丢失概率。

4.多线程竞争:多个线程同时操作同一个QUdpSocket实例,导致问题。

协议本身限制:

UDP无重传机制:不保证可靠交付。

缺乏流量控制:发送方可能发送过快。

1.2 问题点&解决办法

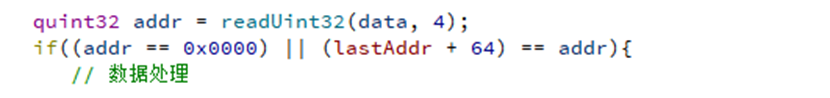

排查思路排查FPGA回传到上位机的数据是否由丢包,可通过wireshark抓包工具查看。数据回传的数据格式为4字节协议头,4字节数据地址位,64字节有效数据。每发一包数据地址位加64,通过检测地址位是否连续,判断数据是否丢包。

经排查FPGA不一定将数据全部发送过来,那么丢包原因就有QT上位机接收丢包和FPGA发送丢包两种可能。

1.2.1 上位机接收丢包解决方法

1.将数据接收和数据处理放入线程中单独处理。

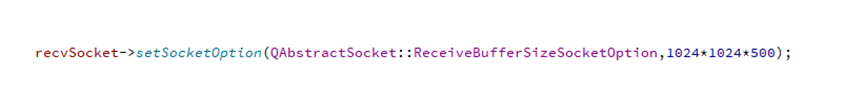

问题点:QT的UDP默认接收缓冲区大小为64KB,接收缓冲区太小可能造成数据溢出。

解决办法:增大缓冲区,将缓冲区设置为500MB

2.关闭主机防火墙

1.2.2 FPGA发送丢包解决方法

FPGA发送数据丢包这个问题需要上位机来做丢包检测,因为FPGA做丢包检测太繁琐,

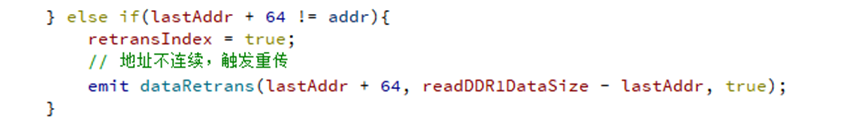

解决办法:增加数据重传机制,判断接收数据地址是否连续,若连续则进行数据处理,反之发送丢失数据的地址给FPGA,进行重传。

关键处理步骤:

当检测到地址不连续时将丢包的地址和剩下接收的数据长度发送给FPGA,FPGA接收到重传标志后,将从丢包的地址开始发送数据。

当重传机制触发后清除接收缓冲区的内容,减少无效地址的判断减小资源开销。

1.3 软件运行

经过以上处理后,FPGA发送的数据能够全部被上位机接收。若中间有丢包也可通过重传机制重新获取丢失的数据。缓冲区增加到足够大数据不会溢出。