基于UDP的FPGA可靠传输与丢包重传机制设计

-

- 背景与问题

使用优数科技的PCIe-404信号处理卡,采用UDP协议与FPGA进行高速数据传输。虽然UDP具备低延迟、无连接的优势,但在网络不稳定或拥堵时,丢包问题不可避免。为保证数据的完整性与可靠性,我们设计并实现了一套基于地址连续检测的丢包重传机制。

-

- 数据帧格式说明

每帧UDP数据包结构如下:

|------|--------|-----------|

| 组成部分 | 大小(字节) | 说明 |

| 协议头 | 4 | 协议类型 |

| 数据地址 | 4 | 当前数据起始地址 |

| 有效数据 | 64 | 实际传输的数据内容 |

地址递增规则:每成功发送一包数据,地址值增加 64,即下一包数据的起始地址。

-

- 丢包检测与重传机制

- 检测逻辑

- 丢包检测与重传机制

接收端持续监听数据包,并提取第 4~7 字节(即"数据地址"字段),判断其连续性:

1)正常情况: 若地址为 0(首包),或地址等于 lastAddr + 64,则更新 lastAddr 为当前地址。

2)丢包情况:若地址不等于 lastAddr + 64,则判定为丢包。

此时,向FPGA发送重传请求,包含:

请求起始地址:lastAddr + 64,剩余待读取数据长度

-

-

- 重传触发与缓冲区管理

-

一旦触发重传机制,接收端会立即清空当前接收缓冲区,避免因残留乱序数据导致重复判断,从而降低系统资源开销。

-

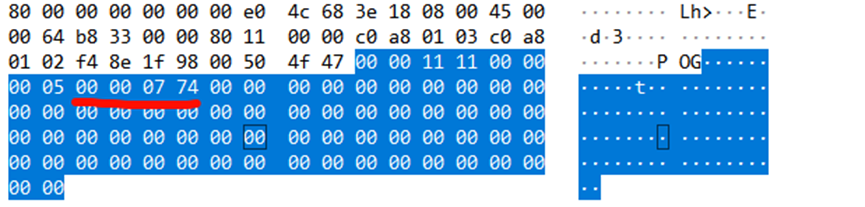

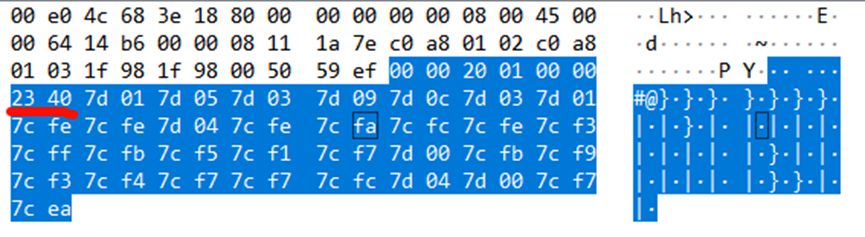

- 丢包处理流程示例

以下模拟一次丢包发生时的处理过程:

检测丢包

接收端发现当前地址为 0x00002380,而上一包地址为 0x00002300,两者差值不为 64,判定 0x00002340 数据包丢失。

发送重传请求

上位机向FPGA发送重传请求,要求重传从 0x00002340 开始的数据。

FPGA响应重传

FPGA收到请求后,从指定地址重新发送数据包,确保数据连续性恢复。

-

- 总结

通过地址连续性检测与主动重传机制,我们成功在UDP协议上实现了可靠数据传输,有效应对网络不稳定导致的丢包问题。该机制具有以下优点:

- 轻量高效:仅通过地址判断,无需复杂握手协议

- 资源友好:及时清空缓冲区,避免无效数据处理

- 适用性强:尤其适合FPGA与上位机之间的高速数据流场景