本博文主要交流设计思路,在本博客已给出相关博文约160篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。

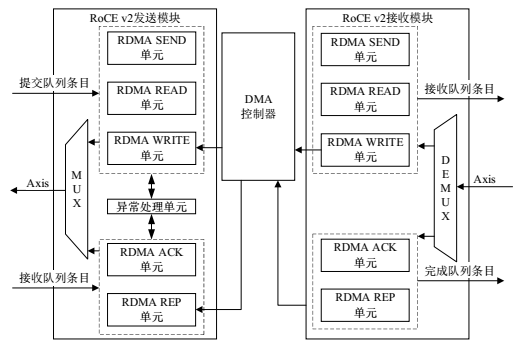

与 RoCE v2 发送模块类似,接收模块由五个接收单元和一个 DEMUX 组成。但是工作流程与 RoCE v2 发送模块略有不同,由于网络包必定逐个到达,所以接收模块不再依赖状态机进行工作。同理,模块接收入口处不会存在拥塞,入口处不再需要设置缓存。接下来将对接收模块中的五个接收单元的设计进行具体分析。

SEND 单元:当接收到来自远程主机的 SEND 包后,SEND 单元将解析 SEND 数据包中的远程主机信息,并存储到队列管理模块的寄存器中,而后生成接收队列条目并写入接收队列。

READ 单元:当接收到来自远程主机的 READ 包后,READ 单元将解析 READ数据包中的请求数据地址,请求数据长度及远程访问密钥,并与队列管理模块中的寄存器进行对比。对比通过,则生成正常接收队列条目,写入接收队列;若对比不通过,则生成异常接收队列条目,写入接收队列。

WRITE 单元:当接收到来自远程主机的 WRITE 包后,WRITE 单元将解析 WRITE数据包中的数据写入地址,写入数据长度及远程访问密钥,并与队列管理模块中的寄存器进行对比。若对比通过允许写入,则将这些参数及数据一并移交 DMA 控制,将数据写入内存;若对比失败,则忽略数据。同时根据对比结果,生成对应的正常或异常接收队列条目。

ACK 单元:当接收到来自远程主机的 ACK 包后,ACK 单元将解析 ACK 数据包。若 ACK 包中的各个字段符合成功传输的定义,则生成正常完成队列条目,将完成队列条目写入完成队列中;反之则生成异常完成队列条目。

REP 单元:当接收到来自远程主机的 REP 包后,REP 单元将解析 REP 数据包,并根据解析出的信息(包序列号)寻找相应的发送队列任务,而后根据发送队列任务中的信息,将数据移交给 DMA 控制器。当数据全部接收完毕后,生成完成队列条目。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望