一、名词简介

1.FPGA是什么

FPGA是一种可以通过编程来修改其逻辑功能的数字集成电路(芯片)

2.什么是HDL

硬件描述语言(Hardware Description Language):用于描述数字电路结构和功能的语言,HDL可以在不同的层次对数字电路的结构、功能和行为进行描述。---逻辑设计(前端)。

HDL所描述的电路可以通过综合工具将其转换为门级电路网表,然后将其与某种工艺的基本元件逐一对应起来,再通过布局布线工具转换为电路布线结构。---电路实现(后端)

3.Verilog和C的区别

Verilog是硬件描述语言,在编译下载到FPGA之后,会生成电路,所以Verilog是并行运行的。

C语言是软件编程语言,编译下载到单片机之后,是存储器中的一组指令。而单片机处理软件指令需要取指、译码、执行,这个过程是串行执行的。

Verilog和C的区别也是FPGA和单片机/CPU的区别。FPGA由于全并行处理,处理速度非常快,这个是FPGA的优势,这一点是单片机/CPU替代不了的。

Verilog HDL作为一种高级的硬件描述语言,它的很多语法和C语言非常相似,因此在C语言的编程基础上去学习Verilog非常容易。

在学习过程中要培养硬件设计的思想,把新概念与硬件结构联系起来,着重理解Verilog的并行特性。

二、Verilog基础语法

1.逻辑值

0:表示低电平,对应电路GND;

1:表示高电平,对应电路VCC;

X:表示未知,有可能是高电平,也有可能是低电平;

Z:表示高阻态,外部没有激励信号,是一个悬空状态。

2.数字进制格式

Verilog数字进制格式包括二进制(b)、八进制(o)、十进制(d)和十六进制(h)。一般常用的为二进制、十进制、十六进制。

二进制表示如下:4'b0101表示4位二进制数字0101

十进制表示如下:4'd2表示4位十进制数字2(二进制0010)

十六进制表示如下:4'ha表示4位十六进制数字a(二进制1010)

3.标识符

标识符用于定义模块名、端口名、信号名等。推荐写法(sum、cpu_addr、clk_50、clk_cpu(要给到cpu的一个时钟信号)等);

(1)标识符可以是任意一组字母、数字、$符号和_(下划线)符号的组合;

(2)但标识符的第一个字符必须是字母或者下划线;

(3)标识符是区分大小写的;

4.数据类型

在Verilog语言中,主要有三大类数据类型;寄存器数据类型、线网数据类型和参数数据类型。在名称中,可以看到真正在数字电路中起作用的数据类型应该是寄存器数据类型和线网数据类型。

a.寄存器数据类型

寄存器表示一个被抽象的数据存储单元,通过赋值语句可以改变寄存器储存的值,寄存器数据类型的关键字是reg,reg类型数据的默认初始值为不定值x。

reg [31:0] delay_cnt;//延时计数,定义了一个位宽为32位名为delay_cnt的寄存器

reg key_reg;reg类型的数据只能在always语句和initial语句中被赋值。

如果该过程语句描述的是时序逻辑,即always语句带有时钟信号,则该寄存器变量应为触发器;

如果该过程语句描述的是组合逻辑,即always语句不带有时钟信号,则该寄存器变量对应为硬件连线。

b.线网类型

线网数据类型表示结构实体之间的物理连线。

线网类型的变量不能储存值,它的值是由驱动它的元件所决定的。

驱动线网类型变量的元件有门、连续赋值语句、assign等。如果没有驱动元件连接到线网类型的变量上,则该变量是高阻的,即其值为z。

线网数据类型包括wire型和tri型,其中最常用的就是wire类型。

c.参数类型

参数其实就是一个常量,在Verilog HDL中用parameter定义常量。

我们可以一次定义多个参数,参数与参数之间需要用逗号隔开。每个参数定义的右边必须是一个常数表达式。

//parameter define 4.3'RGB LCD

parameter H_SYNC = li'd41;//行同步

parameter H_BACK = li'd2;//行显示后沿

parameter H_DISP = li'd480;//行有效数据

parameter H_FRONT = li'd2;//行显示前沿

parameter H_TOTAL = li'd525;//行周期扫描参数型数据常用于定义状态机的状态、数据位宽和延迟大小等。

采用标识符来代表一个常量可以提高程序的可读性和维护性。

在模块调用时,可通过参数传递来改变被调用模块中已定义的参数。

位运算符:

~a:将a的每个位进行取反

&:将a的每个位与b相同的位进行相与

|:将a的每个位与b相同的位进行相或

^:将a的每个位与b相同的位进行异或

移位运算符:

<<:a<<b,将a左移b位

>>:a>>b,将a右移b位

两种移位运算都用0来填补移出的空位,左移时,位宽增加;右移时,位宽不变。

拼接运算符:

{}:{a,b},将a和b拼接起来,作为一个新信号。

三、程序框架

1.注释

行注释//,/*中间的内容都注释*/

2.关键字

-

module:定义一个模块。

-

endmodule:结束模块定义。

-

input:声明输入端口

-

output:声明输出端口

-

inout:inout声明双向端口

-

parameter:信号的参数定义

-

wire:wire信号定义

-

reg:reg信号定义

-

always:产生reg信号语句的关键字

-

assign:产生wire信号语句的关键字

-

begin:语句的起始标志

-

end:语句的结束标志

-

edge/posedge/negedge:时序电路的标志

-

case:case语句起始标记

-

default:case语句的默认分支标志

-

endcase:case语句的结束标志

-

if、else、for:循环语句标志

3.Verilog程序框架

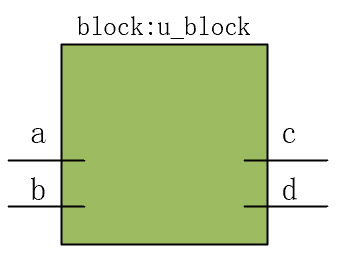

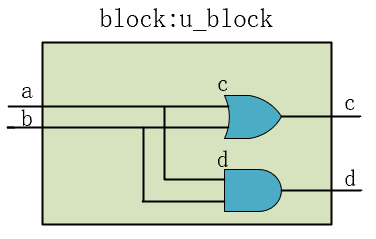

Verilog的基本设计单元是"模块"(block),一个模块是由两个部分组成的,一部分描述接口,另一部分描述功能。

module block(a,b,c,d);

input a,b;

output c,d;

assign c = a | b;

assign d = a & b;

endmodule

每个Verilog程序包括4个主要的部分:端口、IO说明、内部信号声明、功能定义。在always块中,逻辑是顺序执行的,而多个always之间是并行的。

4.模块的调用

在模块调用时,信号通过模块端口在模块之间传递。位宽需要保持一致。

5.语法篇-高级知识点

- intial和always

intial语句它在模块中只执行一次。常用于测试文件的编写,用来仿真测试信号,或者用于对存储器变量赋初值。

always语句一直在不断地重复活动。但是只有和一定的时间控制结合在一起才有作用。always的时间控制可以是沿触发,也可以是电平触发;可以是单个信号,也可以是多个信号,多个信号中间要用关键字or连接。always语句后紧跟的过程块是否运行,要看它的触发条件是否满足。

沿触发的always块常常描述时序逻辑行为,电平触发常常描述组合逻辑行为。组合逻辑电路任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。时序逻辑电路中,任一时刻的输出不仅取决于当前信号,还取决于电路原来的状态,或者说还与以前的输入有关,因此时序逻辑必须具备记忆功能。由关键词or连接的多个事件名或信号名组成的列表称为"敏感列表"。

Verilog HDL语言中,信号有两种赋值方式:1.阻塞语句(b=a);2.非阻塞语句(b<=a)。

所谓阻塞的概念是指,在同一个always块中,后面的赋值语句是在前一句赋值语句结束后才开始赋值的。阻塞赋值可以认为只有一个步骤的操作:即计算RHS并更新LHS。

always @(posedge clk or negedge (rst_n) begin

if(!rst_n)begin

a=1;

b=2;

c=3;

end

else begin

a=0;

b=a;

c=b;

end

end所谓的非阻塞概念是指,在计算非阻塞赋值的RHS以及更新LHS期间,允许其它的非阻塞赋值语句同时计算RHS和更新LHS,非阻塞赋值的操作可以看作两个步骤:

(1)赋值开始的时候,计算RHS;

(2)赋值结束的时候,更新LHS。

always @(posedge clk or negedge (rst_n) begin

if(!rst_n)begin

a<=1;

b<=2;

c<=3;

end

else begin

a<=0;

b<=a;

c<=b;

end

end非阻塞赋值只能用于对寄存器类型的变量进行赋值,因此只能用在initial和always。

小结:

在描述组合逻辑的always块中用阻塞赋值=,综合成组合逻辑的电路结构;

在描述时序逻辑的always块中用非阻塞赋值<=,综合成时序逻辑的电路结构;

这种电路结构往往与触发沿有关系,只有在触发沿时才可能发生阻塞的变化。

注意:在同一个always块中不要既用非阻塞赋值又用阻塞赋值。

- 条件语句

if-else语句、case语句,(4'h0,四位数值来处理,)条件语句必须在过程块中使用。过程块语句是指由initial和always语句引导的块语句。

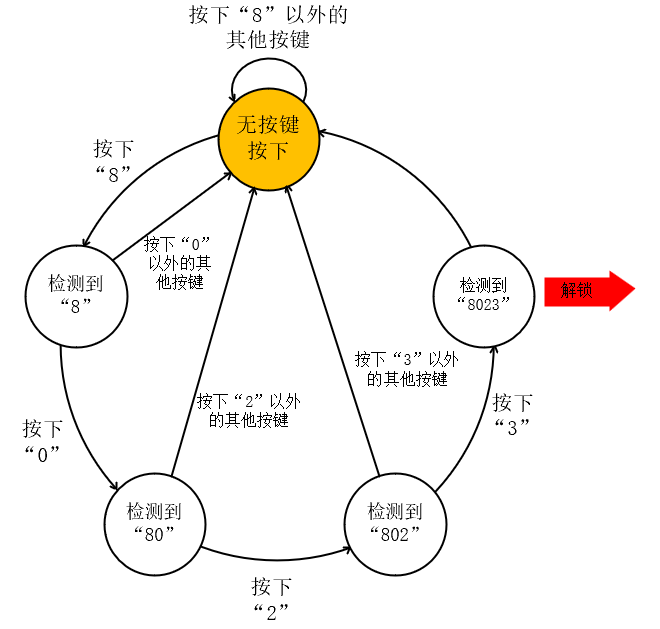

四、状态机

状态机是在有限个状态之间按一定规律转换的时序电路,状态机适合在fpga里面的顺序执行,因为Verilog是并行的。状态寄存器由一组触发器组成,用来记忆状态机当前所处的状态,状态的改变只发生在时钟的跳变沿。状态是否改变、如何改变,取决于组合逻辑F的输出,F是当前状态和输入信号的函数。状态机的输出是由输出组合逻辑G提供的,G也是当前状态和输入信号的函数,用电子门锁举例:密码为8023。

Mealy状态机:状态机的输出不仅与当前状态有关,还与输入信号有关。

Moore状态机:状态机输出只与当前状态有关,而与输入信号无关。

状态机设计:

1.状态空间定义

2.状态跳转

3.下个状态判断

4.各个状态下的动作