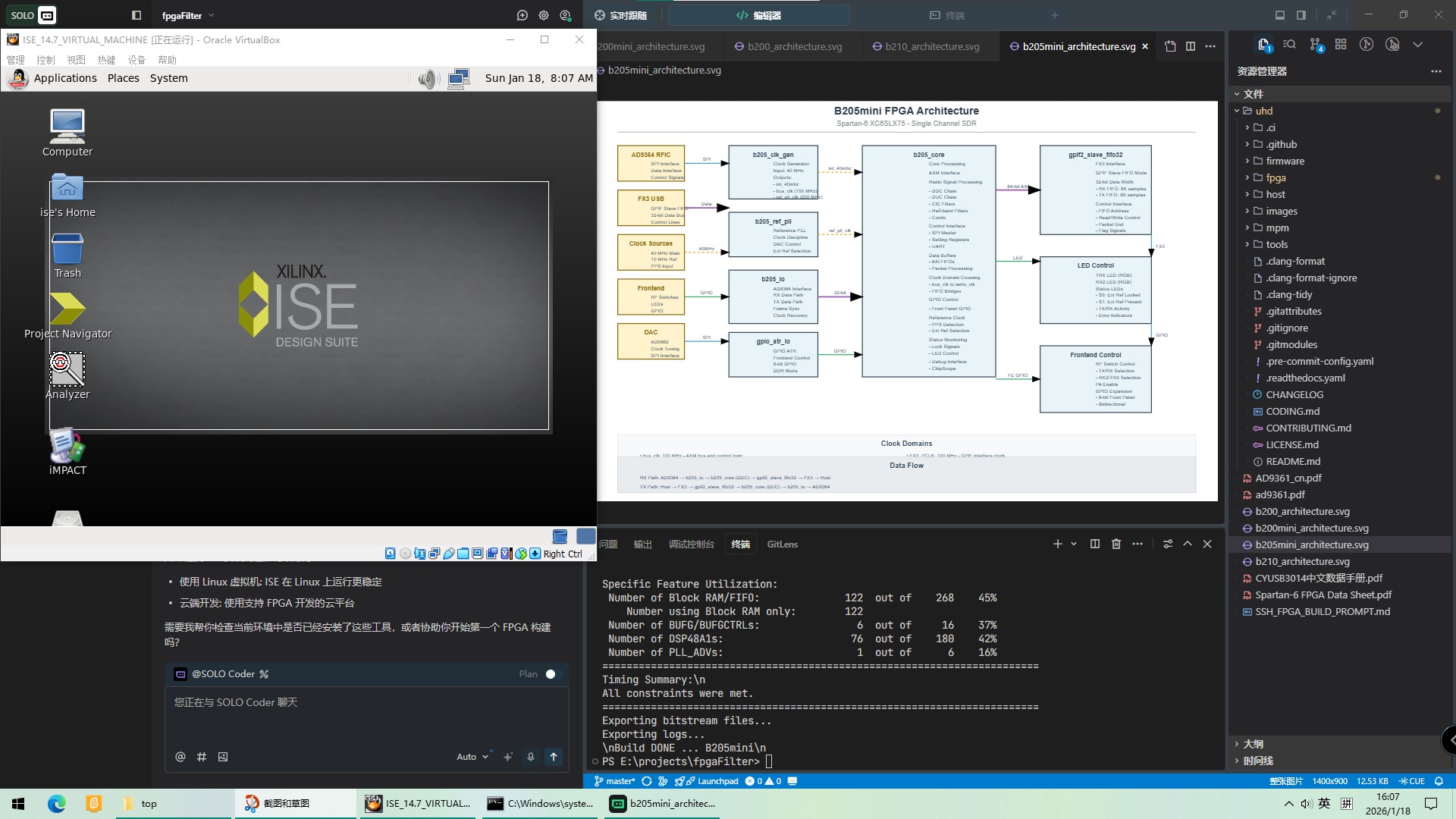

近期,采用ISE 环境结合AI Trae,成功自动化编译了USRP B210/B205系列的FPGA工程,并在AI的协助下,初步了解了工程的结构,自动化产生了Bits, 下面把内容总结如下。

目录

- [1. 硬件架构概览](#1. 硬件架构概览)

- [2. 系统时钟架构](#2. 系统时钟架构)

- [3. 核心模块详解](#3. 核心模块详解)

- [4. 数据流分析](#4. 数据流分析)

- [5. DSP处理链](#5. DSP处理链)

- [6. 控制接口](#6. 控制接口)

- [7. 二次开发指南](#7. 二次开发指南)

- [8. 常见应用场景](#8. 常见应用场景)

- [9. 构建与调试](#9. 构建与调试)

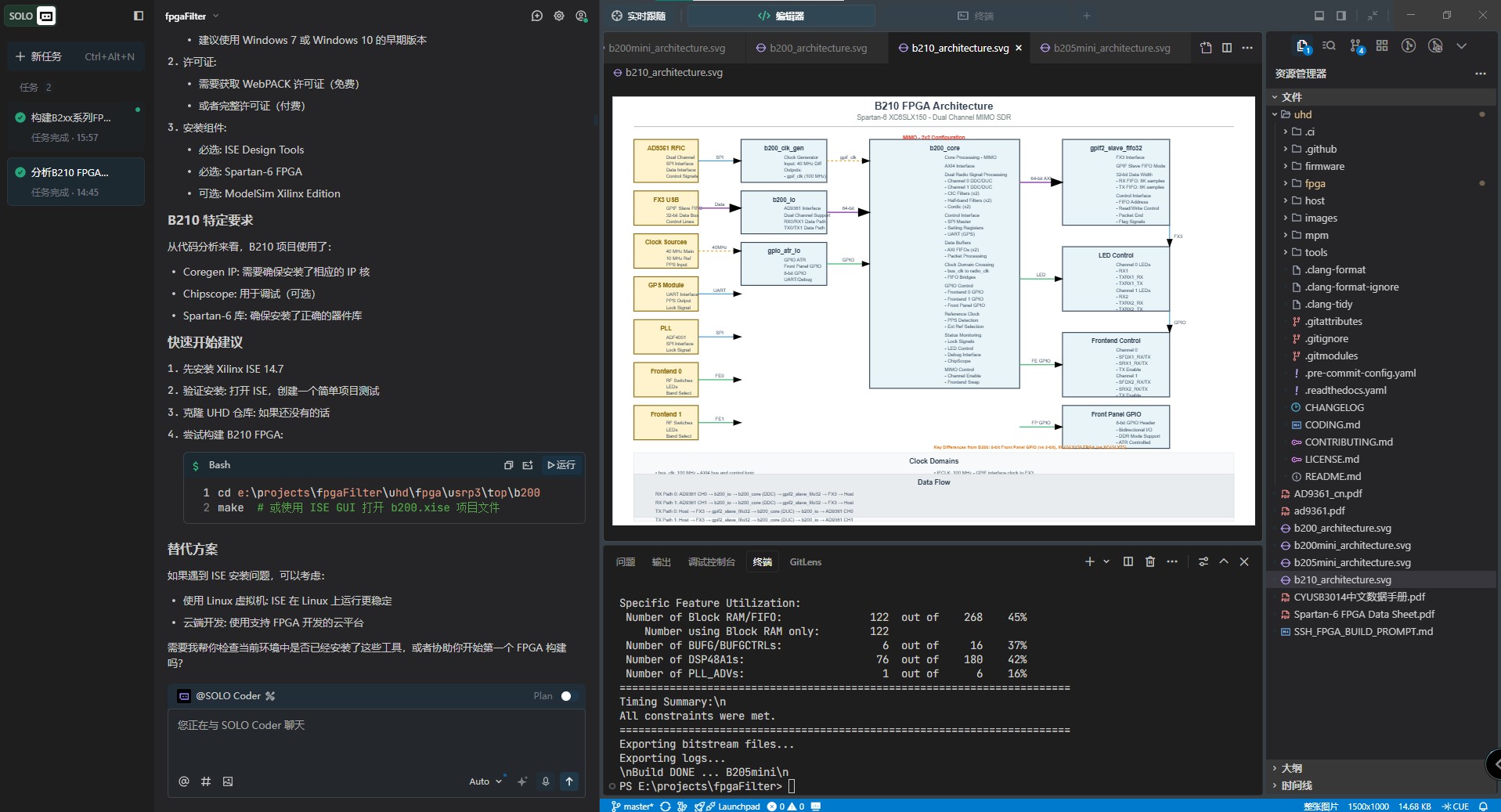

1. 硬件架构概览

1.1 硬件规格

| 组件 | 型号/规格 | 说明 |

|---|---|---|

| FPGA | Spartan-6 XC6SLX75-FGG484-3 | B200mini使用75K逻辑单元 |

| FPGA | Spartan-6 XC6SLX150-FGG484-3 | B205mini使用150K逻辑单元 |

| RFIC | AD9364 | 单通道收发器,70MHz-6GHz |

| USB接口 | Cypress FX3 (CYUSB3014) | USB 3.0 SuperSpeed |

| 主时钟 | 40MHz | 板载晶振 |

| 参考时钟 | 10MHz | 外部参考输入 |

| PPS | 1PPS | 脉冲每秒输入 |

1.2 系统架构图

总线接口

核心处理

IO接口

时钟子系统

外部接口

40MHz

int_40mhz

bus_clk 100MHz

ref_pll_clk 200MHz

12位DDR数据

radio_clk

32位数据

AD9364 RFIC

FX3 USB 3.0

时钟源

40MHz/10MHz/PPS

前端控制

RF开关/LED/GPIO

b205_clk_gen

时钟生成器

b205_ref_pll

参考PLL

b205_io

AD9364接口

gpio_atr_io

GPIO ATR控制

b205_core

核心处理

radio_legacy

无线电处理

DDC Chain

数字下变频

DUC Chain

数字上变频

gpif2_slave_fifo32

FX3接口

AXI4总线

100MHz

1.3 模块层次结构

b205.v (顶层模块)

├── b205_clk_gen (时钟生成器)

├── b205_ref_pll (参考时钟PLL)

├── b205_io (AD9364接口)

├── b205_core (核心处理)

│ ├── radio_legacy (无线电处理)

│ │ ├── ddc_chain (数字下变频链)

│ │ │ ├── NCO (数控振荡器)

│ │ │ ├── CORDIC (坐标旋转数字计算机)

│ │ │ ├── CIC Decimator (级联积分梳状滤波器)

│ │ │ └── Half-band Decimators (半带滤波器)

│ │ ├── duc_chain (数字上变频链)

│ │ │ ├── Half-band Interpolators (半带插值器)

│ │ │ ├── CIC Interpolator (级联积分梳状插值器)

│ │ │ ├── CORDIC (坐标旋转)

│ │ │ └── NCO (数控振荡器)

│ │ ├── radio_ctrl_proc (无线电控制处理器)

│ │ ├── timekeeper (时间管理器)

│ │ └── gpio_atr (GPIO ATR控制)

│ ├── radio_ctrl_proc (总线控制处理器)

│ ├── simple_spi_core (SPI控制器)

│ └── axi_mux4/demux4 (AXI路由)

├── gpio_atr_io (GPIO ATR IO)

└── gpif2_slave_fifo32 (FX3接口)

├── RX FIFO (8K样本)

└── TX FIFO (8K样本)2. 系统时钟架构

2.1 时钟域概览

时钟使用

时钟域

时钟生成

40MHz晶振

b205_clk_gen

bus_clk

100MHz

AXI4总线

radio_clk

61.44MHz

AD9364数据时钟

int_40mhz

40MHz

内部时钟

ref_pll_clk

200MHz

PLL输入

AXI4接口

控制逻辑

DSP处理

DDC/DUC

AD9364接口

参考PLL

2.2 时钟域详细说明

| 时钟域 | 频率 | 用途 | 说明 |

|---|---|---|---|

| bus_clk | 100 MHz | AXI4总线、控制逻辑 | 由b205_clk_gen从40MHz生成 |

| radio_clk | 变量 (通常61.44 MHz) | AD9364数据时钟、DSP处理 | 从AD9364的CAT_DCLK_P恢复 |

| int_40mhz | 40 MHz | 内部时钟、参考PLL输入 | 直接来自40MHz晶振 |

| ref_pll_clk | 200 MHz | 参考PLL输入时钟 | 由b205_clk_gen生成 |

| FX3_PCLK | 100 MHz | GPIF接口时钟 | 与bus_clk同步 |

2.3 时钟域交叉

时钟域交叉通过AXI FIFO实现:

verilog

// 示例:控制数据从bus_clk到radio_clk的CDC

axi_fifo_2clk #(.WIDTH(65), .SIZE(0)) ctrl_fifo

(.reset(bus_rst),

.i_aclk(bus_clk), .i_tvalid(ctrl_tvalid), .i_tready(ctrl_tready),

.i_tdata({ctrl_tlast, ctrl_tdata}),

.o_aclk(radio_clk), .o_tvalid(ctrl_tvalid_r),

.o_tready(ctrl_tready_r), .o_tdata({ctrl_tlast_r, ctrl_tdata_r}));3. 核心模块详解

3.1 b205.v - 顶层模块

文件位置 : b205.v

主要功能:

- 实例化所有子模块

- 连接外部接口

- 生成系统时钟

- 处理复位逻辑

关键信号:

verilog

module b205 (

// AD9364 - SPI接口

output CAT_SPI_EN, input CAT_SPI_DO,

output CAT_SPI_DI, output CAT_SPI_CLK,

// AD9364 - 控制

output CAT_EN, output CAT_EN_AGC,

output CAT_RESETn, output CAT_TXnRX,

output [3:0] CAT_CTL_IN, input [7:0] CAT_CTL_OUT,

// AD9364 - 数据接口

input CAT_DCLK_P, output CAT_FBCLK_P,

input [11:0] CAT_P0_D, output [11:0] CAT_P1_D,

input CAT_RX_FR_P, output CAT_TX_FR_P,

// 时钟

input CLK_40MHz_FPGA,

// FX3 GPIF接口

output FX3_PCLK, output FX3_CTL0, output FX3_CTL1,

output FX3_CTL2, output FX3_CTL3, output FX3_CTL7,

input FX3_CTL4, input FX3_CTL5, input FX3_CTL6,

input FX3_CTL8, output FX3_CTL11, output FX3_CTL12,

inout [31:0] FX3_DQ, input FX3_CTL9,

// LED和GPIO

output cLED_TRX_G, output cLED_TRX_B, output cLED_TRX_R,

output cLED_RX2_G, output cLED_RX2_B, output cLED_RX2_R,

output cLED_S0, output cLED_S1,

inout [7:0] fp_gpio,

// PPS和参考时钟

input PPS_IN, input CLKIN_10MHz,

output CLKIN_10MHz_REQ,

// DAC控制

output CLK_40M_DAC_nSYNC, output CLK_40M_DAC_SCLK,

output CLK_40M_DAC_DIN,

// RF硬件控制

output cFE_SEL_TRX_TX, output cFE_SEL_TRX_RX,

output cFE_SEL_RX_TRX, output cFE_SEL_RX_RX2,

output cTXDRV_PWEN

);3.2 b205_io.v - AD9364接口模块

文件位置 : b205_io.v

主要功能:

- 处理AD9364的DDR数据接口

- 时钟恢复和缓冲

- I/Q数据解复用

关键特性:

verilog

module b205_io (

input reset,

// 基带采样接口

output radio_clk,

output [11:0] rx_i0, output [11:0] rx_q0,

input [11:0] tx_i0, input [11:0] tx_q0,

// Catalina接口

input rx_clk, input rx_frame, input [11:0] rx_data,

output tx_clk, output tx_frame, output [11:0] tx_data

);时钟缓冲架构:

CAT_DCLK_P

AD9364 RX时钟

IBUFG

全局时钟缓冲

BUFIO2 LT

左上角Bank

BUFIO2 LB

左下角Bank

siso_clk

1x时钟

radio_clk

全局时钟

IDDR2

DDR接收器

RX I/Q数据

DDR数据接收:

verilog

// 使用IDDR2接收DDR数据

IDDR2 #(.DDR_ALIGNMENT("C0")) iddr2_i0 (

.Q0(rx_q[0]), .Q1(rx_i[0]),

.C0(io_clk_lb), .C1(io_clk_lb_b),

.CE(1'b1), .D(rx_data[0]),

.R(1'b0), .S(1'b0)

);3.3 b205_core.v - 核心处理模块

文件位置 : b205_core.v

主要功能:

- AXI4总线路由

- 控制命令处理

- 响应数据多路复用

- PPS时间同步

- 用户设置寄存器

关键参数:

verilog

module b205_core #(

parameter R0_CTRL_SID = 8'h10, // 无线电控制流ID

parameter U0_CTRL_SID = 8'h30, // 用户控制流ID

parameter L0_CTRL_SID = 8'h40, // 本地控制流ID

parameter R0_DATA_SID = 8'h50, // 无线电数据流ID

parameter EXTRA_BUFF_SIZE = 12, // 额外缓冲大小

parameter RADIO_FIFO_SIZE = 11, // 无线电FIFO大小

parameter SAMPLE_FIFO_SIZE = 11 // 采样FIFO大小

)控制流路由:

控制输入

ctrl_tdata

axi_demux4

控制解复用器

R0控制

无线电控制

L0控制

本地控制

U0控制

用户控制

3.4 radio_legacy.v - 无线电处理模块

文件位置 : radio_legacy.v

主要功能:

- 无线电信号处理

- DDC/DUC链路控制

- GPIO ATR控制

- 时间戳管理

- 用户设置寄存器

关键参数:

verilog

module radio_legacy #(

parameter RADIO_FIFO_SIZE = 13, // 无线电FIFO大小

parameter SAMPLE_FIFO_SIZE = 11, // 采样FIFO大小

parameter FP_GPIO = 0, // 前面板GPIO

parameter NEW_HB_INTERP = 1, // 新型半带插值器

parameter NEW_HB_DECIM = 1, // 新型半带抽取器

parameter SOURCE_FLOW_CONTROL = 0, // 源流控

parameter USER_SETTINGS = 0, // 用户设置寄存器

parameter DEVICE = "SPARTAN6" // 器件类型

)设置寄存器映射:

| 地址 | 功能 | 说明 |

|---|---|---|

| 0x06 | LOOPBACK | 回环模式 |

| 0x08 | SPI | SPI接口控制 |

| 0x12-0x18 | ATR | GPIO ATR控制 |

| 0x21 | TEST | 测试寄存器 |

| 0x22 | CODEC_IDLE | 编解码器空闲值 |

| 0x32 | READBACK | 读回地址选择 |

| 0x64 | TX_CTRL | TX控制 |

| 0x96 | RX_CTRL | RX控制 |

| 0x128-0x130 | TIME | 时间戳 |

| 0x136 | RX_FMT | RX格式 |

| 0x138 | TX_FMT | TX格式 |

| 0x144-0x183 | RX_DSP | RX DSP参数 |

| 0x184-0x1C3 | TX_DSP | TX DSP参数 |

| 0x200-0x206 | FP_GPIO | 前面板GPIO |

| 0x253-0x254 | USER_SR | 用户设置寄存器 |

| 0x255 | USER_RB_ADDR | 用户读回地址 |

3.5 gpif2_slave_fifo32.v - FX3接口模块

文件位置 : gpif2_slave_fifo32.v

主要功能:

- 实现GPIF Slave FIFO模式

- 32位数据总线

- RX/TX FIFO缓冲

- 数据包处理

FIFO配置:

verilog

gpif2_slave_fifo32 #(

.DATA_RX_FIFO_SIZE(13), // RX FIFO: 8K样本

.DATA_TX_FIFO_SIZE(13) // TX FIFO: 8K样本

) slave_fifo32 (

.gpif_clk(bus_clk), .gpif_rst(bus_rst), .gpif_enb(1'b1),

.gpif_ctl({FX3_CTL8, FX3_CTL6, FX3_CTL5, FX3_CTL4}),

.fifoadr({FX3_CTL11, FX3_CTL12}),

.slwr(FX3_CTL1), .sloe(FX3_CTL2), .slcs(FX3_CTL0),

.slrd(FX3_CTL3), .pktend(FX3_CTL7),

.gpif_d(FX3_DQ),

.fifo_clk(bus_clk), .fifo_rst(bus_rst),

.tx_tdata(tx_tdata), .tx_tlast(tx_tlast),

.tx_tvalid(tx_tvalid), .tx_tready(tx_tready),

.rx_tdata(rx_tdata), .rx_tlast(rx_tlast),

.rx_tvalid(rx_tvalid), .rx_tready(rx_tready),

.ctrl_tdata(ctrl_tdata), .ctrl_tlast(ctrl_tlast),

.ctrl_tvalid(ctrl_tvalid), .ctrl_tready(ctrl_tready),

.resp_tdata(resp_tdata), .resp_tlast(resp_tlast),

.resp_tvalid(resp_tvalid), .resp_tready(resp_tready)

);4. 数据流分析

4.1 RX数据流

主机接口

总线接口

DSP处理

FPGA接口

AD9364

RF输入

ADC

DDR输出

b205_io

DDR接收

解复用

DDC Chain

数字下变频

NCO

混频

CORDIC

旋转

CIC抽取器

半带滤波器

AXI FIFO

时钟域交叉

数据包门控

gpif2_slave_fifo32

FX3接口

FX3 USB

主机PC

RX数据流详细步骤:

- AD9364采样: RF信号经过ADC转换为12位I/Q数据

- DDR传输: 通过12位DDR接口传输到FPGA

- 解复用: b205_io将DDR数据解复用为I和Q分量

- DDC处理 :

- NCO混频: 将信号下变频到基带

- CORDIC旋转: 执行复数旋转

- CIC抽取: 降低采样率

- 半带滤波: 抗混叠滤波

- 时钟域交叉: 通过AXI FIFO从radio_clk域到bus_clk域

- 数据包化: 将样本打包成数据包

- USB传输: 通过FX3传输到主机

4.2 TX数据流

AD9364

FPGA接口

DSP处理

总线接口

主机接口

主机PC

FX3 USB

gpif2_slave_fifo32

FX3接口

AXI FIFO

时钟域交叉

DUC Chain

数字上变频

半带插值器

CIC插值器

CORDIC

旋转

NCO

混频

复用

b205_io

DDR发送

DDR输入

DAC

RF输出

TX数据流详细步骤:

- USB接收: 主机通过USB发送I/Q样本

- FIFO缓冲: gpif2_slave_fifo32缓冲数据

- 时钟域交叉: 通过AXI FIFO从bus_clk域到radio_clk域

- DUC处理 :

- 半带插值: 提高采样率

- CIC插值: 进一步提高采样率

- CORDIC旋转: 执行复数旋转

- NCO混频: 将信号上变频到RF

- 复用: 将I和Q分量复用到DDR接口

- DDR传输: 通过12位DDR接口传输到AD9364

- DAC转换: AD9364将数字信号转换为RF

5. DSP处理链

5.1 DDC Chain (数字下变频链)

文件位置 : ddc_chain.v

处理流程:

RX输入

12位I/Q

输入复用

I/Q交换/取反

NCO

数控振荡器

CORDIC

坐标旋转

CIC抽取器

可配置抽取率

半带滤波器1

2倍抽取

半带滤波器2

2倍抽取

缩放

RX输出

16位I/Q

关键寄存器:

| 地址 | 位宽 | 功能 |

|---|---|---|

| BASE+0 | 32 | NCO相位增量 (频率控制) |

| BASE+1 | 18 | 缩放因子 |

| BASE+2 | 10 | CIC抽取率 + HB使能 |

| BASE+3 | 4 | I/Q交换、取反、实模式 |

| BASE+4 | 22 | 半带滤波器系数重载 |

NCO频率计算:

phase_inc = (f_desired / f_sample) * 2^32其中:

f_desired: 期望的频率偏移f_sample: 采样率

CIC抽取率:

- 范围: 1-128

- 总抽取率 = CIC率 × 2^HB使能数

- 最大抽取率: 128 × 2 × 2 = 512

代码示例:

verilog

// NCO相位累加器

always @(posedge clk)

if(rst)

phase <= 0;

else if(~run)

phase <= 0;

else

phase <= phase + phase_inc;

// CORDIC旋转

cordic_z24 #(.bitwidth(cwidth))

cordic(.clock(clk), .reset(rst), .enable(run),

.xi(to_cordic_i), .yi(to_cordic_q), .zi(phase[31:32-zwidth]),

.xo(i_cordic), .yo(q_cordic), .zo());5.2 DUC Chain (数字上变频链)

文件位置 : duc_chain.v

处理流程:

TX输入

16位I/Q

半带插值器1

2倍插值

半带插值器2

2倍插值

CIC插值器

可配置插值率

CORDIC

坐标旋转

NCO

数控振荡器

TX输出

12位I/Q

关键寄存器:

| 地址 | 位宽 | 功能 |

|---|---|---|

| BASE+0 | 32 | NCO相位增量 (频率控制) |

| BASE+1 | 18 | 缩放因子 |

| BASE+2 | 10 | CIC插值率 + HB使能 |

插值率配置:

- CIC插值率: 1-128

- 半带插值: 每个使能的HB提供2倍插值

- 总插值率 = CIC率 × 2^HB使能数

- 最大插值率: 128 × 2 × 2 = 512

5.3 CORDIC算法

CORDIC (Coordinate Rotation Digital Computer) 用于执行复数旋转:

x_out = x_in * cos(θ) - y_in * sin(θ)

y_out = x_in * sin(θ) + y_in * cos(θ)特性:

- 24位精度

- 算法增益: 1.647

- 实现增益: 0.5

- 总增益: 0.8235

- 最大旋转增益: 1.4142 (sqrt(2))

- 最坏情况总增益: 1.1646

6. 控制接口

6.1 SPI接口

SPI控制器: simple_spi_core

功能:

- 配置AD9364寄存器

- 支持多从设备

- 可配置时钟极性和相位

SPI信号:

verilog

output [7:0] sen, // 从设备使能

output sclk, // SPI时钟

output mosi, // 主出从入

input miso // 主入从出6.2 GPIO ATR控制

GPIO ATR: gpio_atr

功能:

- 根据TX/RX状态自动切换GPIO

- 支持三种状态: IDLE、TX、RX

- 可配置每个状态的GPIO输出

状态机:

初始状态

开始发送

开始接收

发送完成

接收完成

立即切换

立即切换

IDLE

TX

RX

寄存器映射:

| 地址 | 功能 |

|---|---|

| SR_ATR+0 | IDLE状态GPIO值 |

| SR_ATR+1 | RX状态GPIO值 |

| SR_ATR+2 | TX状态GPIO值 |

| SR_ATR+3 | DDR控制 (1=输出) |

6.3 AXI4流接口

AXI4流协议:

verilog

// 数据通道

input [63:0] tdata, // 数据

input tlast, // 最后一个数据

input tvalid, // 数据有效

output tready // 准备接收流类型:

| 流类型 | SID | 方向 | 说明 |

|---|---|---|---|

| R0_CTRL | 0x10 | 双向 | 无线电控制 |

| R0_DATA | 0x50 | 双向 | 无线电数据 |

| U0_CTRL | 0x30 | 双向 | 用户控制 |

| L0_CTRL | 0x40 | 双向 | 本地控制 |

7 TRAE Solo模式Spartan配置环境指南

7.1 ISE_14.7虚拟机初始配置

步骤1:创建虚拟机

- 在Xilinx ISE 14.7安装目录下,找到并运行

xsetup.exe。 - 安装时,把下载好的uhd驱动的宿主文件夹路径填写到对应的共享文件夹位置。本例子中为

E:\projects\fpgaFilter\uhd,映射到虚拟机里是~/projects/fpgaFilter/uhd。 - 安装完毕后,会创建一个新的虚拟机,默认名称为

ISE_14.7_VIRTUAL_MACHINE。

步骤2:虚拟机配置

TRAE Solo模式在Windows 10上运行Oracle Linux 6虚拟机,用于Xilinx ISE 14.7的Spartan-6 FPGA开发环境。

| 配置项 | 值 |

|---|---|

| 操作系统 | Oracle Linux 6 |

| 虚拟机平台 | Windows 10 + 虚拟化 |

| FPGA工具 | Xilinx ISE 14.7 |

| Python版本 | Python 3.6 (rh-python36) |

| SSH用户 | ise |

| SSH地址 | 192.168.56.102 |

| 项目路径 | ~/projects/fpgaFilter |

步骤3:系统基础配置

虚拟机使用双网卡,网卡1是Hostonly 模式,用于与Windows主机通信。

网卡2是NAT或桥接模式,确保Windows主机可以通过SSH访问192.168.56.102。

Oracle Linux 6默认使用Python 2.6,需要通过Software Collections安装Python 3.6。

bash

# 安装Oracle Software Collections仓库

sudo yum install oracle-softwarecollection-release-el6.x86_64

# 安装Python 3.6

sudo yum -y install scl-utils rh-python36

# 验证安装

scl --list

# 输出应包含:rh-python36启用Python 3.6

bash

# 临时启用Python 3.6

scl enable rh-python36 bash

# 验证Python版本

python --version

# 输出应显示:Python 3.6.x

# 验证pip

pip --version

7.2 从Trar主机连接到虚拟机

生成SSH密钥对

在Windows主机上生成SSH密钥对:

bash

# 在Windows PowerShell或Git Bash中执行

ssh-keygen -t rsa -b 4096

# 按提示操作:

# - 保存路径:默认即可(通常在C:\Users\用户名\.ssh\id_rsa)

# - 密码短语:留空(实现无密码登录)配置虚拟机SSH

bash

# 在Windows主机上查看公钥

cat ~/.ssh/id_rsa.pub

# 在虚拟机中创建.ssh目录

mkdir -p ~/.ssh

chmod 700 ~/.ssh

# 将公钥内容复制到authorized_keys文件

vim ~/.ssh/authorized_keys

# 设置正确的权限

chmod 600 ~/.ssh/authorized_keys7.3 TRAE Solo模式集成

TRAE Solo模式 SSH FPGA 构建任务提示词:

基本信息:

- 服务器地址: 192.168.56.102

- 用户名: ise

- 密码: ise

- 项目路径 : 本地项目路径中的projects层级被网盘映射到192.168.56.102的/projects文件夹,因此,本地的子路径都可以用这个规律推定。例如,本地项目路径为/projects/fpgaFilter,在服务器上的路径就是~/projects/fpgaFilter。

- ISE 版本: 14.7 (Spartan-6)

- Python 版本: 3.6 (通过 scl enable rh-python36 启用)

完整构建命令

bash

ssh ise@192.168.56.102 "scl enable rh-python36 'cd ~/projects/path/to/top && source /opt/Xilinx/14.7/ISE_DS/settings64.sh && make B205mini'"

8. 构建与调试

8.1 构建流程

源代码

.v文件

创建ISE项目

Makefile.b205.inc

综合

XST

映射

MAP

布局布线

PAR

位流生成

BitGen

生成报告

check_timing.py

8.2 输出文件

| 文件 | 位置 | 说明 |

|---|---|---|

| b205.bit | build/ | FPGA位流 (带头部) |

| b205.bin | build/ | FPGA位流 (无头部) |

| b205.syr | build/ | 综合报告 |

| b205.twr | build/ | 时序报告 |

| b205.rpt | build/ | 利用率和时序摘要 |

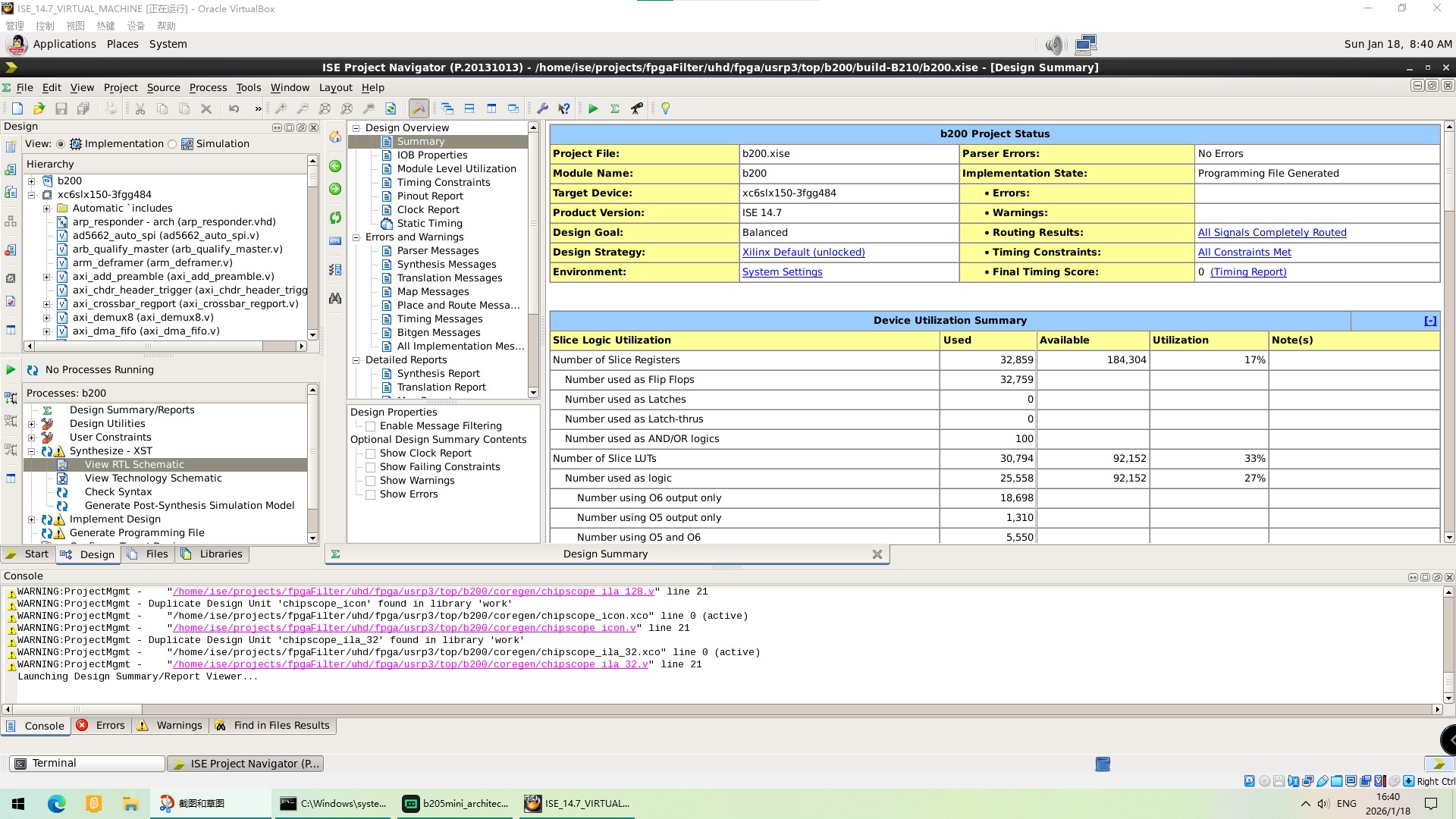

8.3 资源利用率

典型资源使用 (B205mini, XC6SLX150):

| 资源 | 使用 | 总数 | 利用率 |

|---|---|---|---|

| Slice Registers | ~33,000 | 184,304 | ~18% |

| Slice LUTs | ~73,000 | 184,304 | ~40% |

| Block RAM | ~188 | 268 | ~70% |

| DSP48A1 | ~151 | 180 | ~84% |

8.4 时序约束

关键时序路径:

verilog

// 时钟约束示例 (timing.ucf)

NET "bus_clk" TNM_NET = "bus_clk";

TIMESPEC "TS_bus_clk" = PERIOD "bus_clk" 10 ns HIGH 50%;

NET "radio_clk" TNM_NET = "radio_clk";

TIMESPEC "TS_radio_clk" = PERIOD "radio_clk" 16.276 ns HIGH 50%;

NET "FX3_PCLK" TNM_NET = "FX3_PCLK";

TIMESPEC "TS_FX3_PCLK" = PERIOD "FX3_PCLK" 10 ns HIGH 50%;

// 跨时钟域约束

TIMESPEC "TS_bus_to_radio" = FROM "bus_clk" TO "radio_clk" TIG;9. 总结

B205mini FPGA工程是一个完整的SDR平台,提供了灵活的硬件架构和丰富的DSP功能。通过理解其架构和模块,开发者可以轻松添加自定义功能。

9.1 关键要点

- 时钟域: 理解bus_clk和radio_clk的交叉

- 数据流: 掌握RX/TX数据流的完整路径

- DSP链: 熟悉DDC/DUC的处理流程

- 控制接口: 了解SPI、GPIO ATR和AXI4流

- 用户扩展: 利用USER_SETTINGS添加自定义功能

9.2 进一步学习

- UHD官方文档

-

Spartan-6数据手册\](./Spartan-6 FPGA Data Sheet.pdf)

- Xilinx ISE用户指南

9.3 社区资源

文档版本 : 1.0

最后更新 : 2026-01-18

作者 : Trae AI

许可证: LGPL-3.0-or-later