三极管和MOS管的降额使用设计实战

在我们设计的电子产品设计中,器件的长期可靠性是衡量产品质量的核心标准,需要我们设计中预留足够的margin, 意味着设计时需要留出足够的冗余,即需要降额设计。三极管与MOS管作为最基础的半导体器件,其稳定性直接决定了整个系统的寿命和性能。实际工程应用表明,适当的降额设计可以将器件失效率降低 6-16 倍,是提升产品可靠性最有效的手段之一。本文结合我过往的设计和调试案例,深入三极管与MOS管的降额设计理念,从核心原理到实战案例,解决工程师在实践中可能会遇到的常见问题,旨在帮助大家建立一套完整而可靠的器件选型与应用方法论,并能应用在实际项目的设计和分析中。

对于每一位硬件工程师而言,最激动人心的时刻莫过于设计的电路板在客户手上完美运行。然而,从我们设计的样卡到可靠的量产产品之间,存在一道看不见却至关重要的鸿沟,那就是"可靠性设计"。很多在测试台上表现良好的原型机,一旦进入实际应用环境,特别是在经历温度波动,长时间运行和电压波动的考验后,便会开始出现各种意想不到的故障。其中,开关管和功率器件的失效是最常见也最致命的问题之一。

比如大家最常见的疑惑就是为什么数据手册上标称可以承受60A电流的MOS管,在实际20A的应用中就烧毁了?为什么一个简单的三极管线性稳压电路,在夏天会频繁出现故障?

一、电路原理讲解

什么是降额设计?

降额设计,顾名思义就是让元器件工作在其数据手册Datasheet标定的最大额定值之下,并预留一定的margin。其目的不是为了"浪费"器件性能,而是为了应对真实世界中各种不确定因素,从而大幅提升产品的平均无故障时间(MTBF)和整体寿命。这些不确定因素包括:环境温度变化,输入电压波动,负载瞬态变化,器件自身参数的离散性以及长期老化等。

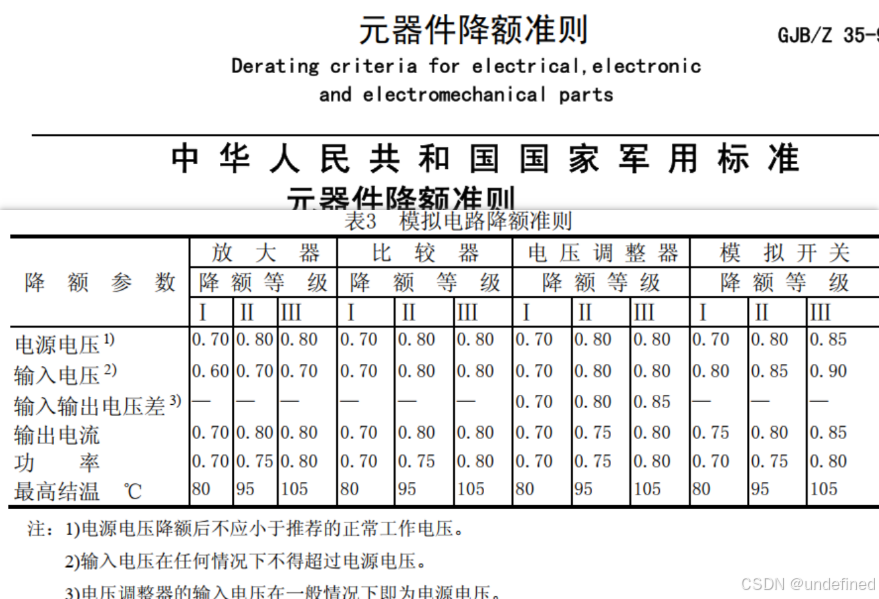

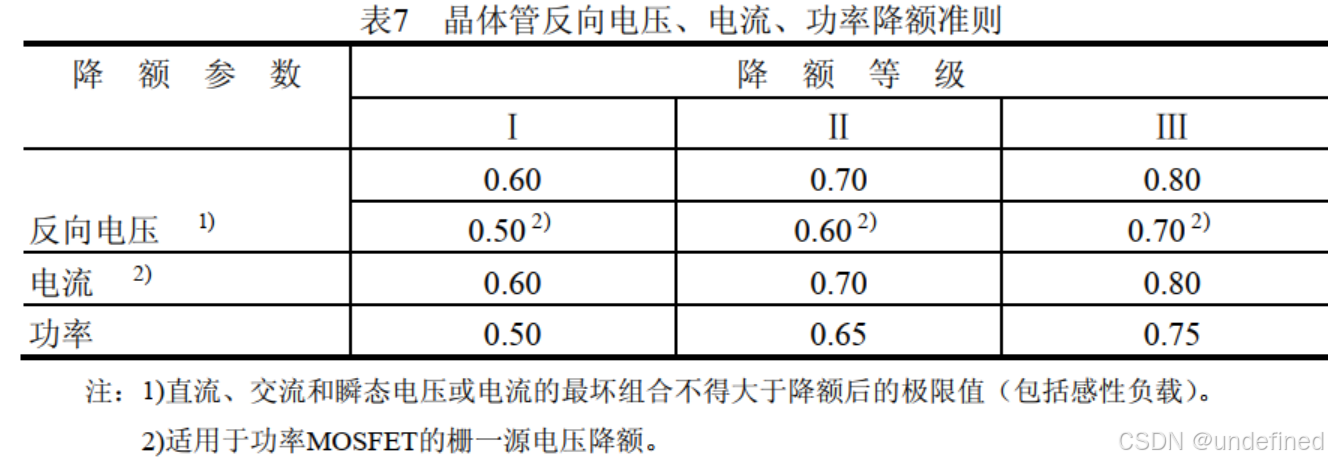

降额设计的核心是应力比控制,即实际工作应力与额定应力的比值。根据 GJB/Z 35-1993中元器件降额准则,降额分为三个等级:

I 级降额(最严格):功率降额系数 0.5-0.6,适用于高可靠性要求场合

II 级降额(中等):功率降额系数 0.6-0.75,适用于一般工业应用

III 级降额(最宽松):功率降额系数 0.75-0.8,适用于成熟标准设计

备注:专栏中提到的所有规范文档,都会免费分享给大家。

为何必须进行降额?因为这是可靠性运行的基石。 由于半导体器件的失效概率与其工作应力,特别是结温(Junction Temperature, Tj) ,呈现指数级的关系。根据经典的Arrhenius模型,温度每升高10摄氏度,半导体器件的寿命大约会缩短一半。大家牢记这个模型,其应用非常广泛,电解电容的寿命也有类似的规律,在实际的设计考量中非常实用。降额设计的本质核心目标,就是通过控制电应力(电压和电流)和热应力(功率损耗),将器件的结温控制在一个绝对安全的范围内。

功率降额公式:P 允许 = P 额定 × (Tj 最大 - Tc 实际)/(Tj 最大 - 25)

核心参数解读与降额目标

降额设计必须围绕几个关键参数进行。比如对于三极管BJT来说,至少有以下三个关键参数

第一个是**集电极-发射极电压 Vce。**这是三极管在截止或放大状态下承受的主要电压。降额的目标是防止在电源电压过冲或感性负载尖峰时,Vce超过其额定值,导致二次击穿(Second Breakdown)而永久损坏。

**第二个是集电极电流 Ic。**这是流过三极管的主要工作电流。降额的目标是限制功耗和热量产生,同时避免电流过大导致键合线熔断或芯片过热。

第三个是**功耗 Pd。**这是三极管热设计的核心。Pd等于Vce*Ic。功耗直接决定了芯片的温升。

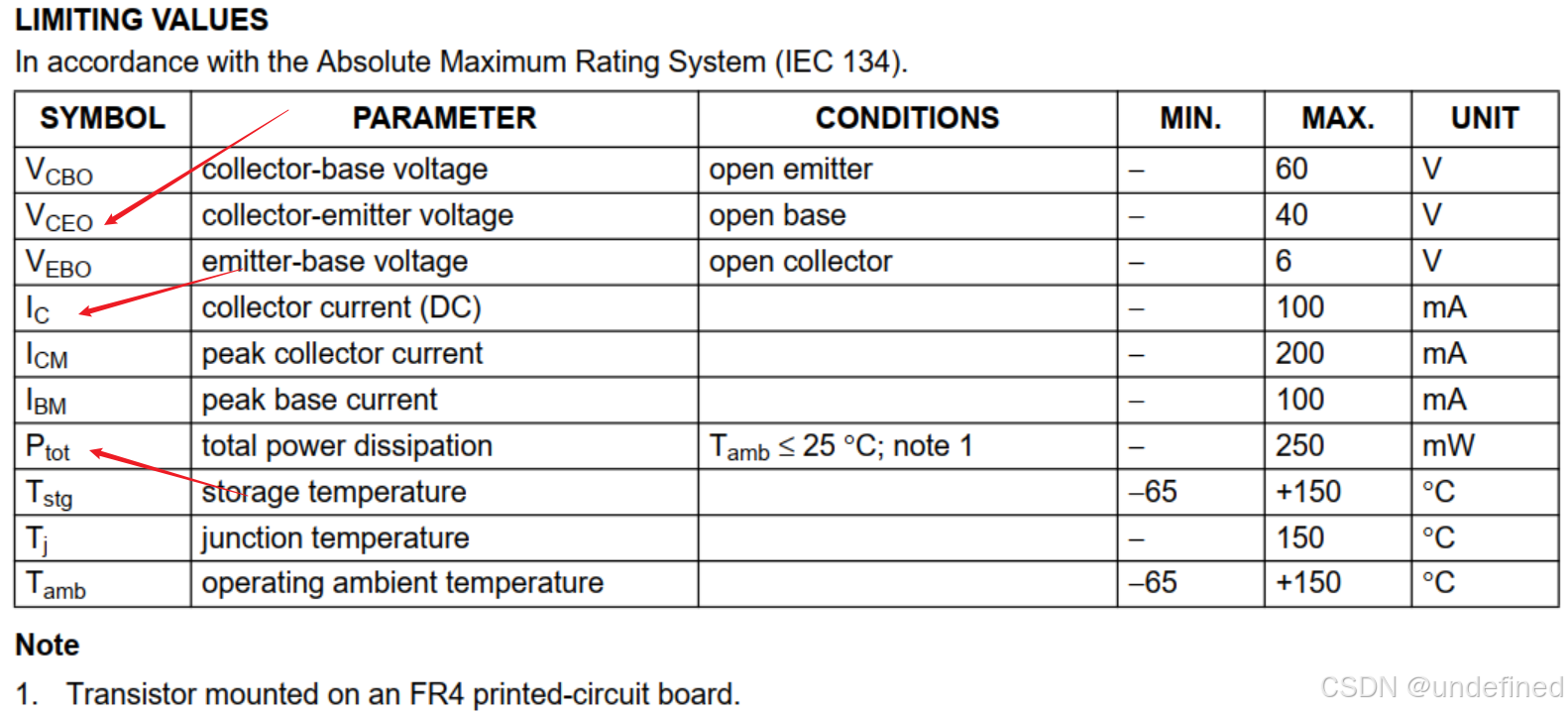

对应手册里面有很多描述,比如下面的极限参数的要求,absolute maximum表示任何情况下都不能超过的指标,但凡超过,元器件很可能就会快速损坏或失效。同时很多新手朋友会以这里的参数做设计,这是不对的,实际的设计经验是设计要远小于absolute maximum value才行,否则会出现各种问题。设计主要参考的是后面的推荐设计参数,并以此预留一个的余量,这样就能保证设计的安全和可靠。

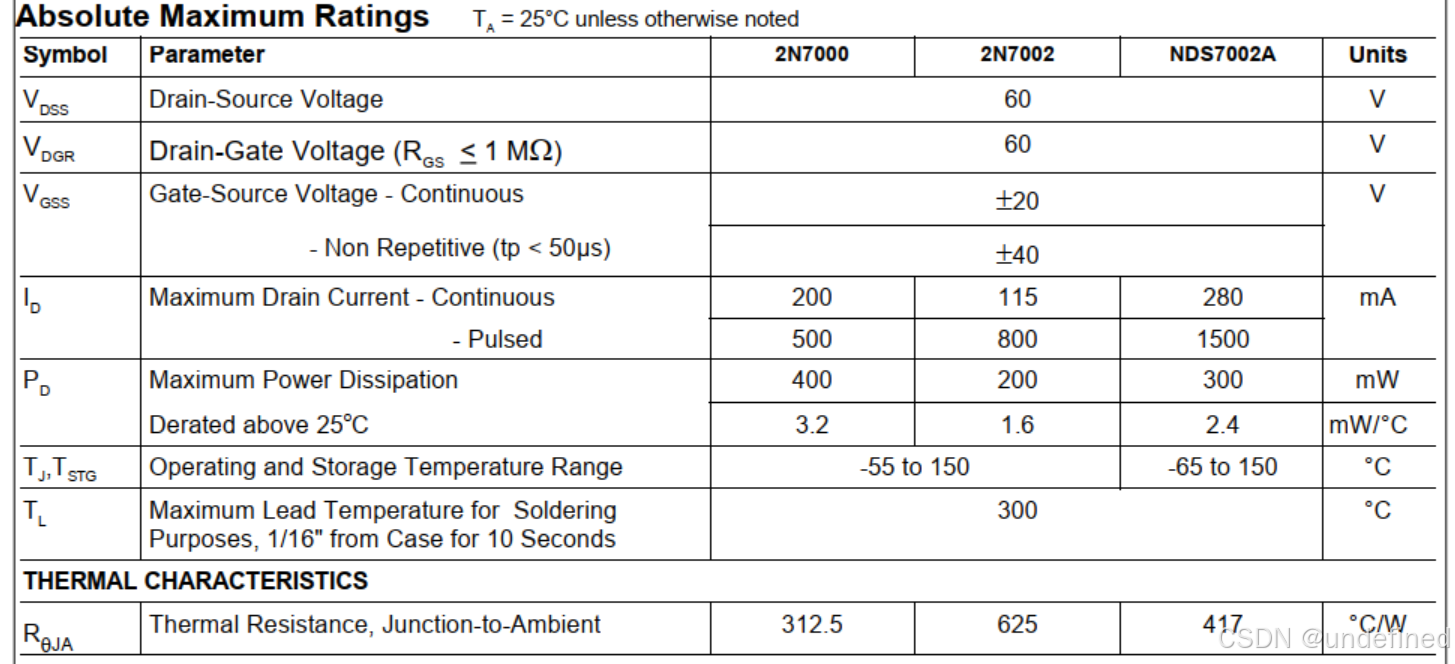

对于MOS管(MOSFET)对应有4个指标,多的一个是SOA, 即安全工作区,尤其对于功率MOS需要重点考虑。

**第一个是漏极-源极电压 Vds。**类似于Vce,这是MOS管关闭时承受的主要电压。必须为输入电压的尖峰和开关振铃(Ringing)预留足够裕量。

**第二个是漏极电流 Id。**虽然MOS管通常有很高的脉冲电流能力,但我们更应关注其连续电流能力和与之相关的功耗。

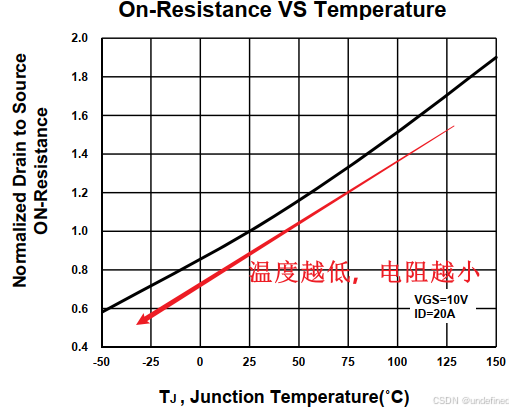

**第三个是导通电阻 Rds(on)。**这是MOS管作为开关时最重要的参数之一。它直接决定了导通损耗,并且具有很强的正温度系数,即温度越高,电阻越大,损耗也越大,形成恶性循环。

**第四个是安全工作区(SOA)。**这是MOS管最重要的图表。它定义了在不同Vds电压下,MOS管可以安全工作的最大Id电流和时间。任何时候,器件的工作点都不能超出SOA曲线的范围。每个手册中都有这个图,大家可以找一份仔细看看。SOA 安全工作区降额一般要求是:

热限制区域:降额率 0.8%/℃

二次击穿区域:降额率 0.5%/℃

温度降额系数:I 降额 = Isoa × (Tj 最大 - Tc 实际)/(Tj 最大 - 25)

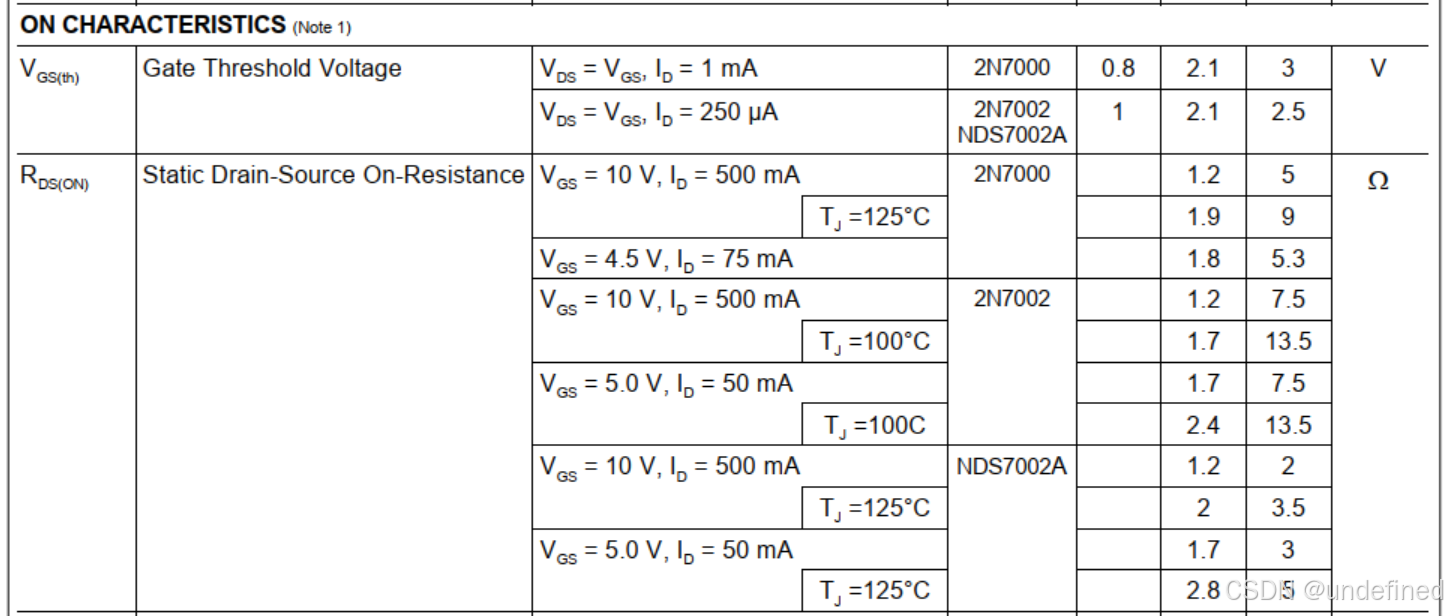

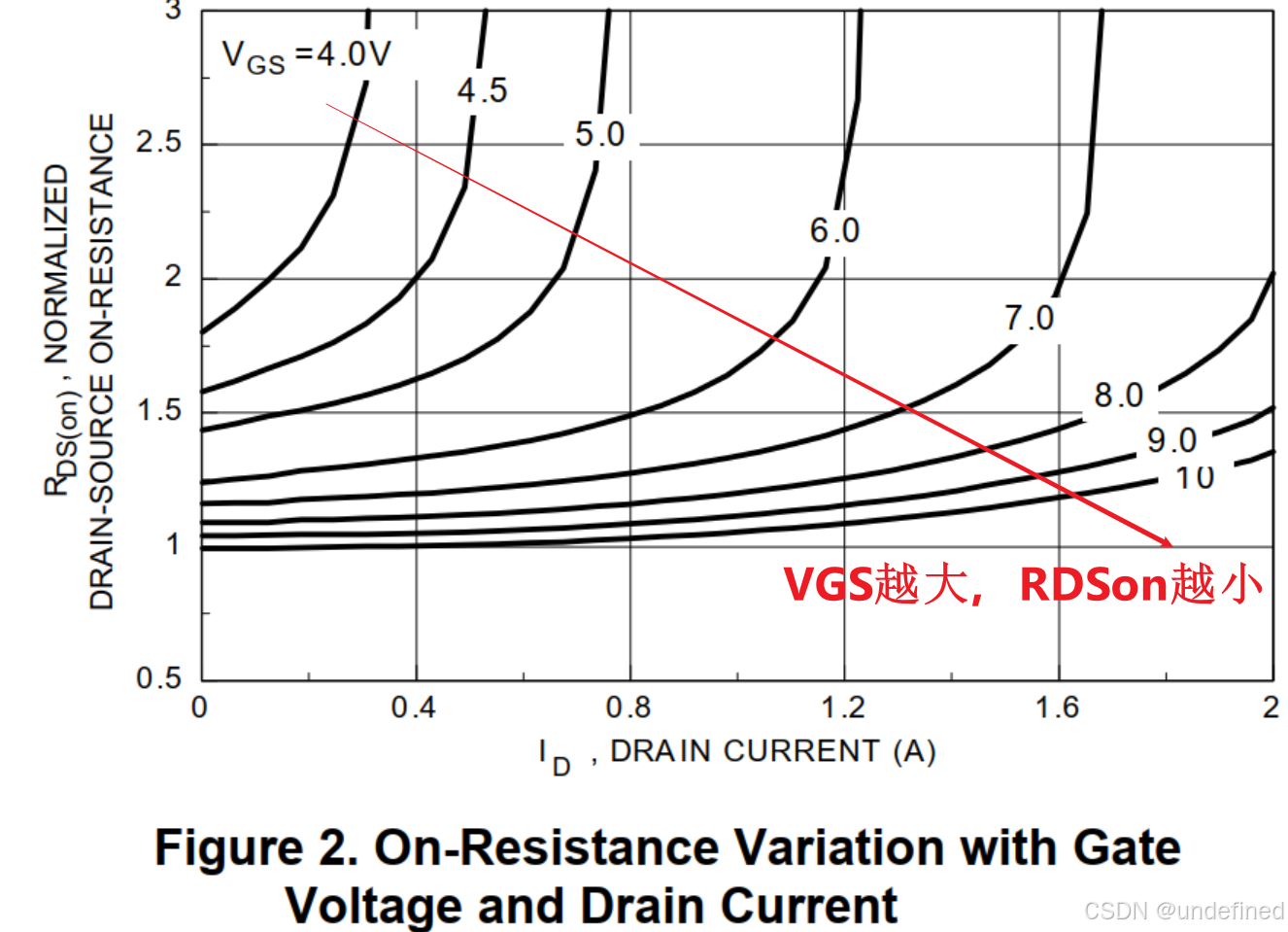

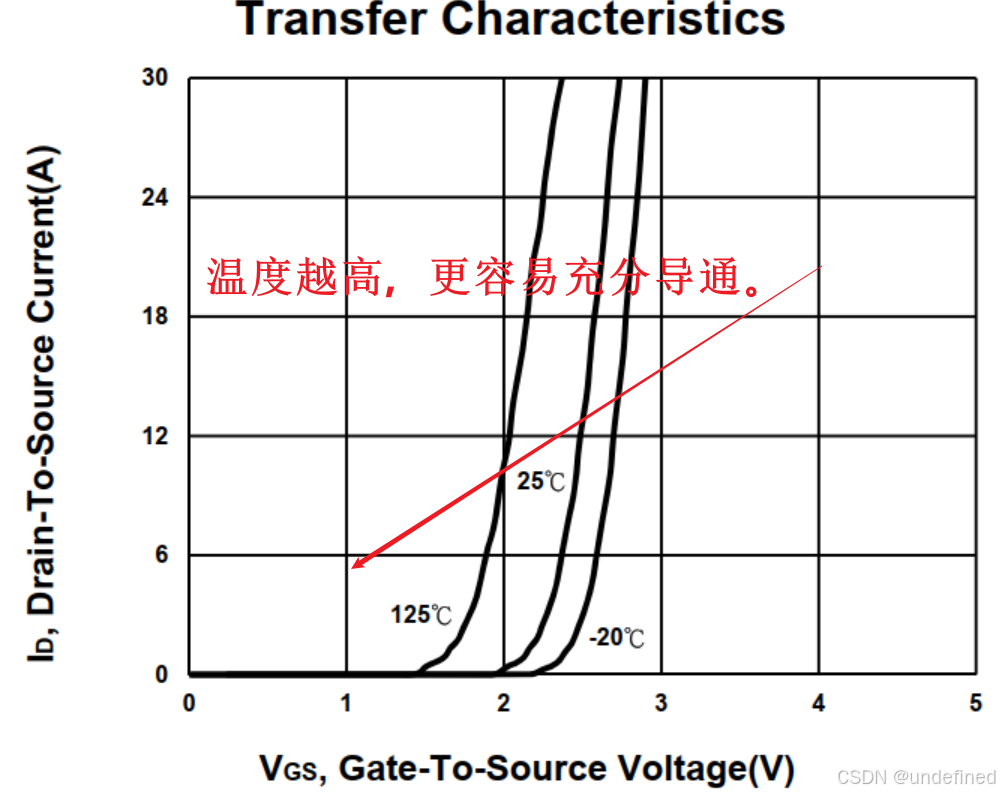

以上的几个参数是需要重点考虑的,但并不代表其他的参数就不重要了,比如还有VGSth表示MOS的打开电压,这个也要预留足够的余量,确保管子由于工艺制成能充分打开,而对于功率应用则需要这里电压比较大,保证能有更小的Rdson. 因为由下图可以看到VGS越大,电阻越小,这个对于开关功率应用是非常重要的。

也可以由这个图来理解,会更深入:VGS越大,Rdson越小。大家记住这个规律,实际非常有用。

4. 关键的计算公式

降额设计的核心离不开热量计算,而其基础是下面这个公式:

结温计算公式:Tj = Ta + Pd * Rth_ja

Tj: 芯片内部的结温(单位:°C),这是我们最终要控制的目标。一般建议控制在125°C以下,对于高可靠性应用甚至建议在110°C以下。

Ta: 环境温度(单位:°C),即设备所在环境的温度,需要考虑最恶劣的情况,如夏天封闭的机箱内部。

Pd: 器件的实际功耗(单位:W)。

Rth_ja (θja): 结到环境的热阻(单位:°C/W)。它表示器件每消耗1W功率,结温会比环境温度高多少度。这个值可以在数据手册中查到,它的大小极大地依赖于封装和PCB布局。

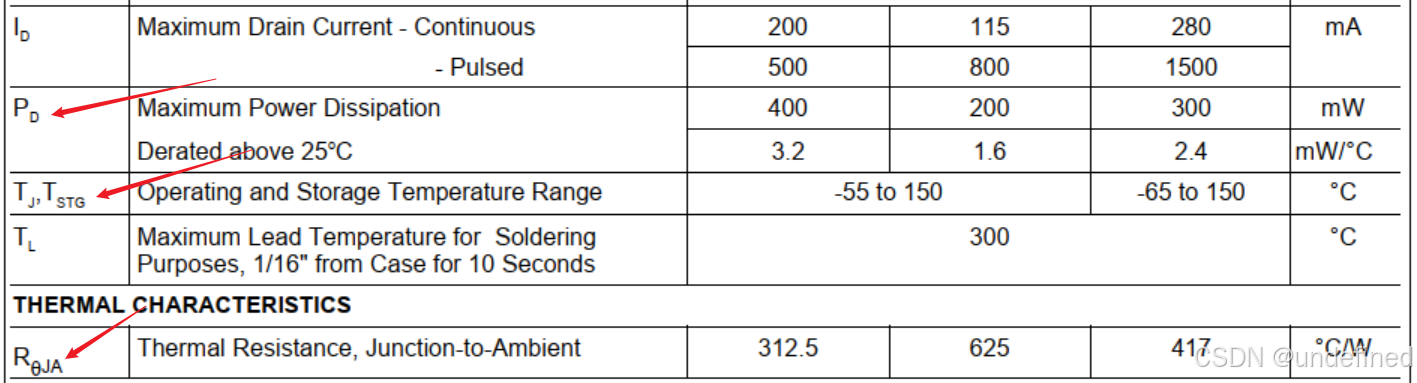

每个MOS管的datasheet里面都会明确标注相关的信息,如下图。根据这些信息结合实际场景的电流情况就能估算温度时候可控?

大家牢记上面的公式和方法,因为所有散热相关的计算和应用都是以此公式方法为基础,后面的电源,包括LDO和开关电源,芯片的功耗,散热,CPU/GPU的计算等等都是以此为基础展开的,本质和底层公式逻辑都一样。

二、案例拆解

理论可能比较枯燥,虽然我们尽量图标化让大家更好的理解,接下来我们通过几个用的最多最常见的案例,一步步对降额设计的应用进行拆解。

案例1:三极管线性稳压器的"热"问题

设计目标: 设计一个简单的线性稳压电源,将12V直流电压稳定到5V,为后级电路提供最大300mA的电流。框图大概如下

选型: 新手工程师小王选择了一款非常常见的NPN型功率三极管TIP41C。

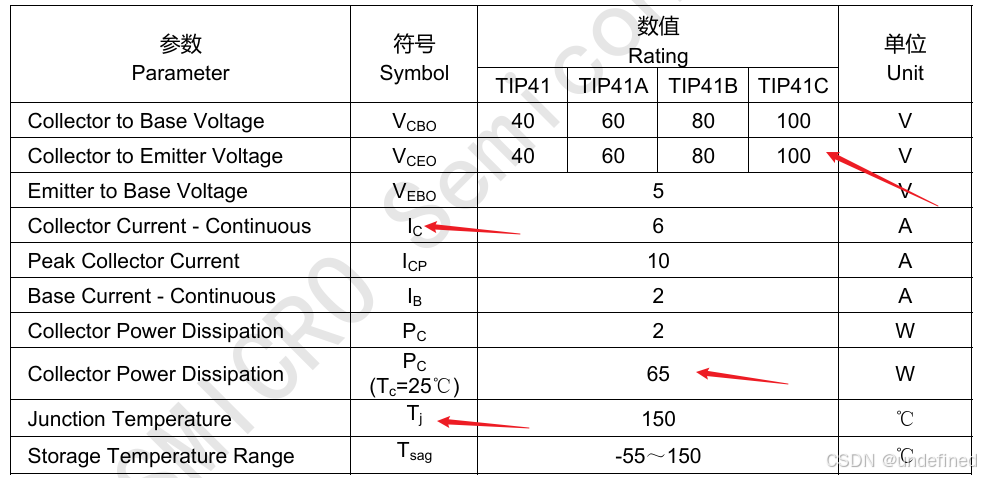

初步分析: 查阅TIP41C数据手册,关键参数如下:

Vceo_max: 100V

Ic_max: 6A

Pd_max: 65W (在Tc = 25°C时)

Tj_max: 150°C

Rth_jc: 1.92 °C/W (结到外壳热阻)

看起来,这个三极管的参数余量巨大,小王想着区区300mA的应用简直是大材小用,游刃有余。于是迅速搭建了电路,在实验室测试也一切正常。然而,产品在夏季的客户现场开始出现批量失效。

问题拆解与降额计算分析

-

实际工作Vce = 输入电压 - 输出电压 = 12V - 5V = 7V。LDO中这就是dropout, 实际中需要重点关注的参数。

-

Vce(7V) << Vceo_max(100V)。电压降额比例为7%,从这个方面来说是非常安全。

-

实际工作Ic = 300mA = 0.3A。且Ic(0.3A) << Ic_max(6A)。电流降额比例为5%,也非常安全。

但是,通过热应力分析(记住问题的关键):计算功耗Pd: Pd = Vce * Ic = 7V * 0.3A = 2.1W。

藏在数据手册的陷阱: 工程师小王看到了Pd_max高达65W,认为2.1W的功耗毫无压力,这是很多工程师最容易犯的错误,大家一定注意。因为他忽略了一个致命的条件:"at Tc = 25°C"。Tc是外壳温度,这意味着要实现65W的功耗,你必须有能力将三极管的外壳强制冷却并维持在25°C,这在实际应用中几乎不可能,也不现实的,因为管子一直在发热。

所以,必须要实际结温计算!注意,再强调一遍,必须通过实际的结温计算,即在没有散热器的情况下,我们需要用结到环境的热阻Rth_ja来计算。对于实际用得TO-220封装,在自然对流下,典型的Rth_ja约为62 °C/W。且假设机箱内最恶劣的环境温度Ta为50°C。

能快速得到:Tj = Ta + Pd * Rth_ja = 50°C + 2.1W * 62°C/W = 50 + 130.2 = 180.2°C!

因此有结论: 计算出的结温180.2°C,已经远远超过了其最大允许结温150°C。三极管必然会因过热而烧毁。这完美解释了为什么产品在冬天低loading状态下工作正常,但夏季高温环境下会批量失效。

**那么怎么解决呢?解决方案与重新设计思路。**我们的目标是将Tj控制在一个安全范围内,比如110°C,105°左右。

比如,当110目标所需总热阻 Rth_total_needed = (Tj_target - Ta_max) / Pd = (110°C - 50°C) / 2.1W = 28.6 °C/W。

大家注意,这个总热阻包括了Rth_jc(结到外壳)加上Rth_cs(外壳到散热器,通常为0.5-1°C/W)加上Rth_sa(散热器到空气)。

因此**所需散热器的热阻 Rth_sa = Rth_total_needed - Rth_jc - Rth_cs = 28.6 - 1.92 - 1 = 25.68 °C/W。**这意味着我们必须为TIP41C选择一个热阻小于25.68 °C/W的散热器,并使用导热硅脂良好安装,才能确保其在最恶劣环境下依然可靠工作。

通过安装散热器后,温度得到了解决。

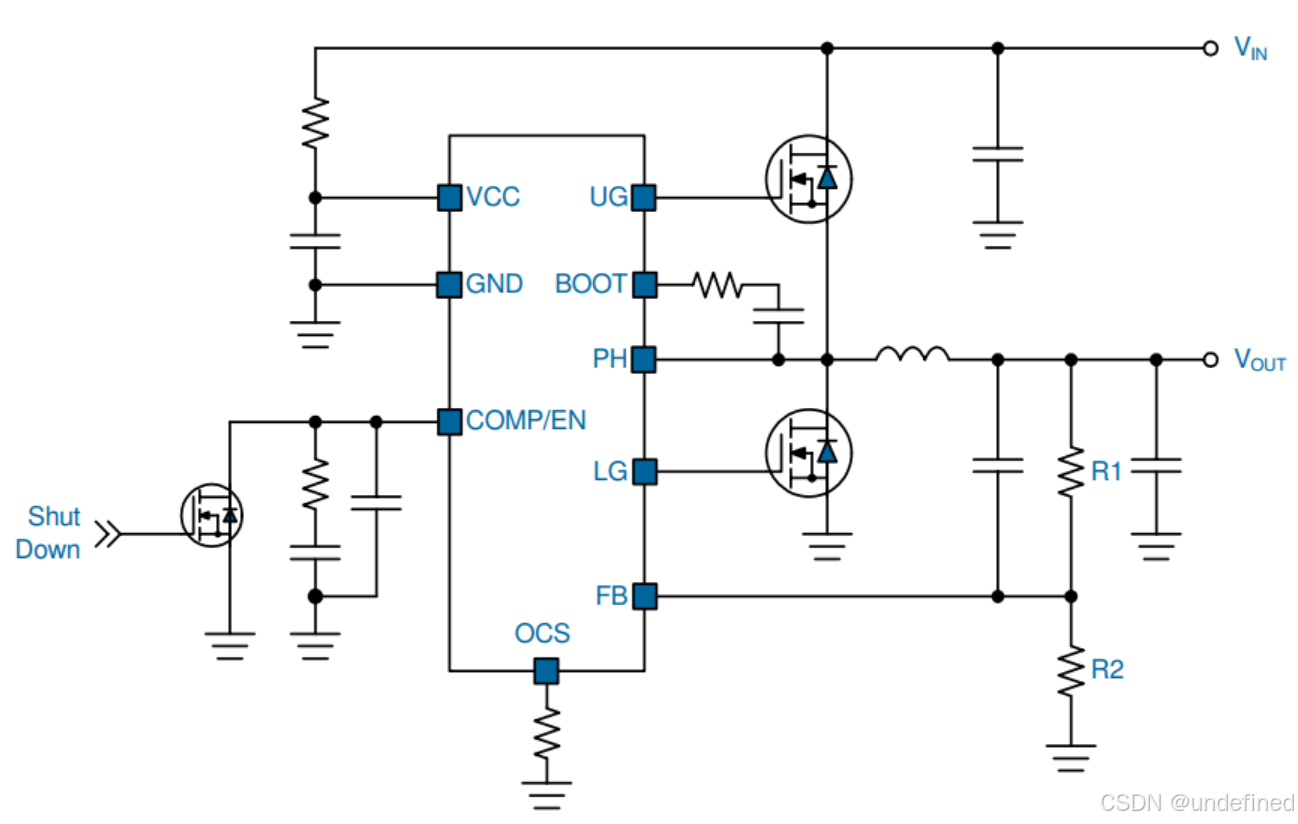

案例2:DC-DC降压转换器中MOS管的选型

设计目标: 设计一个同步Buck降压转换器,将24V输入转换为12V输出,负载电流为10A,开关频率f_sw为200kHz。大概的方案框图如下

选型: 工程师小李为高边(High-Side)和低边(Low-Side)都选择了一款N-Channel MOSFET,其关键参数如下:

Vds_max: 60V

Id_max: 80A (在Tc = 25°C时)

Rds(on)_max: 5 mΩ (在Vgs=10V, Tj=25°C时)

Rds(on)温度系数: 1.5倍 (在Tj=125°C时)

tr (上升时间): 15 ns, tf (下降时间): 10 ns

Rth_ja: 50 °C/W

问题拆解与降额计算:

首先对于工作Vds = 输入电压 = 24V。

Vds(24V) << Vds_max(60V)。电压降额比例为40%,考虑的开关尖峰,这个裕量是合理且必要的。

然后对于热应力分析,需要精细计算, 首先是占空比 D = Vout / Vin = 12V / 24V = 0.5。

接着预估工作结温: 在计算功耗前,我们需要先预估一个结温,因为Rds(on)与温度相关。我们先假设Tj为125°C。

接着计算在工作温度下的Rds(on): Rds(on)@125°C = Rds(on)@25°C * 温度系数 = 5 mΩ * 1.5 = 7.5 mΩ。温度越高,Rdson越小。

有以上的条件,可以计算高边MOS管(Q1)的功耗:

其导通损耗 P_cond_Q1: I_rms_Q1 = Iout * sqrt(D) = 10A * sqrt(0.5) ≈ 7.07A。

P_cond_Q1 = I_rms_Q1^2 * Rds(on)@125°C * D = 7.07^2 * 0.0075 * 0.5 ≈ 0.187W。

其开关损耗 P_sw_Q1: P_sw_Q1 = 0.5 * Vin * Iout * (tr + tf) * f_sw = 0.5 * 24V * 10A * (15ns + 10ns) * 200kHz

= 120 * 25e-9 * 200e3 = 0.6W。这里主要是开关损耗为主的,这也是上管选型需要重点考虑的对象。

所以,总功耗 P_total_Q1 = P_cond_Q1 + P_sw_Q1 = 0.187W + 0.6W = 0.787W。

计算低边MOS管(Q2)的功耗:

- 导通损耗 P_cond_Q2: 低边MOS管在(1-D)时间内导通,且电流为负载电流。

P_cond_Q2 = Iout^2 * Rds(on)@125°C * (1-D) = 10^2 * 0.0075 * (1-0.5) = 0.375W。

-

开关损耗 P_sw_Q2: 低边MOS管是零电压开通,开关损耗主要发生在关断过程,且有体二极管反向恢复损耗,此处为简化,我们先忽略这部分,认为其开关损耗远小于高边。

-

总功耗 P_total_Q2 ≈ P_cond_Q2 = 0.375W。下管主要是导通损耗,跟上管不一样,所以选型要重点关注Rdson。

**由以上的信息,就可以对结温验算:**先假设环境温度Ta为60°C,PCB布局良好,无额外散热器。

Tj_Q1 = Ta + P_total_Q1 * Rth_ja = 60°C + 0.787W * 50°C/W = 60 + 39.35 = 99.35°C。

Tj_Q2 = Ta + P_total_Q2 * Rth_ja = 60°C + 0.375W * 50°C/W = 60 + 18.75 = 78.75°C。

结论: 计算出的高边MOS管结温约为99.35°C,低于我们预估的125°C,也低于建议的安全上限110°C。这表明当前设计在热方面是安全的,降额是充分的。如果计算结果高于110°C,则需要考虑更换Rds(on)更低或开关速度更快的MOS管,或者通过优化PCB布局(增加散热铜皮)来降低Rth_ja。

启芯的建议:大家可以找几个类似的电源,自己算一遍,计算之后就能理解上管和下管该如何选择,上管和下管哪个以Rdson为主,哪个以Qg为主?为什么?

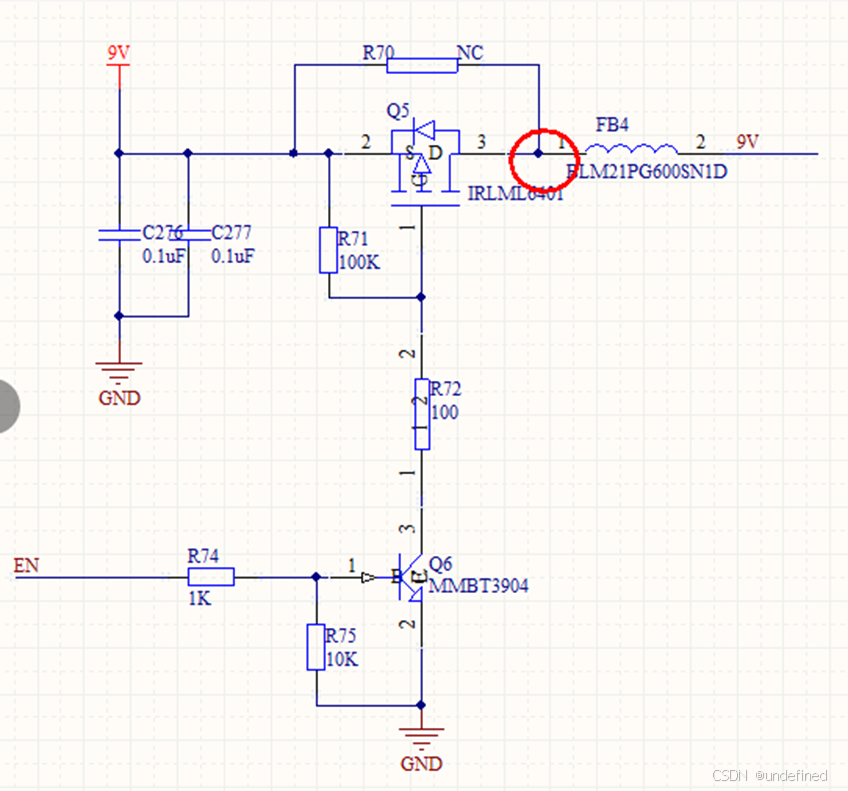

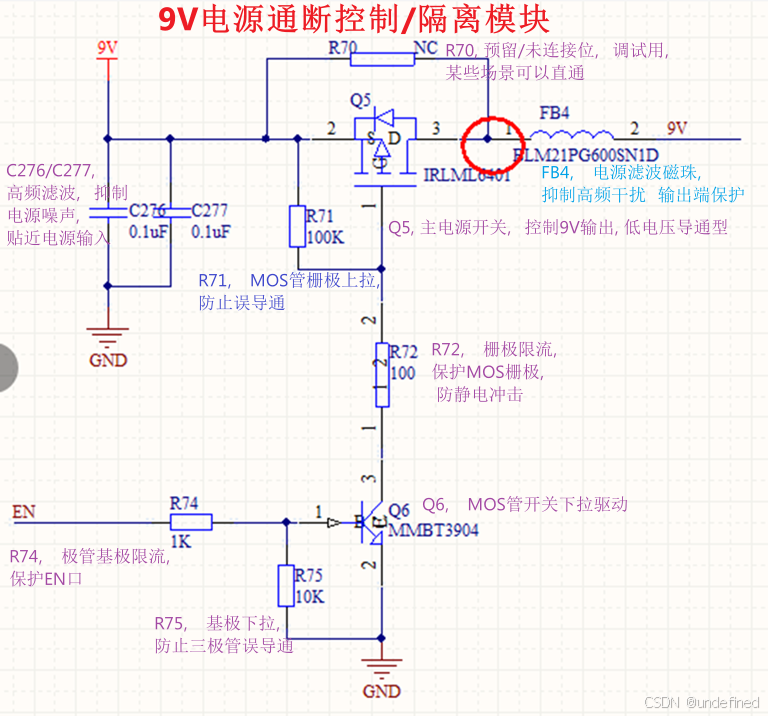

案例3:9V电源通断控制和隔离模块的电路分析

该电路为9V电源通断控制/隔离模块,采用N沟MOS和三极管进行有效电源管理,可实现低功耗控制与滤波保护。以下我会为每个元件的作用、整体电路的工作原理、工程建议等说明,以方便大家更好的理解。

首先,对于电路整体工作原理

C276/C277对9V电源输入进行高频滤波,提升输入电压稳定性及抗干扰能力。

Q5为P沟道MOSFET,从9V电源向后级输出提供主电源通断功能。当MOS管栅极被拉低时导通,9V通过FB4进入后级负载。

栅极正常由R71 100kΩ进行上拉,保持MOS管关断,防止悬空带来的误导通。

控制端EN信号经R74限流后驱动Q6,Q6导通时将MOS管栅极拉低,使Q5导通,实现电源输出。

R72为栅极限流,防止开关切换瞬间大电流损坏MOS管,保障门极安全。

R75将Q6基极下拉,防止由于EN端口浮空或干扰时三极管误导通。

FB4为输出端滤波磁珠,抑制高频噪声和电磁干扰,提升后级负载输入品质。

R70为预留调试/保护位,NC表示未装,不影响正常工作。

然后,如果需要优化,我的工程改进建议如下

根据实际MOS管型号与EN驱动电压,R71上拉、电流限流R72可适当调整至10k~470kΩ及10~100Ω,优化开关速度与抗干扰能力。这个实际根据测试去优化

如负载电流较大或干扰环境恶劣,可提升C276/C277容量至1μF,增加输出侧滤波。

三极管选型应与EN端口电平兼容,确保可靠驱动MOS管开关。

MOS管建议选型为低Rds(on)、高额定电流型号,提升通断能力及系统可靠性。

PCB布线应加宽9V主电源路径与地线,并保证MOS管、磁珠焊盘可靠接地。

若需实现反向隔离或输入反接保护,可加装肖特基二极管于输入侧。

最后,启芯小结:本电路可实现9V电源高效通断控制,具备良好的抗干扰与低功耗特性,应用于小型DC电源隔离、智能电源模块及系统时序管理场合。

三、工程问题与解决

问题1:MOS管在感性负载下,远低于额定电压和电流却频繁损坏

问题分析: 这通常是由于感性负载(如电机,继电器)在关断瞬间产生的反向电动势尖峰导致的。这个尖峰电压(Vds)会远超电源电压,瞬间突破MOS管的Vds_max,导致其发生雪崩击穿而损坏。即使尖峰能量很小,在SOA图上可能也已经超出了限制。

解决方法:

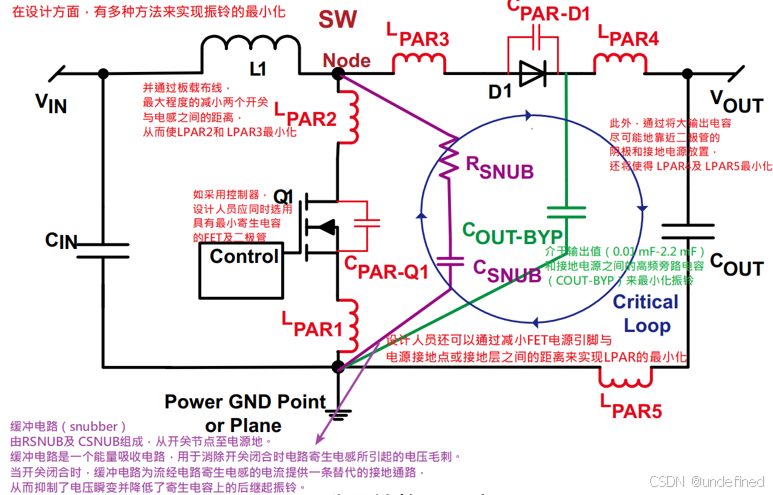

**方案1是增加吸收电路。**在MOS管的D-S两端并联一个RC缓冲电路(Snubber)或TVS二极管,用于吸收和钳位这个尖峰电压。Snubber的连接电路可以参考下面案例

**方案2采用续流二极管。**对于直流感性负载,最简单有效的方法是在负载两端并联一个高速的续流二极管(Freewheeling Diode)。

**方案3选择更高电压等级.**在设计初期就预估尖峰电压,选择Vds_max有足够裕量的MOS管,例如在24V系统中选用60V甚至80V的MOS管。

问题2:多个MOS管并联使用时,出现"链式反应"烧毁

问题分析: 并联MOS管是为了增大电流输出能力,降低ESR,这在很多常用应用非常多。但如果处理不当,会因为参数不一致导致电流分配不均。MOS管的Rds(on)有正温度系数,哪个管子温度略高,其Rds(on)就会变大(这个可以参考翻看前面贴的图),分担的电流会减小,这是一种负反馈,有利于均流,也就是温度高的低电流,温度低的大电流,从而保证电流和温度的平衡关系。然而,这里有一个危险的因素是其阈值电压Vgs(th)具有负温度系数,也就是温度越高的管子,在相同的驱动电压下会更早,更充分地导通,从而抢占更多的电流,导致自身温度进一步升高,形成热失控的正反馈,最终烧毁。如下图

解决方法有如下几个常用的推荐给大家

第一是分仓驱动,即每个MOS管的栅极(Gate)都独立串联一个小的电阻(如2.2-10Ω),这可以抑制并联时可能发生的寄生振荡,并轻微影响开通速度,帮助动态均流。注意这个电阻值需要实测,确保不影响MOS管的开通速度及正常工作。

第二是**PCB对称布局,**确保从驱动芯片到每个MOS管的栅极走线长度,宽度完全一致。并联MOS管的源极和漏极的走线也要做到尽可能对称,以保证静态阻抗一致。

第三是同批次选型,这个没做过实际量产项目的一般是无法理解的。原则就是尽可能选用同一品牌,同一批次的MOS管,以减小参数的离散性。

第四是热设计均衡。可以将并联的MOS管放置在同一块散热器或同一片大的散热铜皮上,确保它们工作在相近的温度,促进热均衡。这个在实际的板卡设计中应用也很多。

问题3:为什么我的MOS管驱动不足或驱动过慢?

问题分析: MOS管是一个由电压驱动的器件,其输入端是一个电容(Ciss)。要使其快速开通,驱动电路必须能提供足够大的瞬时电流来对这个输入电容充电。如果驱动电流不足(比如直接用微控制器的I/O口驱动),会导致开关上升/下降时间过长,极大地增加了开关损耗(见上面案例中的公式),从而导致MOS管过热。

解决方法:

使用专用栅极驱动IC: 对于需要快速开关的应用(如开关电源,电机驱动),必须使用专用的MOSFET栅极驱动器(Gate Driver)。它们能提供数安培的峰值拉灌电流,确保MOS管在纳秒级完成开关动作。

优化驱动环路: 驱动IC到MOS管栅极和源极的环路面积要尽可能小,以减小寄生电感,防止振荡。

总结与建议

降额设计是专业硬件工程师与业余爱好者的分水岭,它体现了对产品全生命周期的责任感。它不是一个孤立的步骤,而应贯穿于整个设计流程。

核心建议:

-

永远不要相信"最大额定值": 数据手册中的最大值是在极端理想条件下测得的,它们是器件的"生存极限",而非"工作推荐值"。大家要重点关注SOA图和各种条件下的典型值。

-

温度是最主要的失效原因: 任何功耗器件的设计,本质上都是热设计。精确计算功耗,并根据最坏情况下的环境温度,通过计算来验证结温是否在安全区内。

-

动态应力比静态应力更危险: 电压尖峰和电流冲击是器件的隐形杀手。必须对感性负载和高速开关应用中的瞬态过程给予足够的重视。

-

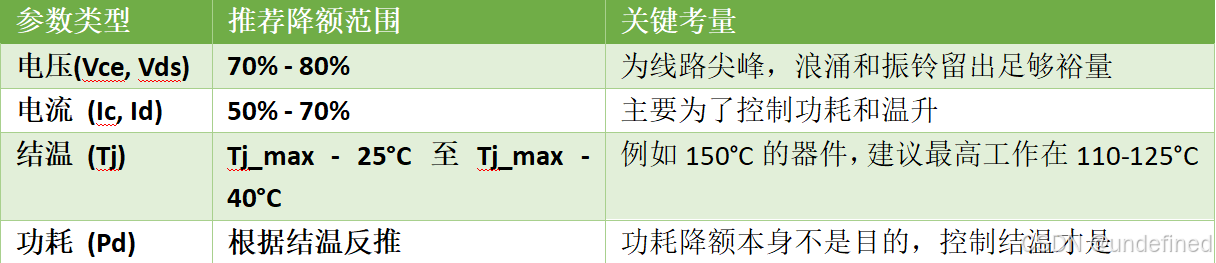

建立降额规范: 成熟的研发团队都有一套内部的降额标准。以下是一个通用的参考,可以根据产品的重要性和成本进行调整:

|------------------|---------------------------------|-----------------------------|

| 参数类型 | 推荐降额范围 | 关键考量 |

| 电压(Vce, Vds) | 70% - 80% | 为线路尖峰,浪涌和振铃留出足够裕量 |

| 电流 (Ic, Id) | 50% - 70% | 主要为了控制功耗和温升 |

| 结温 (Tj) | Tj_max - 25°C至Tj_max - 40°C | 例如150°C的器件,建议最高工作在110-125°C |

| 功耗 (Pd) | 根据结温反推 | 功耗降额本身不是目的,控制结温才是 |

- 仿真与实测结合: 在设计的早期阶段,使用热仿真工具可以帮助预测温度分布。在样品阶段,必须在高温箱中进行满载老化测试,并使用热像仪或热电偶实际测量关键器件的温度,以验证降额设计的有效性。

最后,把我常用的快速评估方案分享给大家,如何确定最优降额系数

1、工程实践经验:

消费电子产品:功率降额 70%,电压降额 80%

工业控制设备:功率降额 60%,电压降额 75%

汽车电子应用:功率降额 50%,电压降额 70%

军用/航天级:功率降额 40%,电压降额 60%

2、计算工具:

降额系数 = (额定参数 - 安全余量)/额定参数

安全余量 = 最恶劣工况参数 × 1.2(20%工艺裕量)

3、三极管降额设计关键参数至少满足

集电极电流降额至额定值的 70-80%

集电极-发射极电压降额至额定值的 80%

功耗降额至额定值的 60-75%

结温控制在 125℃以下(硅器件)

4、MOS 管降额设计关键参数至少满足

漏源电压降额至击穿电压的 80%

漏极电流降额至额定电流的 85%

栅源电压控制在±15V 以内

SOA 工作点保持 20%以上裕量

掌握了以上重要的降额设计,你才能真正从"把电路做出来"迈向"把产品做好"的更高层次。