#灵感# 苍天啊! 人为什么会遗忘

目录

[锁存器:(set_reset latch)](#锁存器:(set_reset latch))

组合逻辑电路:

组合逻辑电路:在电路结构上,只有门电路,不包含存储单元。

所以它任意时刻的输出只取决于该时刻的输入。

频繁使用的组合逻辑电路已变成标准化集成器件,比如加法器、选择器、编码器、译码器等。为了便于扩展,多数集成的中规模电路都 附加了控制端,(比如 使能端、片选端、禁止端等)

竞争-冒险现象(毛刺)是组合逻辑电路中由于工作状态改变,经常会出现的一种现象。

时序逻辑电路

指任意时刻的输出不仅取决于该时刻的输入信号,还取决于电路原来的状态(历史输入序列)。电路包含记忆元件,能够存储状态信息。

电路结构 由组合逻辑电路 + 存储元件(触发器、寄存器等)共同构成,存储元件用于记忆电路状态。

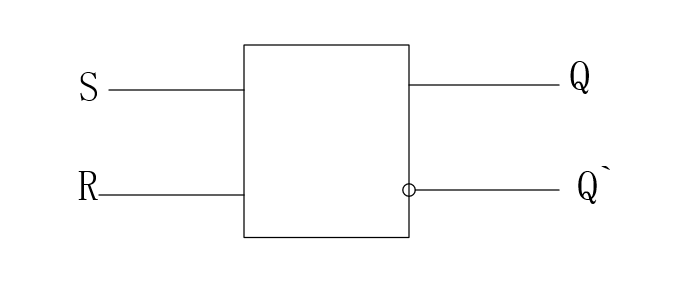

锁存器:(set_reset latch)

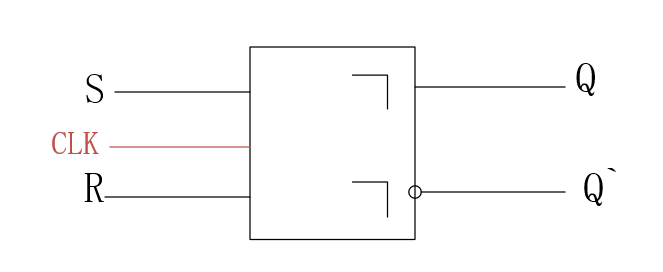

输入是 S R,输出Q Q`。 它的特点是输出的 Q Q`是直接由输入的 S R决定的。

遵守的约束条件是SR=0,即 S R不能同时为1.

当 S=1, R=0 时,Q=1 Q`=0;

当 S=0, R=1 时, Q=0 Q`=1;

当 S=0, R=0 时, 电路维持原来状态不变。

触发器:

定义:由触发信号触发,根据不同的输入信号,输出可以置为0或1。 触发器存储1位二值信号。

结构上:有两个可以自行稳定的状态,用来表示二值的0 或1 。

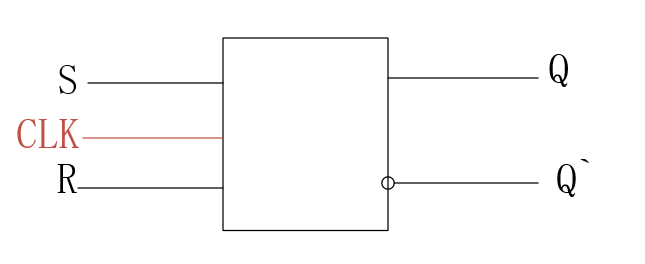

电平触发的SR 触发器,输入有3个, S 、R 、CLK, CLK 是触发信号即时钟信号clock 。当触发信号有效时,输出才能置成相应的状态。

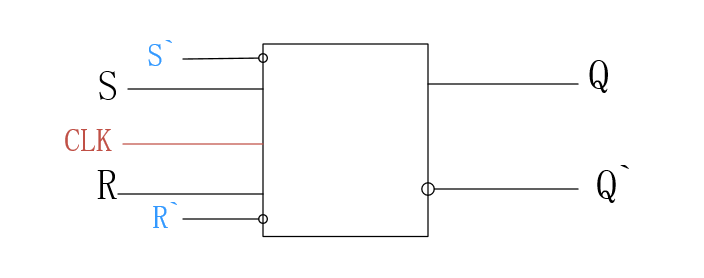

有时候,根据需要添加异步置位信号 S'、R', 当 S'为低电平时,触发器置为1,当 R' 为低电平时触发器置为0。当 S'、R'有效时,输出不受时钟信号、输入信号的控制。

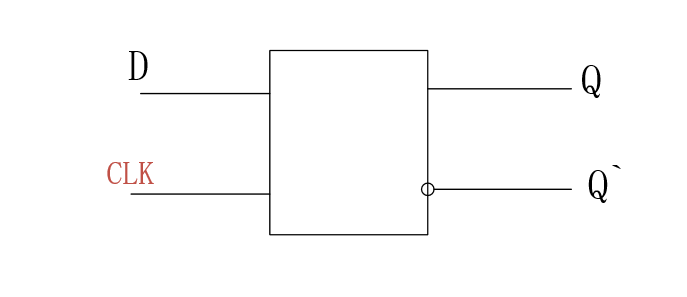

D触发器:只有一个输入信号D

D=1 时,如果CLK 为高电平,Q =1,CLK 再回到低电平后,Q=1 保持不变.

脉冲触发器:

脉冲触发器确保在一个完整的时钟周期内,输出端最多只发生一次状态变化,提高了触发器的可靠性。

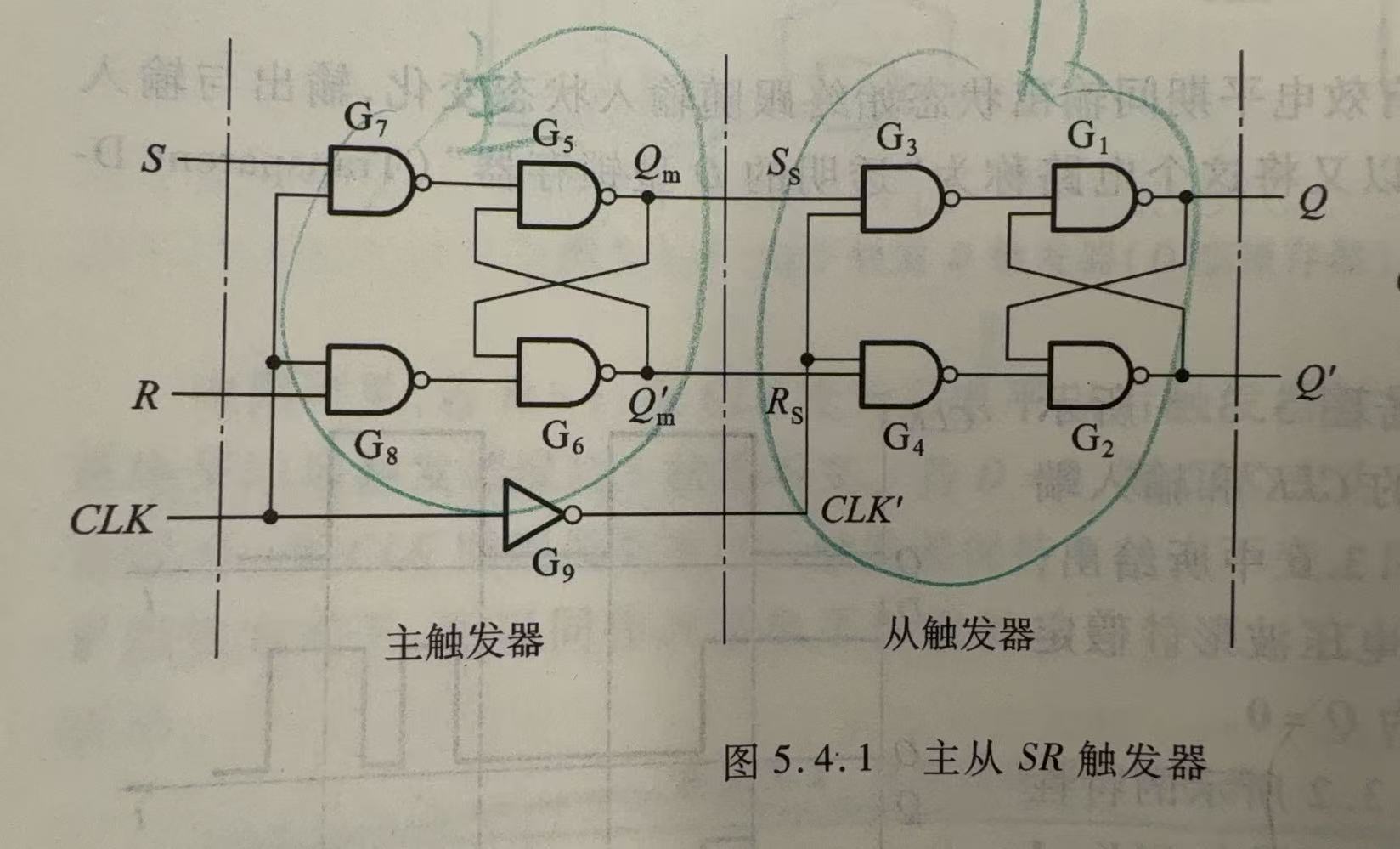

脉冲触发器通常采用主从结构。它由两个触发器组成,一个主触发器、一个从触发器。

其工作过程可以分为两个阶段:

-

主触发器采样阶段 :当时钟信号处于有效电平时(例如CLK=1),主触发器被激活,它会根据输入信号(如S、R)改变状态。从触发器被时钟信号封锁,保持原状态不变。

-

锁定与更新阶段 :当时钟信号发生跳变(例如CLK=0)时,主触发器 立刻被封锁,将其状态锁定,不再受输入信号变化的影响。同时,从触发器被激活,从触发器按照主触发器锁定的状态进行翻转,更新整个触发器的输出状态。因此整个触发器在一个时钟周期内,状态只更新了一次。

边沿触发器:

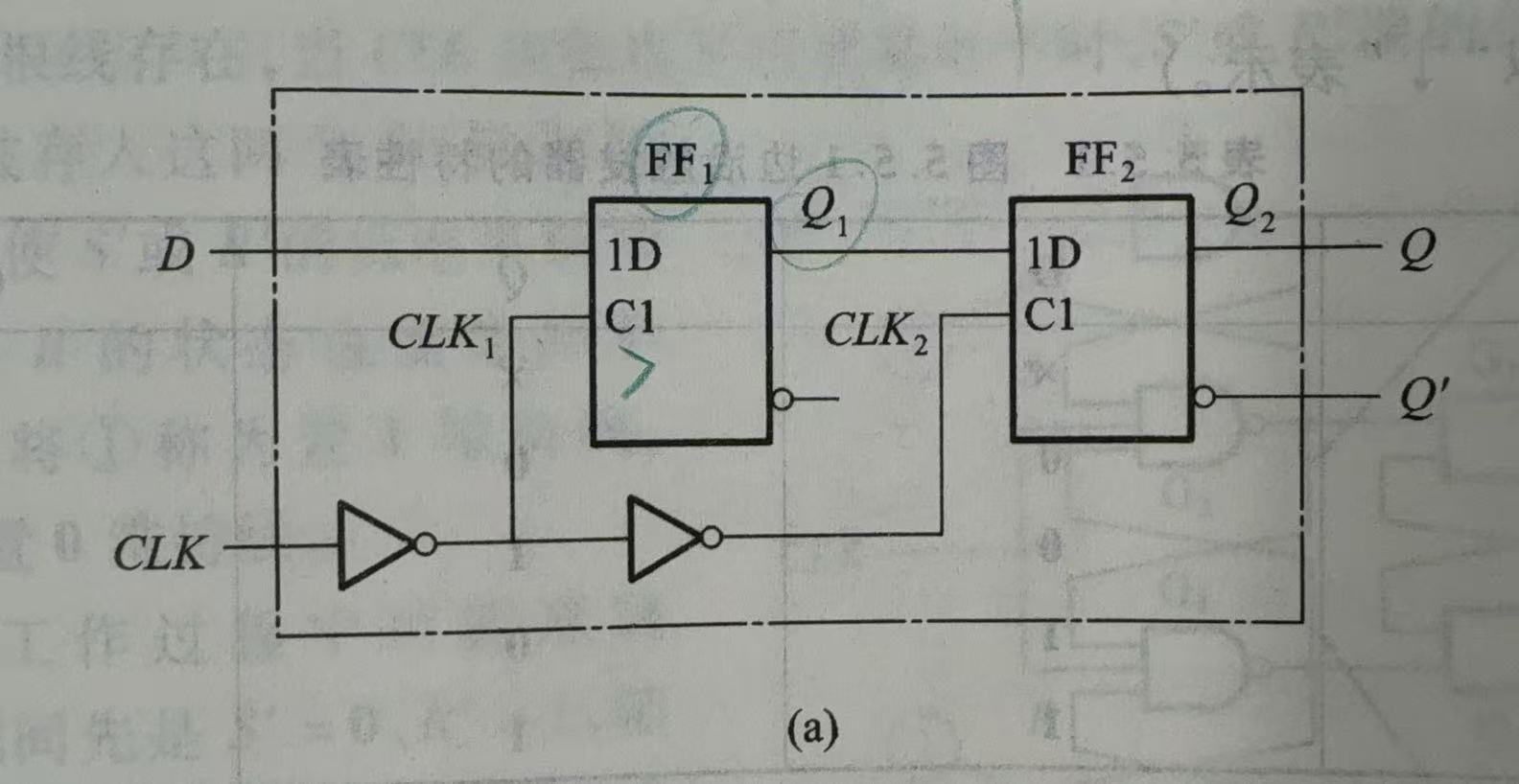

触发器的次态仅取决于CLK 下降沿(或上升沿)到达时,输入信号的状态。CMOS 电路常用 "由两个D触发器组成的边沿触发的触发器"。

两个D触发器叫 F1 和 F2。

CLK =0时,F1的输出Q1=D, F2的输出维持原状。

CLK =1时,F1的输出不变, F2的输出Q2=Q1。

因为是CLK=1时,触发器的输出改变,所以称为是"上升沿触发的" D触发器。

如果是下降沿触发的,CLK的输入端会标注一个小圆圈" 。"

触发器动态特性:

为了保证触发器在动态工作时翻转的准确性,输入信号、时钟信号的相互配合都有一定的要求。具体表现在对建立时间、保持时间、时钟信号宽度和最高工作频率的限制上。