IOPLL 分布差异

HSIO BANK 的 I/O bank IOPLL 与 PHY 电路紧密耦合,专为高速接口设计;而 HVIO BANK 的 IOPLL 不直接连接到 HSIO 的 PHY 电路

HSIO BANK 的 IOPLL 支持两种输入源:

1、专用 PLL 参考时钟树(低抖动、低延迟,时序性能最佳)

2、核心时钟网络(灵活性高,不受物理布局限制)

这两种输入源均支持接收来自 HVIO BANK 的参考时钟信号,但实现方式不同

关键技术细节

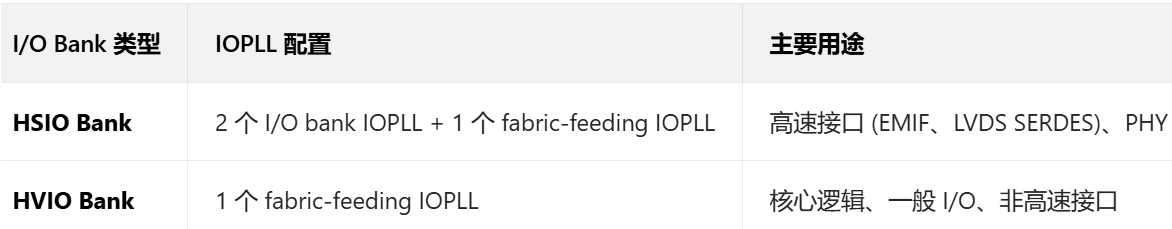

PLL 架构差异

每个 HSIO BANK 包含两个 I/O bank IOPLL和一个 fabric-feeding IOPLL,而每个 HVIO Block 仅包含一个 fabric-feeding IOPLL

HSIO BANK 的 I/O bank IOPLL 专为高速接口(如 EMIF、LVDS SERDES)设计,与 PHY 电路紧密耦合

HVIO BANK 的 IOPLL 主要用于驱动核心逻辑和一般 I/O,不直接连接到 HSIO 的 PHY 电路

专用 PLL 参考时钟树连接

Agilex 5 架构提供平衡的 PLL 参考时钟树,可跨多个相邻 HSIO BANK 和 HVIO BANK 分布

Quartus Prime 软件会自动配置该时钟树,确保参考时钟信号以低抖动方式到达所有连接的 PLL,这种连接方式仅适用于相邻且共享同一时钟树的 HVIO 和 HSIO BANK

核心时钟网络连接

HVIO BANK 的参考时钟首先通过 I/O buffer 进入 FPGA 核心

然后通过核心可编程时钟树(Programmable Clock Tree Synthesis)路由到目标 HSIO BANK 的 IOPLL

IOPLL IP 支持从核心时钟网络接收输入,可通过 IP 配置界面选择 "core clock input" 作为参考源

Agilex 5 FPGA 的 HVIO BANK 参考时钟可以作为 HSIO BANK 内部 IOPLL 的输入,但需根据芯片布局和性能要求选择合适的连接方式。专用 PLL 参考时钟树提供最佳性能,而核心时钟网络提供更高灵活性。