一、什么是 XDMA

XDMA(Xilinx Direct Memory Access)是 Xilinx FPGA 提供的一种高性能数据传输机制,它基于 PCI Express 总线,实现 FPGA 与主机内存之间的高速数据交换。与传统 DMA 相比,XDMA 支持以下优势:

-

高带宽传输:利用 PCIe Gen3/Gen4 总线,实现几 GB/s 的数据吞吐。

-

低延迟:支持分散-聚集(SGDMA)模式,高效管理连续或非连续内存。

-

灵活接口:支持用户逻辑访问(User)、控制寄存器访问(Control)等多种节点。

-

跨平台支持:提供 Linux、Windows 驱动与用户态 API。

XDMA 常用于高速采集、图像处理、AI 推理加速等需要频繁、大量数据交换的场景。

二、XDMA 在 Windows 平台的架构

在 Windows 下,XDMA 通常由三个主要部分组成:

-

FPGA 端硬件 IP

-

包含 XDMA IP 核

-

提供控制寄存器、SGDMA 通道、用户逻辑接口

-

-

Windows 驱动

-

提供标准的 PCIe DeviceInterface

-

支持

control、user、h2c(Host-to-FPGA)、c2h(FPGA-to-Host)访问

-

-

用户态应用

-

通过 SetupAPI 获取设备列表

-

打开设备 Handle (

CreateFile) -

调用

ReadFile/WriteFile或内存映射实现 DMA 读写

-

三、XDMA 节点与寄存器解析

XDMA 将设备分为若干逻辑节点,每个节点具有不同的功能:

每个节点支持**偏移(Offset)与长度(Length)**操作,配合 DMA 机制实现高速传输。

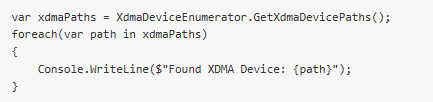

四、Windows 下获取 XDMA 设备列表

通过 Windows SetupAPI 可以枚举所有 PCIe XDMA 设备,并获取其接口路径:

核心步骤:

-

调用

SetupDiGetClassDevs获取设备信息集 -

使用

SetupDiEnumDeviceInterfaces枚举每个设备接口 -

调用

SetupDiGetDeviceInterfaceDetail获取设备路径 -

将路径用于

CreateFile打开设备

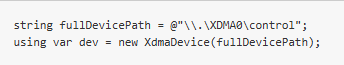

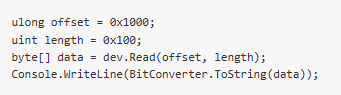

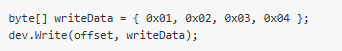

五、用户态数据读写实践

1. 打开设备

2. 读取数据

3. 写入数据

六、常见问题与注意事项

-

Stream does not support seeking-

出现该问题通常是直接使用

MemoryStream或FileStream读写时未正确定位偏移 -

在 XDMA 用户态实现中,需要使用

SetFilePointer或Seek定位

-

-

设备路径乱码

- 使用

Marshal.PtrToStringAuto或Unicode编码进行路径转换

- 使用

-

异步与性能

-

对大数据块(如 DDR 采集 10KB+)建议使用异步读取

-

避免阻塞 UI 线程,使用

Task.Run或后台线程

-

-

节点选择

- 根据 FPGA 逻辑决定使用

control、user或 DMA 通道

- 根据 FPGA 逻辑决定使用

七、实践经验

-

构建用户态测试工具时,可结合 WPF 实现:

-

下拉选择设备

-

下拉选择节点

-

输入偏移与长度

-

支持十六进制 / 十进制切换显示

-

实时显示原始数据日志

-

-

对于初学者,建议先从 控制寄存器 (

control) 读写开始,再扩展到 DMA 通道(h2c_x/c2h_x)。

八、总结

XDMA 为 FPGA 与主机间提供了高性能、灵活的数据通道。

在 Windows 平台,通过 SetupAPI 获取设备接口,并结合 ReadFile / WriteFile,即可实现用户态高速读写。

关键要点:

-

明确节点与偏移

-

处理 Windows 下的设备路径和句柄

-

界面显示与日志反馈要考虑十进制 / 十六进制切换

-

数据量大时注意异步与 UI 流畅性