【STM32G4-FOC】(1)STM32G431 之创建项目

【STM32G4-FOC】(2)STM32G431 之 TIM+ADC

【STM32G4-FOC】(3)STM32G431之三相互补 PWM

【STM32G4-FOC】(4)PWM 硬件触发 ADC 同步采样

【STM32G4-FOC】(5)DAC 受控输出闭环链路

【STM32G4-FOC】(5)DAC 受控输出闭环链路:基于同步采样的幅值与频率调制

-

- [1. 项目介绍](#1. 项目介绍)

-

- [1.1 实验目的与背景](#1.1 实验目的与背景)

- [1.2 硬件需求与外设分工](#1.2 硬件需求与外设分工)

- [1.3 软件架构](#1.3 软件架构)

- [2. CubeMX工程配置](#2. CubeMX工程配置)

-

- [2.1 创建新项目](#2.1 创建新项目)

- [2.2 TIM 配置](#2.2 TIM 配置)

- [2.3 ADC 配置](#2.3 ADC 配置)

- [2.4 DAC 配置](#2.4 DAC 配置)

- [2.5 工程配置](#2.5 工程配置)

- [3. 实验一:ADC 采样后 DAC 输出方波](#3. 实验一:ADC 采样后 DAC 输出方波)

- [4. 实验二:ADC 采样后 DAC 输出幅值可调的方波](#4. 实验二:ADC 采样后 DAC 输出幅值可调的方波)

- [5. 实验三:ADC 采样后 DAC 输出频率可调的方波](#5. 实验三:ADC 采样后 DAC 输出频率可调的方波)

- [6. 小结](#6. 小结)

1. 项目介绍

1.1 实验目的与背景

上一篇《 【动手学STM32G4】(16)PWM 触发 ADC 采样》基于 NUCLEO-G431RB 开发板完成了 PWM 触发 ADC 同步采样 的完整验证流程,实现了由定时器事件精确控制采样时序,并将三相电流数据稳定地传输至上位机进行可视化显示。本文在此基础上引入 DAC 输出,进一步构建从"采样 → 计算 → 波形输出"的闭环链路,为后续实现 SVPWM 与电流控制算法奠定基础。

在FOC控制中,电流环的控制频率通常与PWM频率相同,即每个PWM周期都执行一次电流环计算。但本节的目标并非直接驱动电机功率级,而是通过 DAC 输出可观测的模拟波形,对控制逻辑与调制算法进行"无功率级、低风险"的验证。与 PWM 相比,DAC 输出波形连续、直观,适合用示波器或上位机进行分析,不涉及死区、互补、驱动极性等功率级问题,非常适合在算法尚未完全成熟时进行调试、演示和阶段性验证。

本节采用分阶段递进的实验设计思路,逐步增加系统复杂度,实验分为三个层次:

-

流程打通阶段:

在 ADC1 完成三相电流采样之后,DAC 输出固定频率方波,用于验证 ADC → 运算 → DAC 的基本数据通路是否畅通;

-

受控反馈阶段:

引入简单的反馈关系,根据 ADC1 的采样结果动态调节 DAC 方波的输出幅值,从而验证采样数据参与控制计算的实时性与稳定性;

-

调制实现阶段:

根据 ADC1 的采样结果动态调节 DAC 方波的输出频率,从而验证采样数据参与控制计算的实时性与稳定性;

通过上述由简到繁的实验安排,可以在不依赖电机功率级、不引入复杂硬件风险的前提下,逐步验证控制算法的正确性与系统结构的合理性。最终形成的 DAC 输出调制逻辑,可无缝迁移至 PWM 占空比更新,为后续构建完整的 FOC 电流环与 SVPWM 驱动提供可靠依据。

1.2 硬件需求与外设分工

本实验基于 ST 官方的 NUCLEO-G431RB(STM32G431RBT6)开发板完成,主要观测手段包括:

- 示波器:用于观察 DAC 输出波形的频率、幅值和相位关系;

- 上位机(可选):用于辅助观察采样数据或调试变量。

为保证实验过程清晰、可验证,并便于后续从算法验证平滑过渡到实际电机控制系统,本节在硬件与软件结构设计上延续了前一节《 【动手学STM32G4】(16)PWM 触发 ADC 采样》的整体框架,仅在原有系统中新增 DAC 输出通道,而不改变已经验证可靠的 PWM 与 ADC 同步采样结构。

-

TIM1 的作用是 "时间主线",其配置与上节保持一致:

- CH1~CH3:三相 PWM 输出(本节不再关注其驱动功能,仅作为系统背景存在)

- CH4:用于在 PWM 周期内产生稳定的比较事件(CC4 event)

- CC4 event:作为 ADC1 注入组的外部触发源,确保三相电流采样在固定相位完成

-

ADC1 的作用是提供同步、可靠的三相采样数据,其配置与上节保持一致:。

- 注入组(Injected Group)采样

- 三个通道分别对应 Iu / Iv / Iw

- 触发方式为 TIM1_CC4 事件

- 采样频率与 PWM 周期严格同步

-

DAC 是新增的关键外设,在本节中 其定位并非驱动负载,而是作为控制算法输出结果的"可视化窗口"。

DAC 不参与闭环控制本身,而是镜像(mirror)FOC 内部关键变量,用于验证、调试和教学。

1.3 软件架构

在典型 FOC 系统中,电流环控制频率与 PWM 频率一致。每个 PWM 周期内,首先在电流纹波最小的时刻(通常为 PWM 中点)触发 ADC 同步采样;当 ADC 转换完成后,立即执行电流环计算,包括 Clarke / Park 变换、电流 PI 调节以及 SVPWM 调制计算;计算得到的占空比更新将作用于下一个 PWM 周期,从而形成具有固定、可预测延迟的闭环控制结构。

本实验虽然未直接实现电流环控制,但采用与标准 FOC 电流环一致的事件驱动型闭环结构。其核心思想是:以 PWM 周期为时间基准,以 ADC 注入采样完成事件作为控制计算与输出的触发点,从而形成固定、可预测的闭环时序。也为后续电流环计算的引入预留了完整且一致的控制框架。

从软件结构上看,整个闭环可划分为以下几个层次:

-

时间基准(PWM 定时层)

由 TIM1 产生固定频率的 PWM 周期,并在每个周期的预定时刻(通常为周期中点)通过 CH4 产生捕获比较事件。该事件作为系统中所有"强实时操作"的时间锚点,确保采样与控制在 PWM 周期内具有确定的相位关系。

-

同步采样(ADC 注入组)

ADC1 注入组以 TIM1_CC4 事件作为外部触发源,在 PWM 周期中点同步完成三相电流采样。ADC 转换完成后产生注入转换完成事件(JEOC),进入中断服务程序。至此,系统获得了当前 PWM 周期内最新、相位对齐的电流信息。

-

控制触发(ADC 回调驱动)

在 HAL_ADCEx_InjectedConvCpltCallback() 回调函数中,软件首先读取三相注入结果(JDR1/JDR2/JDR3),并将其视为当前控制周期的有效输入。随后,在同一回调中调用统一的控制/输出更新函数,用于推进后续控制逻辑或波形输出。

-

控制与输出(本实验中的 DAC 更新)

在当前实验阶段,控制层尚未实现完整的电流环计算,而是通过一个与采样事件同步调用的 DAC 更新函数输出固定频率的方波,用以验证"采样 → 计算 → 输出"的数据与时序链路。尽管输出内容简化,但其调用位置与真实电流环完全一致,逻辑上等价于在 ADC 采样完成后立即执行一次控制更新。

-

周期闭合与前馈延迟

由 ADC 注入回调触发的输出更新结果,将在随后的 PWM 周期中体现(无论是 DAC 波形变化,还是未来的 PWM 占空比更新),从而形成"本周期采样 → 下周期作用"的标准离散控制闭环。

由 DAC 外设输出模拟波形,通过示波器或上位机直接观察输出结果。该层用于验证控制计算的结果是否符合预期,是本节实验的核心观测对象。

在软件实现上,本实验采用以 PWM 为时间基准、以 ADC 注入完成中断为控制触发点的事件驱动闭环结构,实现了"同步采样---即时处理---下一周期生效"的完整控制时序,与标准 FOC 电流环的软件结构保持一致。

软件时序框图(ADC 同步采样后立即推进 DAC 输出)如下:

bash

PWM 周期(TIM1)基准

↓

TIM1_CC4(周期中点事件)

↓

ADC1 注入组同步采样(三相电流 Ia/Ib/Ic)

↓

ADC 注入完成中断 ISR(JEOC/JEOS)

↓

读取 JDR1/JDR2/JDR3

↓

更新 adc_snapshot(本周期电流快照)

↓

调用 DAC_Update_OnAdcInjected()

↓

DAC 输出更新(固定频率方波/调试波形)

↓

进入下一 PWM 周期2. CubeMX工程配置

2.1 创建新项目

-

新建工程。

启动 STM32CubeMX,点击 "Start New Project" (或Ctrl-N快捷键)新建工程,进入 New Project 界面。

选择MCU为 STM32G431RBT6(参考开发板的 MCU 型号选择)。

选择开发板为 NUCLEO-G431RB 开发板。

点击右上角 "Start Project" 创建项目,例如保存为 "STM32G431_DAC05.ioc"。

-

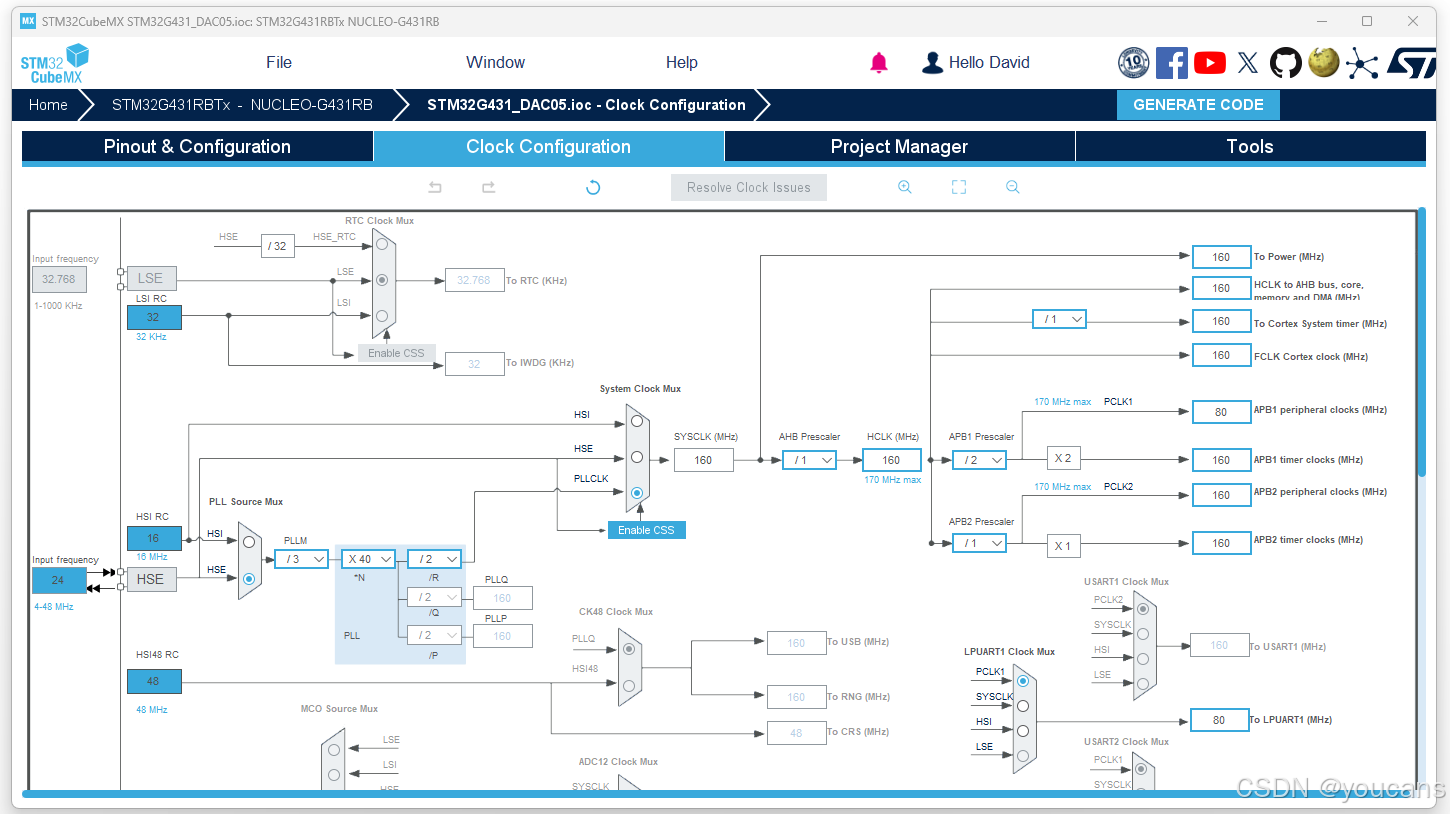

配置系统时钟树。

(1)点击顶部 "Clock Configuration" 选项卡,进入时钟树配置。

(2)设置输入频率 Input frequency=24 MHz,SysCLK frequency=160 MHz。

配置完成后,System Clock 显示为160MHz,HCLK、PCLK1、PCLK2 均为160MHz。

-

系统配置:在引脚配置(Pinout & Configuration)中,选择 "System Core -- SYS" 。

(1)设置调试器类型,将 Debug 模式设为 "Serial Wire"。

(2)设置基础时钟源(Timebase Source),可以选择默认设置 "SysTick"。

(3)时钟配置:在引脚配置(Pinout & Configuration)中,选择 "System Core -- RCC" 配置时钟模式。

设置高速时钟为外部晶振,将 High Speed Clock (HSE) 设为 "Crystal/Ceramic Resonator"。

Low Speed Clock (LSE) 设为 "Disable"(本实验不需要)。

-

GPIO 配置。

(1)将 LD2(PA5)配置为输出模式 "GPIO_Output"。

(2)将用户按键(PC13)配置为外部中断 "GPIO_EXTI13"。

-

配置虚拟串口(LPUART)

使用串口发送 ADC/DAC 数据到 PC 来显示波形:

启用 LPUART1,模式设为 Asynchronous;波特率设置为 115200;引脚使用默认的 PA2(TX)/PA3(RX),连接到 Nucleo 板上的 ST-LINK 虚拟串口。

用于高频率发送数据到上位机或更新波形时,可以为 LPUART1_TX 分配 DMA 通道。

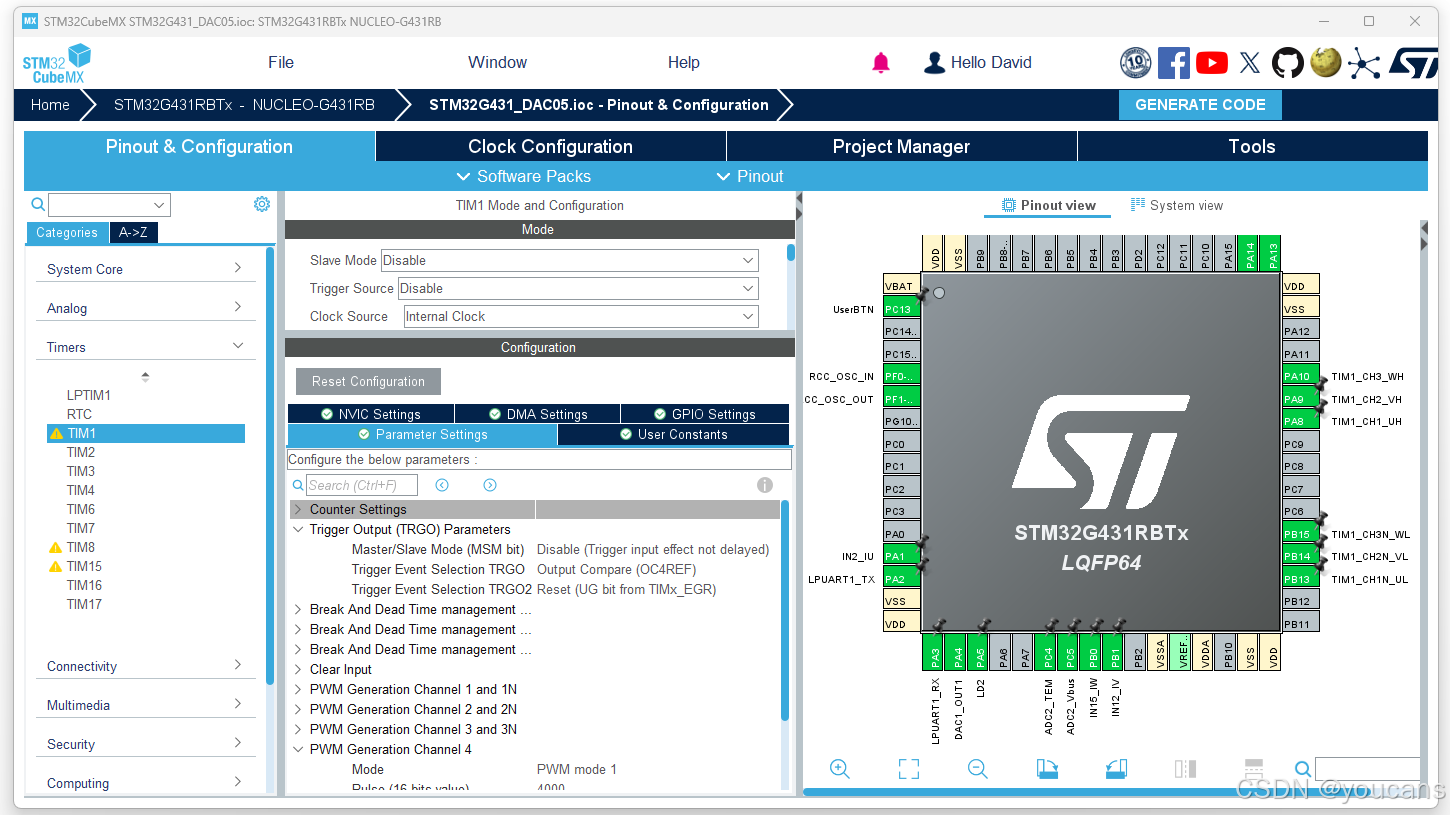

2.2 TIM 配置

- 配置定时器 TIM1 中断频率为 10kHz,产生 三相互补 PWM 波。

(1)配置 TIM1 管脚。

在右侧 Pinout View 图中,点击引脚打开设置选项 → 选择 TIM1_CHx / TIM1_CHxN 对应功能。TIM 具体设置如下:

bash

TIM1_CH1 → PA8

TIM1_CH2 → PA9

TIM1_CH3 → PA10

TIM1_CH1N → PB13

TIM1_CH2N → PB14

TIM1_CH3N → PB15(2)启用并配置TIM1。

选择 "引脚配置(Pinout & Configuration)",从左侧下拉列表中选择 "Timers -- TIM1 -- TIM1 Mode and Configuration ",配置 TIM1 Mode 如下:

bash

Clock Source 配置为: Internal Clock

Channel-1 配置为: PWM Generation CH1 CH1N(PWM 互补输出)

Channel-2 配置为: PWM Generation CH2 CH2N(PWM 互补输出)

Channel-3 配置为: PWM Generation CH3 CH3N(PWM 互补输出)

Channel-4 配置为: PWM Generation No Output(用于触发ADC采样)(3)TIM1 的具体参数配置与《 【动手学STM32G4】(16)PWM 触发 ADC 采样》相同。

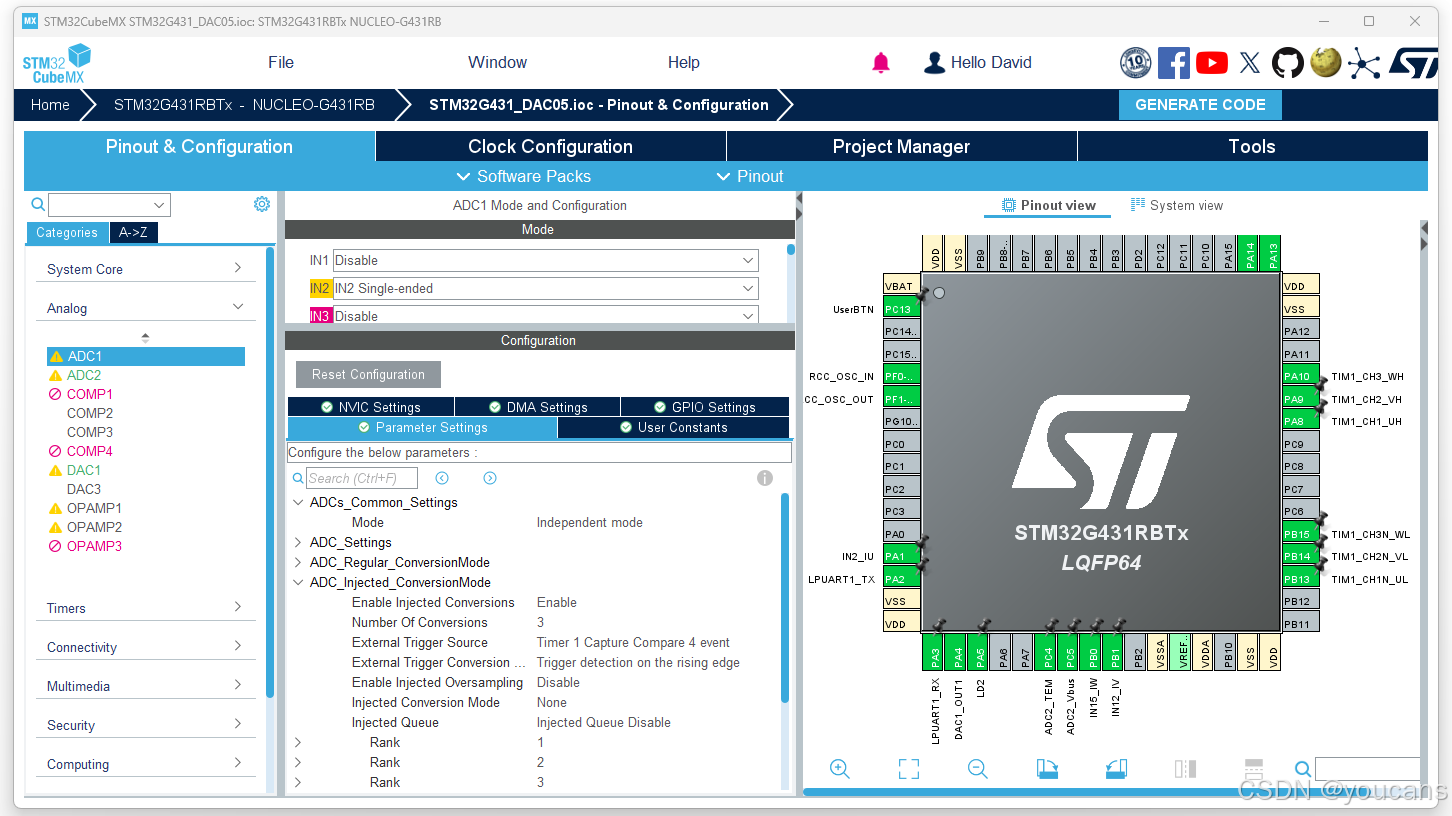

2.3 ADC 配置

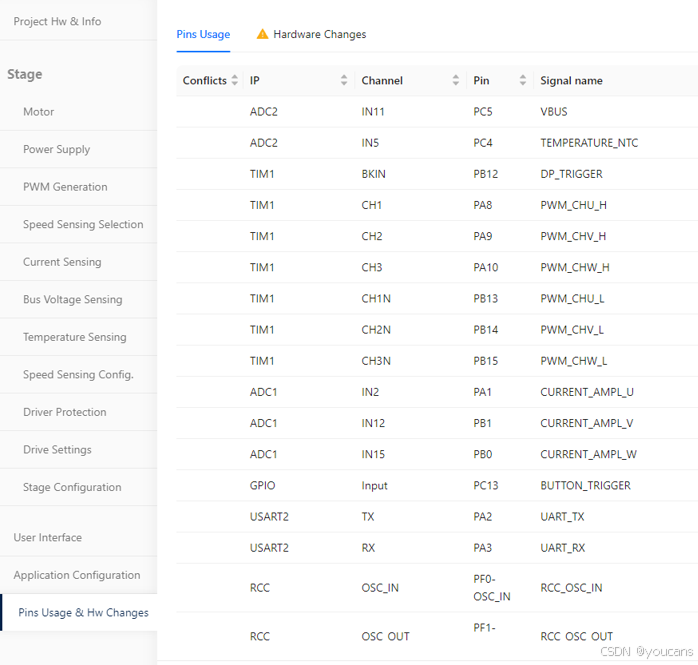

- 根据硬件原理图中的管脚定义,在右侧 Pinout View 图中设置 ADC 管脚如下。

bash

ADC1_IN2 → PA1(I_U)

ADC1_IN12 → PB1(I_V)

ADC1_IN15 → PB0(I_W)

ADC2_IN11 → PC5(Vbus)

ADC2_IN5 → PC4(Temp)ADC 的具体参数配置与《 【动手学STM32G4】(16)PWM 触发 ADC 采样》相同。

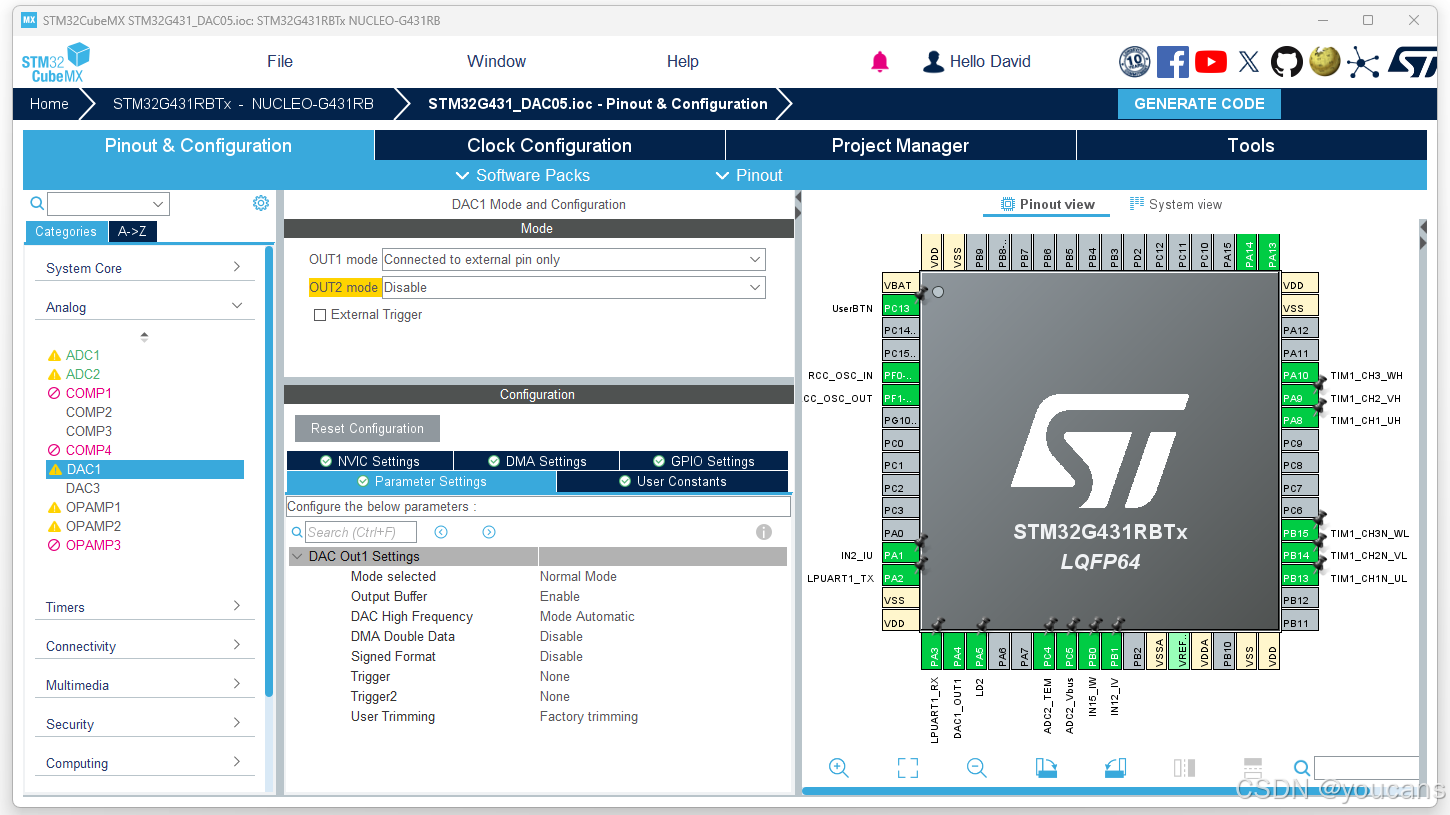

2.4 DAC 配置

- 使用 OUT1(PA4) 作为模拟输入通道,单通道模拟输出。

(1)从左侧下拉列表中选择 "Analog -- DAC1" ,将 OUT1 设置为 "Connected to external pin only"。工作模式和参数选择默认值即可。

(2)DMA 配置。虽然本实验可以使用 查询(Polling)方式读写 DAC,但考虑到后续连续采样或实时波形输出,可以为 DAC 配置 DMA。

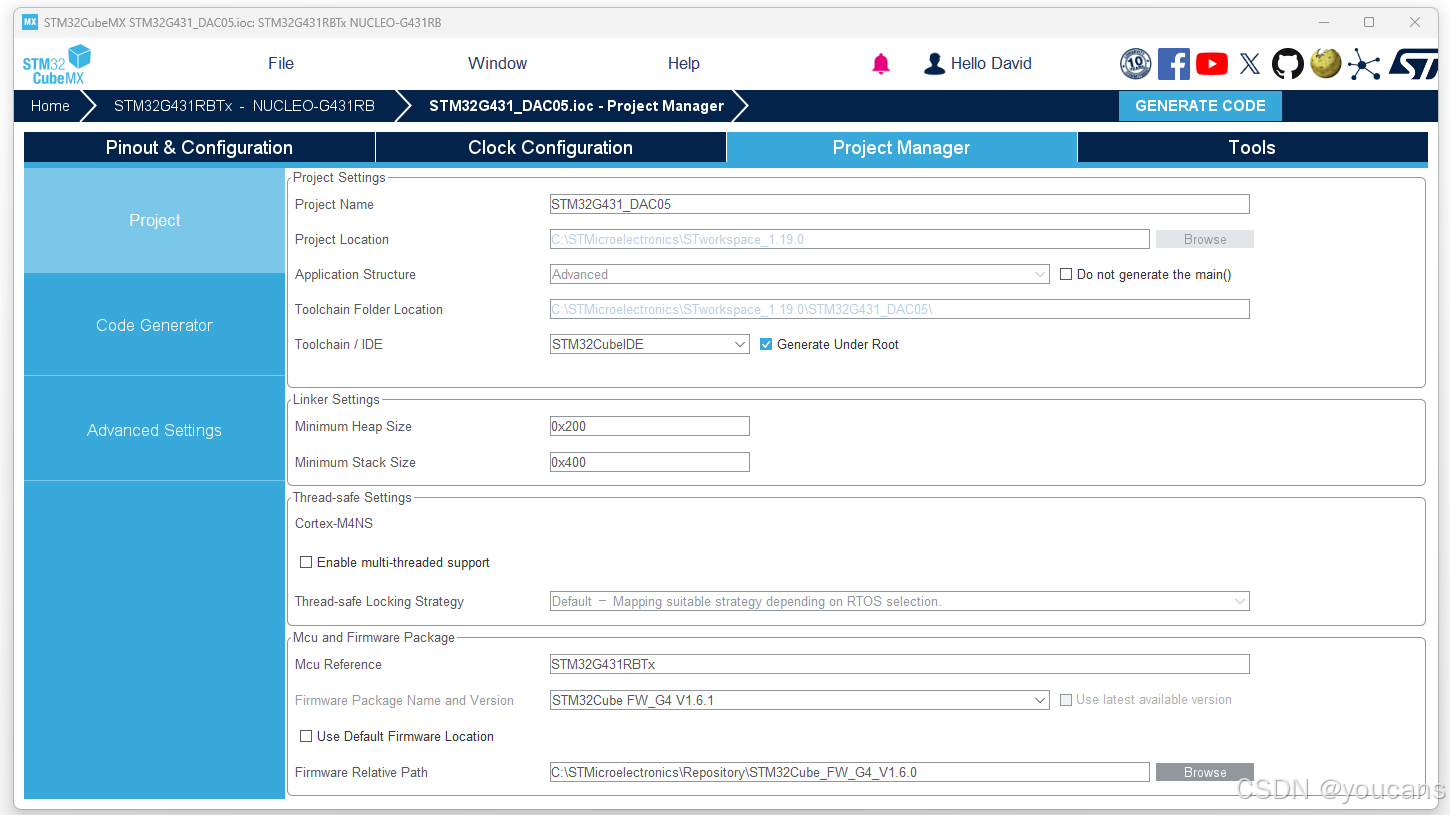

2.5 工程配置

- 点击 "Project Manager" 菜单按钮,进入工程配置界面。

(1)输入项目名称为 "STM32G431_DAC05",选择项目的保存路径。

(2)将Toolchain / IDE 设为 STM32CubeIDE(根据用户安装和使用的 IDE 选择,也可以选择 EWARM、MDK-ARM、MakeFile、CMake 等IDE工具)。

(3)点击右上角 "GENERATE CODE" 生成代码。

(4)加载完毕后,弹出代码生成提示窗口,点击" OPEN PROJECT",进入 STM32CubeIDE。

3. 实验一:ADC 采样后 DAC 输出方波

在上一篇《 【动手学STM32G4】(16)PWM 触发 ADC 采样》中,已经完成了 TIM1_CH4 触发 ADC1 注入组采样 的验证,并能够稳定获取三相电流采样值。本实验在完全保留该配置的前提下,引入 DAC 输出,用于验证从"同步采样 → 数据读取 → 波形输出"的基本流程是否畅通。

需要强调的是,本实验并不使用 ADC1 的采样结果参与 DAC 波形计算,DAC 输出为固定频率、固定幅值的方波。这样设计的目的在于:将验证目标聚焦在系统数据流是否打通,而非控制算法本身;为后续基于采样结果调制 DAC 波形(实验二、三)提供一个稳定的参考起点。

-

在 STM32CubeIDE 打开代码文件 main.c。

代码生成后,已经自动进入 STM32CubeIDE,并打开创建的 STM32G431_DAC05 项目。在 "Core\Src" 目录中,已经生成了 dac.c 和 main.c 等基础程序。

-

修改 main.c 代码。

以下代码仅给出与本实验相关的新增或关键逻辑,TIM1、ADC1 的初始化与配置沿用(16)节内容。

(1)全局变量

c

/* USER CODE BEGIN PV */

typedef struct {

uint16_t iu;

uint16_t iv;

uint16_t iw;

} adc3_u16_t;

volatile adc3_u16_t adc1_latest = {0};

/* Youcans@qq.com CODE END PV */(2)ADC1 注入回调

c

/* ADC1 injected conversion complete callback (JEOS/Injected sequence complete) */

void HAL_ADCEx_InjectedConvCpltCallback(ADC_HandleTypeDef *hadc)

{

if (hadc->Instance == ADC1)

{

// 用 LED2 观察触发节拍

HAL_GPIO_TogglePin(LD2_GPIO_Port, LD2_Pin);

adc1_latest.iu = (uint16_t)HAL_ADCEx_InjectedGetValue(hadc, ADC_INJECTED_RANK_1);

adc1_latest.iv = (uint16_t)HAL_ADCEx_InjectedGetValue(hadc, ADC_INJECTED_RANK_2);

adc1_latest.iw = (uint16_t)HAL_ADCEx_InjectedGetValue(hadc, ADC_INJECTED_RANK_3);

adc1_new = 1; // optional

DAC_Update_OnAdcInjected(); // 采样完成后同步推进 DAC

}

}说明:

- 本实验中并不使用 adc1_latest 的数值,但保留读取过程,以确保采样链路真实存在;

- 后续实验将直接复用这一回调。

(3)DAC 初始化与启动(CubeMX 生成)

生成代码后,在 main() 中启动 DAC:

c

HAL_DAC_Start(&hdac1, DAC_CHANNEL_1); // DAC Start(4)固定频率方波输出逻辑

以下示例以 1000 Hz 方波 为例(周期 1 ms):

c

#define ADC_TRIG_FREQ_HZ 10000U

#define DAC_SQ_FREQ_HZ 1000U // DAC 输出方波频率 1KHz

#define DAC_MAX_VALUE 4095U // 12-bit DAC

#define DAC_TOGGLE_DIV (ADC_TRIG_FREQ_HZ / (2U * DAC_SQ_FREQ_HZ))

void DAC_Update_OnAdcInjected(void)

{

dac_div_cnt++;

if (dac_div_cnt >= DAC_TOGGLE_DIV)

{

dac_div_cnt = 0;

dac_state ^= 1;

uint32_t out = dac_state ? DAC_MAX_VALUE : 0;

HAL_DAC_SetValue(&hdac1, DAC_CHANNEL_1, DAC_ALIGN_12B_R, out);

}

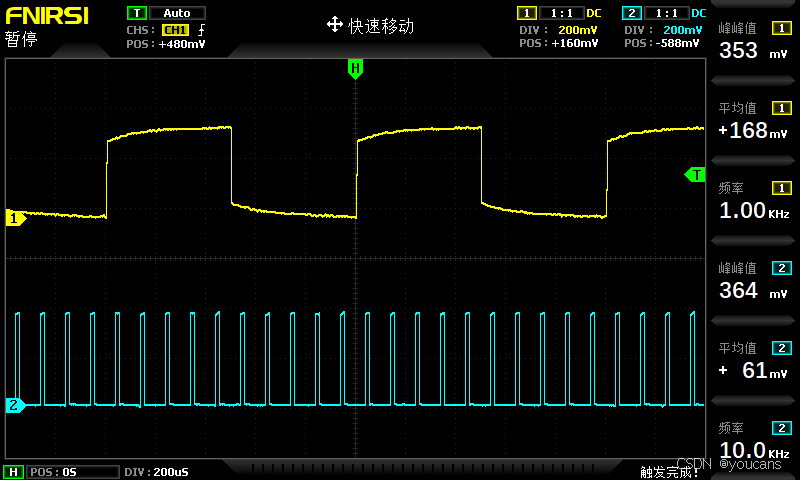

}- 实验现象与结果分析

实验运行后,用示波器测量 PA4 引脚波形。如图所示,生成频率 1 KHz、幅值在 0 ~ VDDA(约 3.3 V) 之间切换的方波(黄色曲线),结果符合预期。

作为参照,PA8 引脚的波形是频率 10 KHz、占空比 20% 的方波(蓝色曲线),与 《(16)PWM 触发 ADC 采样》中一致。

通过本实验,系统在保持 PWM 触发 ADC 同步采样结构不变的前提下,成功引入了 DAC 输出,并验证了从"采样 → 数据读取 → 波形输出"的基本流程。该阶段不关注控制算法本身,而是确保系统已经具备在采样之后产生可观测输出的能力。在此基础上,下一步即可引入采样数据与输出波形之间的反馈关系,实现更加接近实际控制行为的实验设计。

4. 实验二:ADC 采样后 DAC 输出幅值可调的方波

本实验引入控制量随采样值变化的可视化输出,用于验证电流采样结果能够实时参与后续控制计算并作用于输出端。

由于当前尚未连接真实电机功率级,因此本实验通过外部电位器为 ADC1 的 I_U 通道提供 0~3.3V 的可控输入,以模拟电流采样值的变化(或堆叠插接 NUCLEO-IHM16M1 电机驱动扩展板后,通过 PC2 引脚连接到 NUCLEO-IHM16M1 驱动板上的板载旋钮电位器来进行调节)。

在软件结构上,本实验仍严格沿用与标准 FOC 电流环一致的闭环时序:由 PWM 周期中点触发 ADC1 注入组同步采样,在 ADC 注入转换完成中断中读取采样结果,并在同一回调中推进 DAC 输出更新。与实验一的区别在于,DAC 输出不再是固定幅值的方波,而是保持方波频率恒定(1 kHz),其高电平幅值由 IU 通道的采样结果实时决定。

- 修改程序 main.c。

以下代码仅给出与本实验相关的新增或关键逻辑,其它部分与实验一相同。

(1)宏定义:

c

/* Private define ------------------------------------------------------------*/

/* USER CODE BEGIN PD */

#define ADC_TRIG_FREQ_HZ 10000U // ADC1 注入触发频率(与 PWM 同步)

#define DAC_SQ_FREQ_HZ 50U // DAC 方波频率:50Hz

#define DAC_MAX_VALUE 4095U // 12-bit DAC

#define DAC_TOGGLE_DIV (ADC_TRIG_FREQ_HZ / (2U * DAC_SQ_FREQ_HZ))

/* Youcans@qq.com CODE BEGIN PD */(2)修改 DAC 更新函数(幅度随 Iu 变化):

c

void DAC_Update_OnAdcInjected(void)

{

static uint16_t div = 0;

static uint8_t hi = 0;

uint16_t amp = adc1_latest.iu; // 幅值由 Iu 决定(0..4095)

// 分频产生固定 1kHz 方波翻转节拍 Youcans@qq.com

if (++div >= DAC_TOGGLE_DIV)

{

div = 0;

hi ^= 1;

uint16_t out = hi ? amp : 0; // 高电平输出 amp,低电平输出 0

HAL_DAC_SetValue(&hdac1, DAC_CHANNEL_1, DAC_ALIGN_12B_R, out);

}

}(3)ADC 注入回调与实验一相同。

c

void HAL_ADCEx_InjectedConvCpltCallback(ADC_HandleTypeDef *hadc)

{

if (hadc->Instance == ADC1)

{

adc1_latest.iu = (uint16_t)HAL_ADCEx_InjectedGetValue(hadc, ADC_INJECTED_RANK_1);

adc1_latest.iv = (uint16_t)HAL_ADCEx_InjectedGetValue(hadc, ADC_INJECTED_RANK_2);

adc1_latest.iw = (uint16_t)HAL_ADCEx_InjectedGetValue(hadc, ADC_INJECTED_RANK_3);

DAC_Update_OnAdcInjected(); // 实验二:1kHz 方波,幅值随 Iu 变化

}

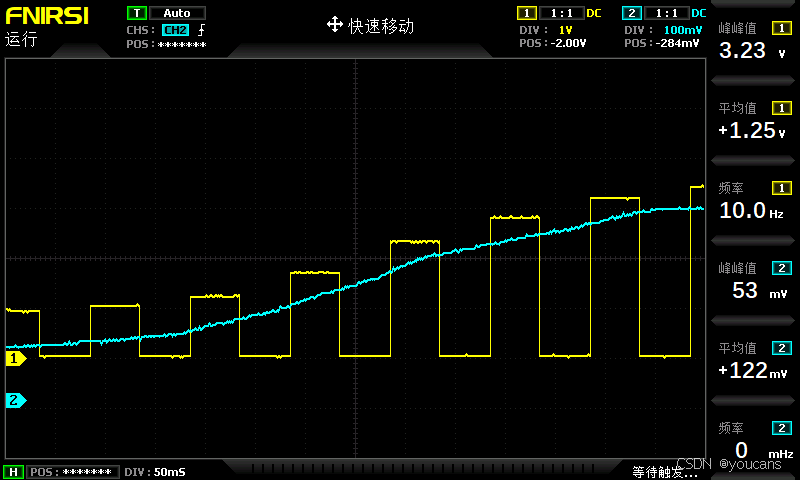

}- 实验现象与结果分析

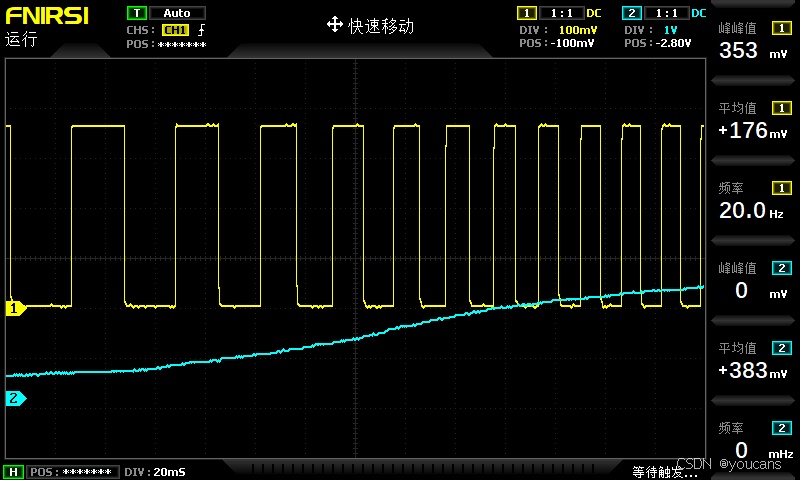

实验运行后,用示波器测量 ADC 采样 I_U 波形(蓝色曲线)和 DAC 输出 PA4 引脚波形(黄色曲线)。如下图所示,调节电位器时,输入电压 I_U 缓慢增大,DAC 输出方波的峰值电压也随之增大,变化过程与输入电压保持良好对应关系。

这说明 ADC1 同步采样、数据读取以及 DAC 输出更新已经构成一条完整、实时的闭环链路。尽管本实验尚未引入实际的电流环计算和调节算法,但在结构和时序上已经等价于标准 FOC 中"采样完成后立即计算并输出控制量"的控制流程,为后续基于电流计算控制量、输出 SVPWM 波形奠定了可靠基础。

5. 实验三:ADC 采样后 DAC 输出频率可调的方波

本实验进一步验证使用 ADC 采样值调制输出频率(FM):保持 DAC 方波幅值恒定,利用 IU 的 ADC 采样值实时改变 DAC 方波频率,从而在示波器上直观看到"输入变化 → 频率变化"的控制效果。这一步在概念上更接近后续 SVPWM/电角速度调制中"频率/相位推进"的思想。

- 修改程序 main.c。

以下代码仅给出与本实验相关的新增或关键逻辑,其它部分与实验一相同。

(1)宏定义:

为了示波器可直观看到变快/变慢,设置频率范围 10~100 Hz。

c

/* Private define ------------------------------------------------------------*/

/* USER CODE BEGIN PD */

#define ADC_TRIG_FREQ_HZ 10000U // ADC 注入回调频率(与 PWM 同步)

#define FREQ_MIN_HZ 10U

#define FREQ_MAX_HZ 100U

#define DAC_MAX_VALUE 4095U // 固定幅值(高电平)

#define TOGGLE_DIV_MIN (ADC_TRIG_FREQ_HZ / (2U * FREQ_MAX_HZ)) // 50

#define TOGGLE_DIV_MAX (ADC_TRIG_FREQ_HZ / (2U * FREQ_MIN_HZ)) // 500

/* Youcans@qq.com CODE BEGIN PD */(2)修改 DAC 更新函数(频率随 Iu 变化):

c

void DAC_Update_OnAdcInjected(void)

{

static uint16_t div_cnt = 0;

static uint8_t hi = 0;

// 动态分频系数(由 IU 决定)

static uint16_t toggle_div = TOGGLE_DIV_MAX;

// 1) IU 低通滤波(抑制电位器抖动/噪声)

// y += (x - y)/16 -> 右移4位

static uint32_t iu_f = 0;

uint32_t x = (uint32_t)adc1_latest.iu; // 0..4095

iu_f = iu_f + ((x - iu_f) >> 4);

uint32_t iu_smooth = iu_f; // 0..4095 附近

// 2) 频率更新节流:每 10 次回调更新一次(约 1 kHz 更新率)

static uint8_t update_cnt = 0;

if (++update_cnt >= 10)

{

update_cnt = 0;

// IU -> 目标频率 f: 10..100 Hz Youcans@qq.com

uint32_t f = FREQ_MIN_HZ +

(iu_smooth * (FREQ_MAX_HZ - FREQ_MIN_HZ)) / 4095U;

// 由频率计算 toggle_div = f_adc / (2f)

uint32_t td = ADC_TRIG_FREQ_HZ / (2U * f);

// 限幅保护

if (td < TOGGLE_DIV_MIN) td = TOGGLE_DIV_MIN;

if (td > TOGGLE_DIV_MAX) td = TOGGLE_DIV_MAX;

toggle_div = (uint16_t)td;

}

// 3) 动态分频翻转 DAC:固定幅值、频率可变方波

if (++div_cnt >= toggle_div)

{

div_cnt = 0;

hi ^= 1;

uint16_t out = hi ? DAC_MAX_VALUE : 0;

HAL_DAC_SetValue(&hdac1, DAC_CHANNEL_1, DAC_ALIGN_12B_R, out);

}

}(3)ADC 注入回调与实验一相同。

- 实验现象与结果分析

实验运行后,用示波器测量 ADC 采样 I_U 波形(蓝色曲线)和 DAC 输出 PA4 引脚波形(黄色曲线)。如下图所示,当缓慢调节电位器使输入电压 I_U 缓慢增大时,DAC 输出方波的频率随之平滑增大,且变化过程与输入电压保持良好的对应关系。

在本实验中,通过对 IU 通道采样值进行低通滤波,并将其线性映射到 10~100 Hz 的频率区间,在 ADC 注入采样完成回调中动态调节 DAC 输出节拍,实现了基于采样值的频率调制输出。该结果验证了在保持 PWM 同步采样与回调驱动结构不变的前提下,采样数据不仅能够参与控制量的幅值调制,也能够稳定地驱动输出节拍和相位推进。

6. 小结

本文在前文 PWM 触发 ADC 同步采样验证的基础上,引入 DAC 作为可视化输出手段,围绕"采样完成后控制量如何产生并输出"这一核心问题,设计并完成了三个循序渐进的实验。通过严格保持与标准 FOC 电流环一致的闭环时序结构------即以 PWM 周期为时间基准,在 ADC 注入采样完成中断中推进后续输出逻辑------逐步验证了从同步采样到控制量生成的完整软件链路。

实验一通过在 ADC 注入回调中输出固定频率方波,验证了"同步采样---数据读取---波形输出"的基本流程;

实验二通过调节输入电压控制 DAC 输出方波的幅值随 IU 采样值连续变化,验证了采样数据参与控制量计算并实时作用于输出端的过程;

实验三通过调节输入电压控制 DAC 输出方波的频率随 IU 采样值的调制输出,验证了 DAC 输出节拍能够随输入电压平滑变化。

上述三个实验,通过 DAC 将原本"不可见"的控制量以直观的模拟波形形式呈现出来,从而有效验证同步采样后的控制逻辑与时序结构是否正确。本文所采用的"ADC 注入完成回调驱动输出"的软件架构,在结构和时序上与标准 FOC 电流环完全一致,为后续引入电流 PI 调节、相位累加以及 SVPWM 波形合成提供了可直接复用的基础框架。

版权声明:

youcans@qq 原创作品,转载必须标注原文链接:【STM32G4-FOC】(5)DAC 受控输出闭环链路:基于同步采样的幅值与频率调制(https://blog.csdn.net/youcans/article/details/157294022)

Copyright@youcans 2026

Crated:2026-1