目录

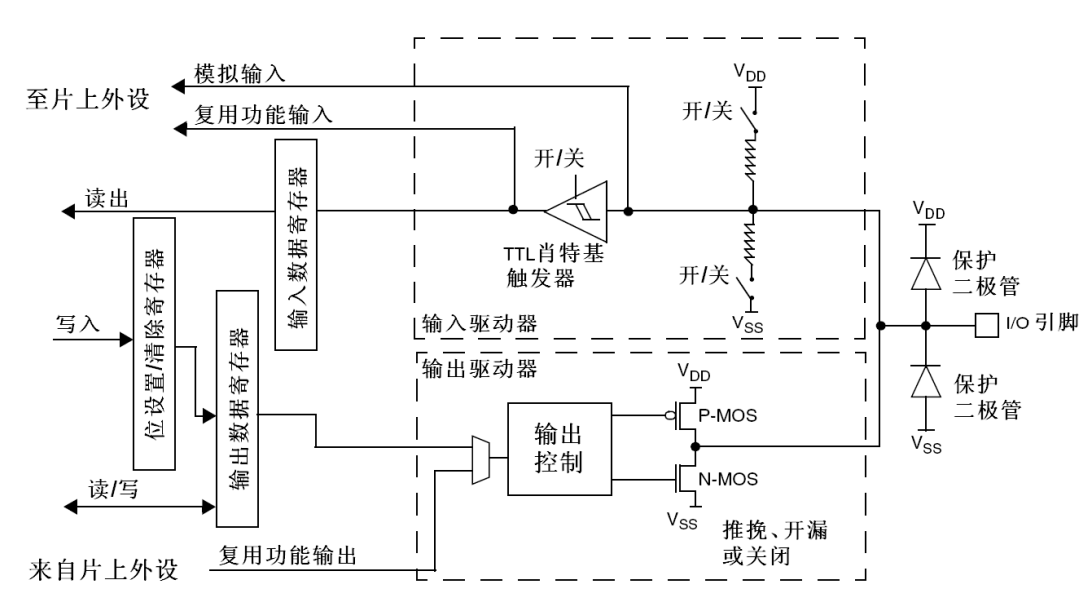

一、GPIO端口的基本结构

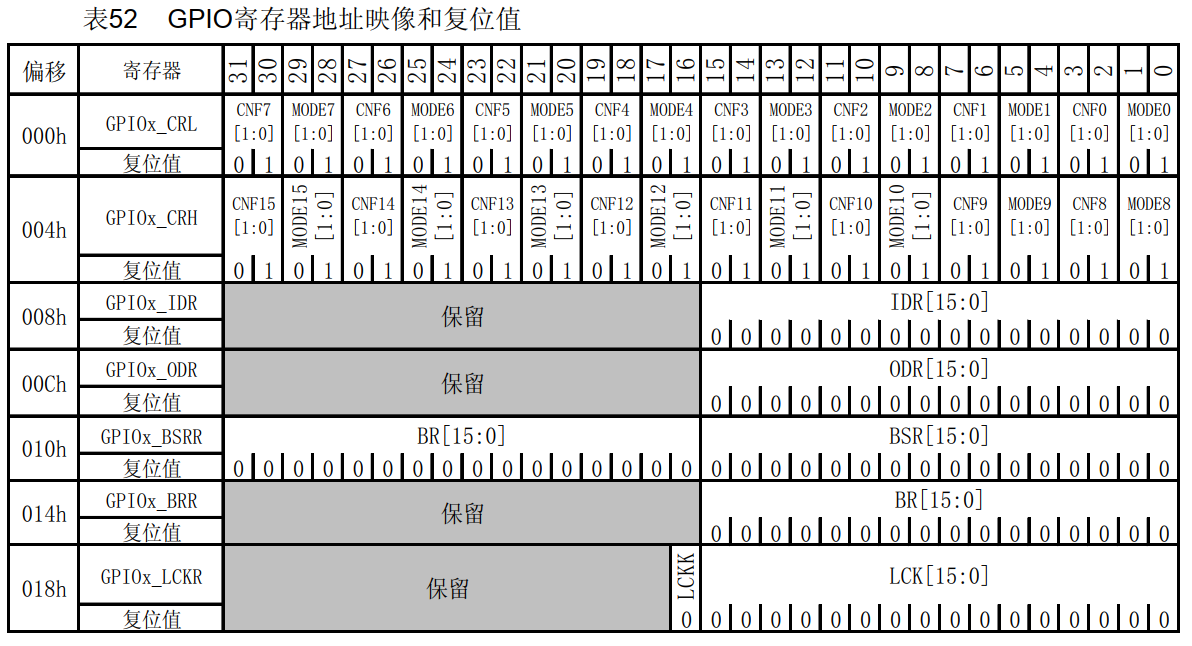

二、每组GPIO模块有7个相关的寄存器:

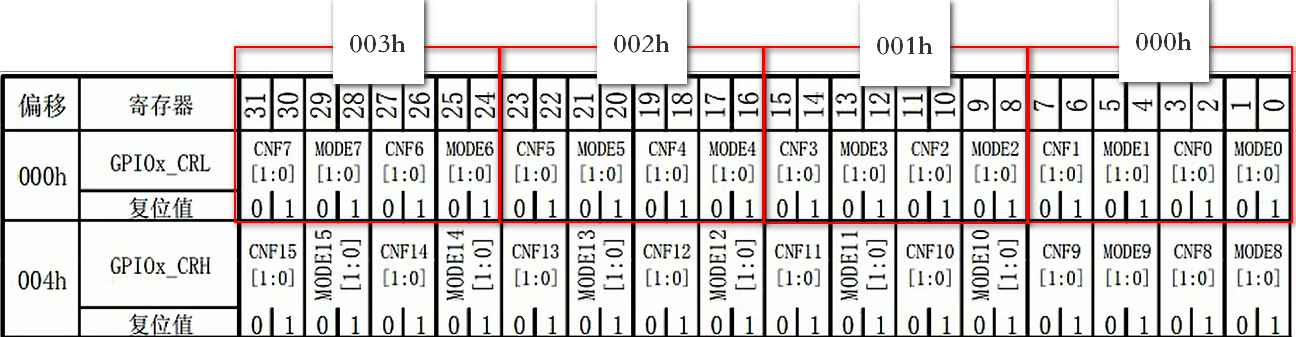

- 2个32位配置寄存器---GPIOx_CRL, GPIOx_CRH

- 2个32位数据寄存器---GPIOx_IDR,GPIOx_ODR

- 1个32位置位/复位寄存器---GPIOx_BSRR

- 1个16位复位寄存器---GPIOx_BRR

- 1个32位锁定寄存器---GPIOx_LCKR

这7个寄存器中最重要的是前2个寄存器:

2个32位配置寄存器GPIOx_CRL, GPIOx_CRH

2个32位数据寄存器GPIOx_IDR, GPIOx_ODR

剩下的:

1个32位置位/复位寄存器和1个16位复位寄存器使用的比较少,且功能类似。

最后的:

1个32位锁定寄存器GPIOx_LCKR用于保护配置和数据寄存器不被修改

1.说明:

- GPIOx中的x指的是每一组GPIO端口都有其对应的这些寄存器

- 每组GPIO对应的寄存器的地址是GPIO端口的基地址+寄存器的偏移

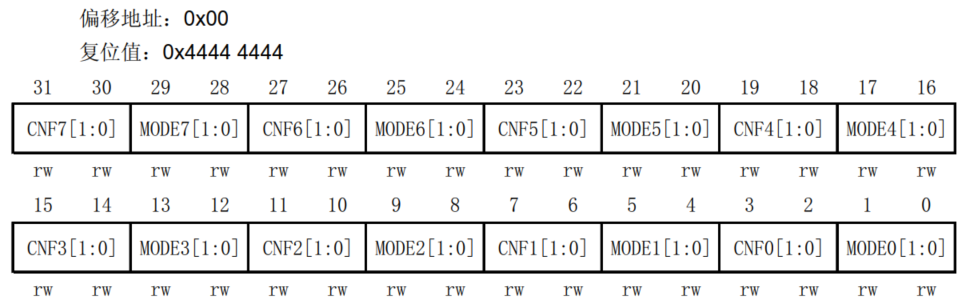

(一)2个32位配置寄存器

1.GPIOx_CRL 端口配置低寄存器

CRL:configeration register low

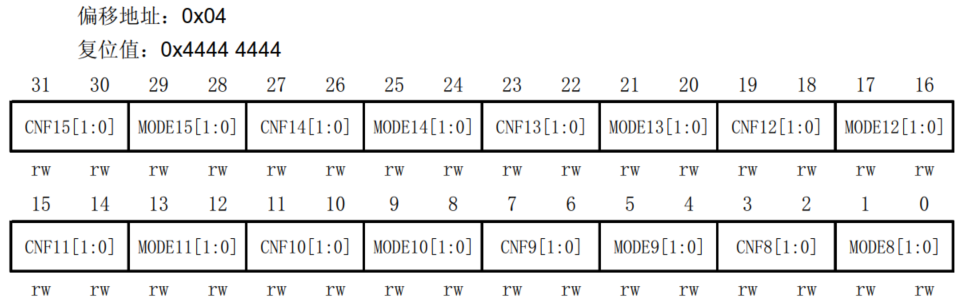

2.GPIOx_CRH端口配置高寄存器

CRL:configeration register high

CRL和CRH寄存器的作用:

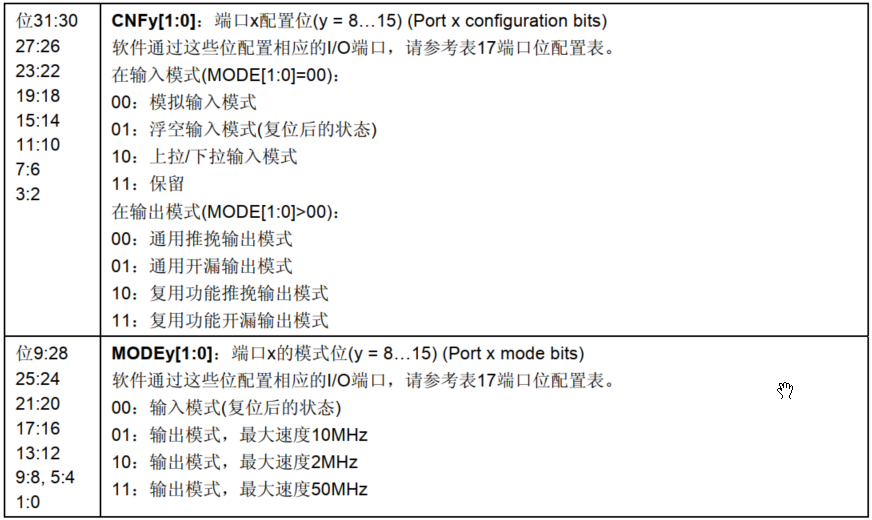

3.寄存器解读

GPIO的端口配置寄存器分为两个:

端口配置高寄存器CRH和端口配置低寄存器CRL

CRL控制第x组的0-7管脚

CRH控制第x组的8-15管脚

CRH寄存器和CRL寄存器总共使用了64bit,每4个比特控制一个管脚,这样一来,就会有一些位是保留状态。

注意:

(1)寄存器的复位值是0x4444 4444,这时寄存器内部的各位:01 00 也就意味着:GPIO接口的默认模式为:浮空输入模式

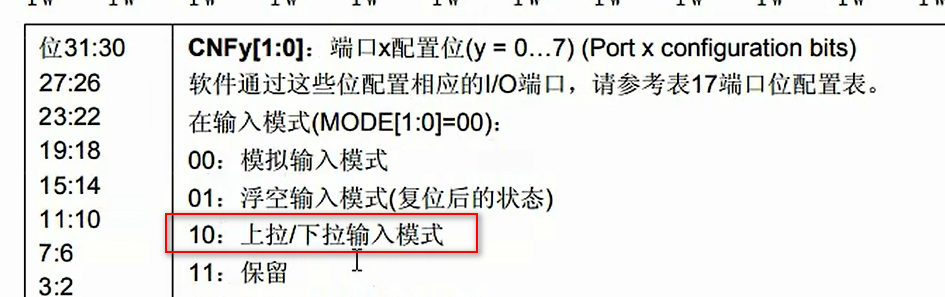

(2)这里的上下拉在一个控制位,配置时取端口的初始状态

(二)2个32位数据寄存器

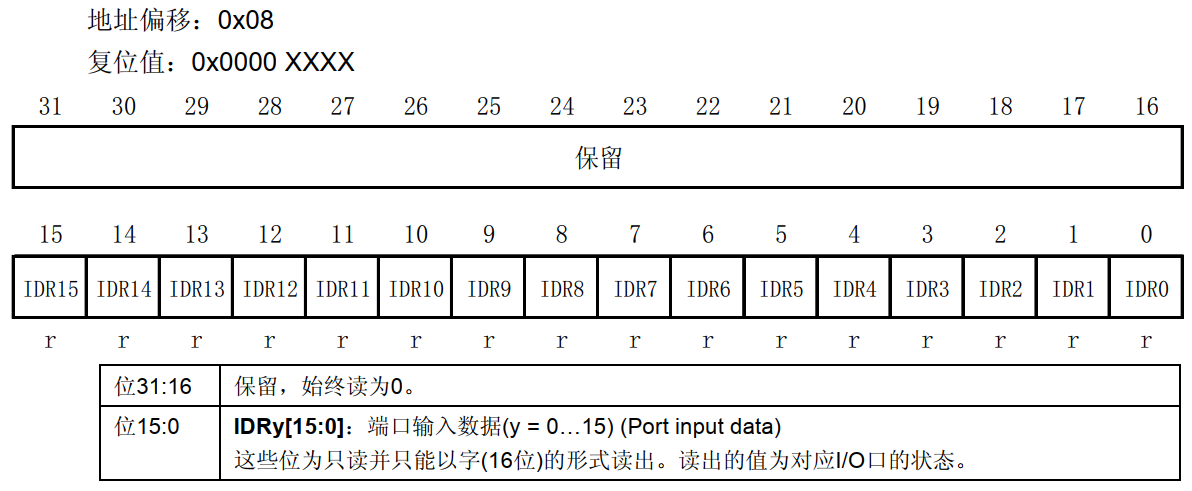

1.GPIOx_IDR端口数据输入寄存器

IDR:input data register

数据接收时,先通过IO口经过施密特触发器滤波,得到标准的高低电平后写入到IDR中,再由CPU读取寄存器的信息完成数据输入。

每一位对应一个端口的数据状态

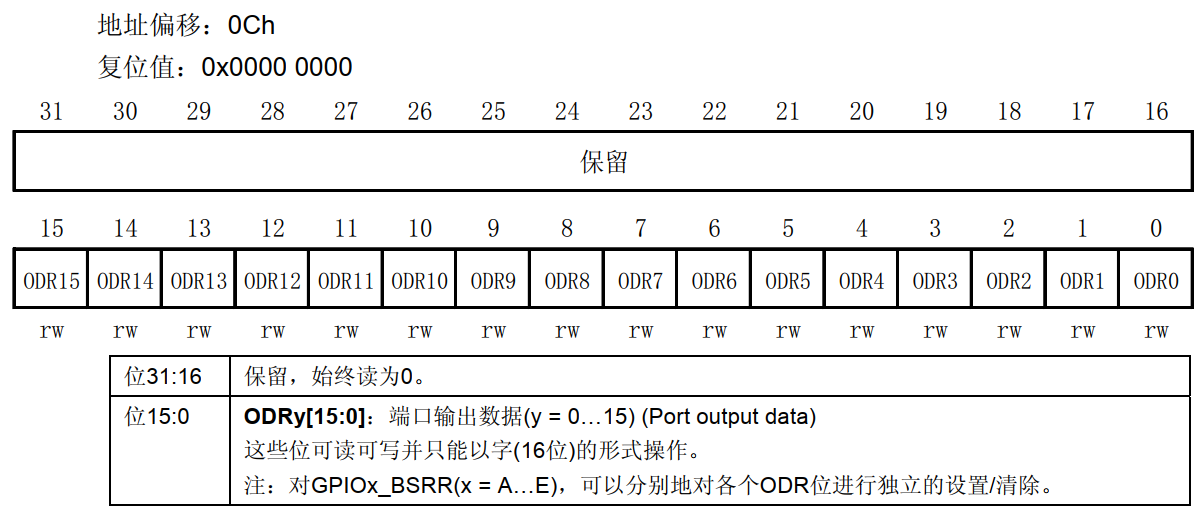

2.GPIOx_ODR端口数据输出寄存器

ODR:output data register

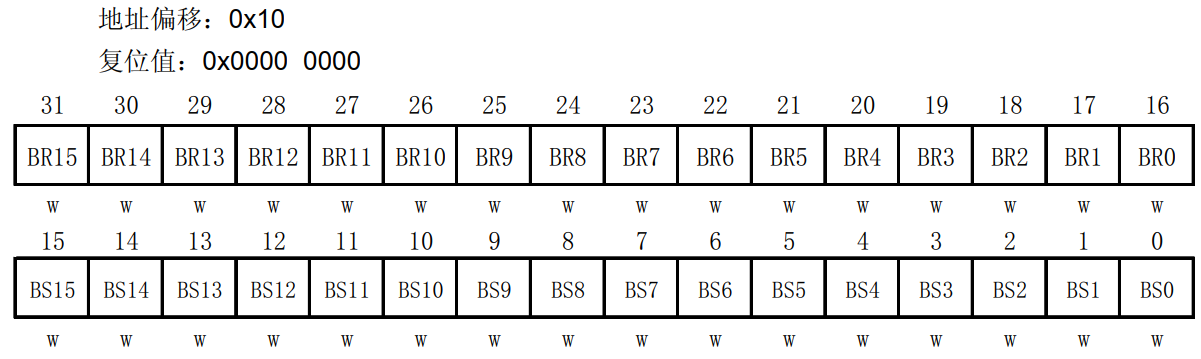

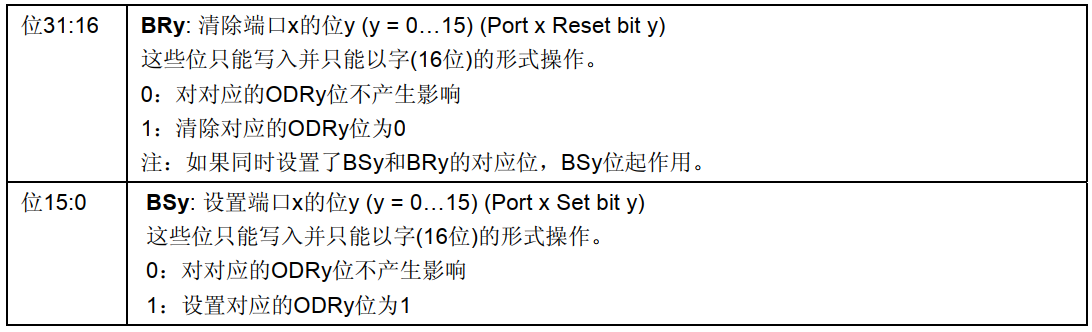

(三)1个32位置位/复位寄存器

GPIOx_BSRR:端口位设置/清除寄存器

BSRR:bit set/reset register

疑问:

我们可以直接操作ODR,为什么还要有这个BSRR寄存器呢?

答案:

这样设置可以简化编程,有了这个寄存器,在编程时就会省去置0时对右操作数的取反操作,也不会再有按位或的运算,会简化编程的逻辑。

注意:若对应的BR和BS同时为1,BS生效

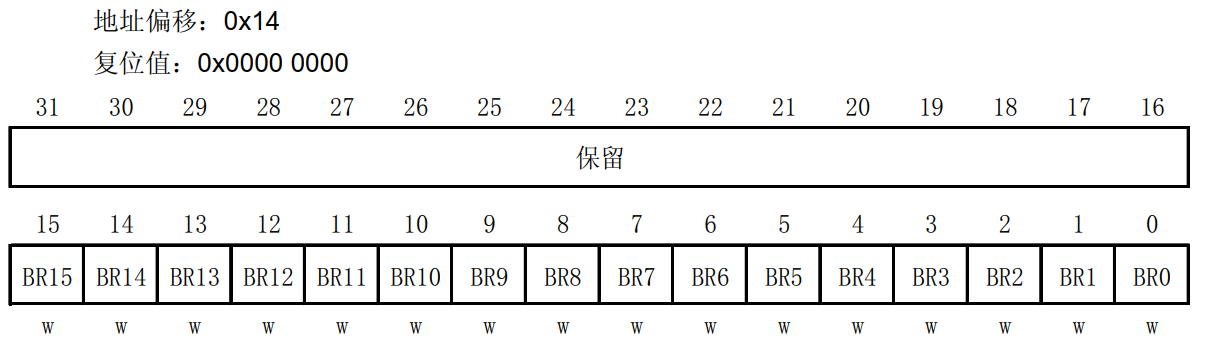

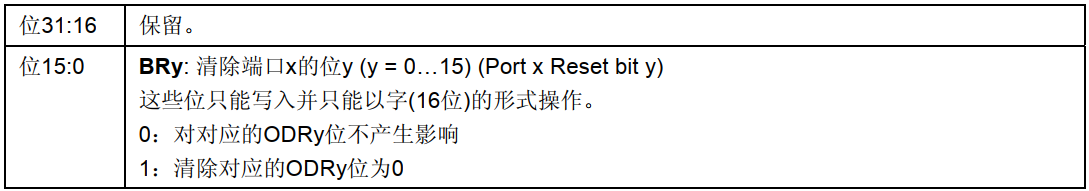

(四)1个16位复位寄存器

GPIOx_BRR:端口位清除寄存器

BRR:bit reset register

BRR对比BSRR功能少了set功能,reset功能一致。

在编程时,可以通过BSRR置位,可以通过BRR置零。

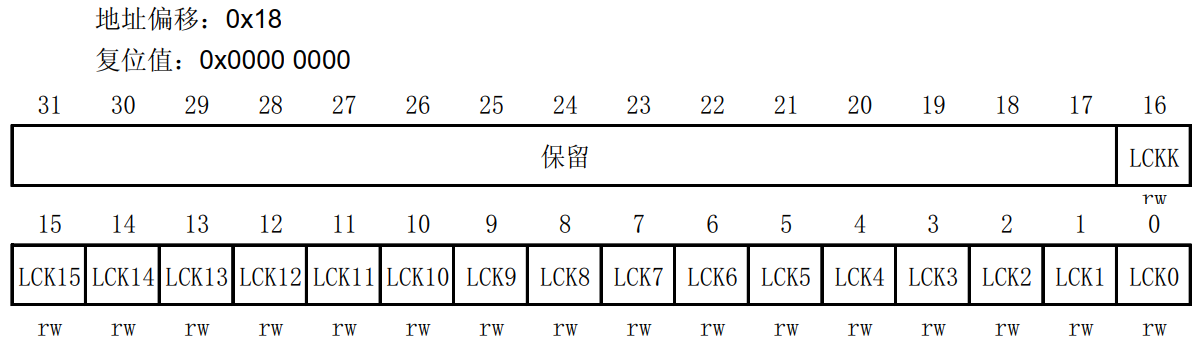

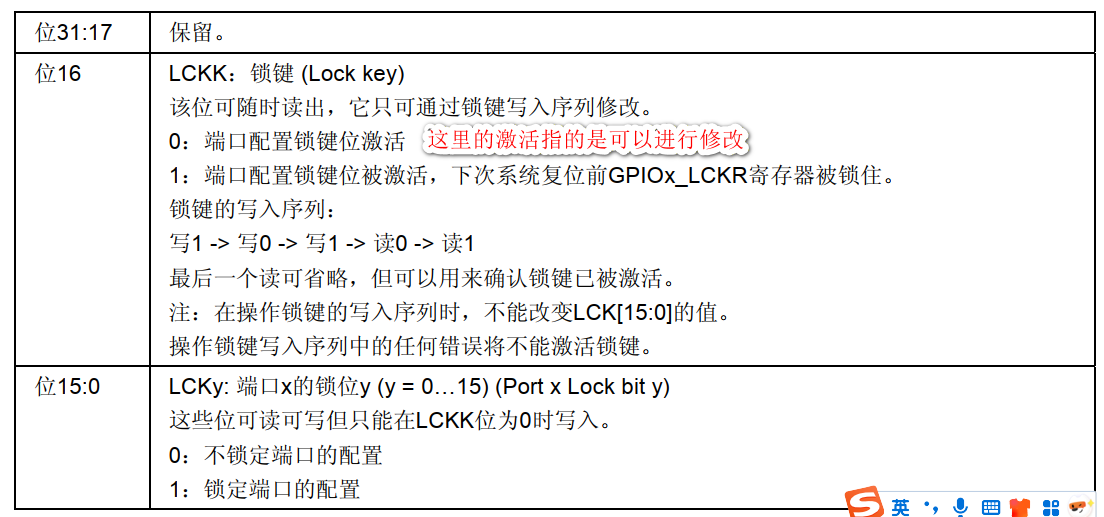

(五)1个32位锁定寄存器

GPIOx_LCKR

位16LCKK:锁键(lock key),锁定的是位15:0LCK锁定寄存器的锁定位,一旦锁定,需要复位后才能再次更改。

位16的LCKK的值的改变需要经过一个写入序列: **先写1->再写0->再写1->读0;**经过这个操作后,LCKK就会变为1,我们可以再次将其中的值读出,确认LCKK被激活。

位15:0LCK锁定寄存器的每一锁定位针对的是CRH和CRL的4个位的锁定

(六)GPIO寄存器地址映像

1.结构体类型定义:

typedef struct { __IO uint32_t CRL; __IO uint32_t CRH; __IO uint32_t IDR; __IO uint32_t ODR; __IO uint32_t BSRR; __IO uint32_t BRR; __IO uint32_t LCKR; } GPIO_TypeDef;

2.关于偏移量是4的理解:

内存中,以每8个bit为一个基本存储单元:字节,每个字节都会有一个编号---内存地址,这个内存地址使用十六位数进行标识

连续的内存空间的地址编号是连续的

如下图: