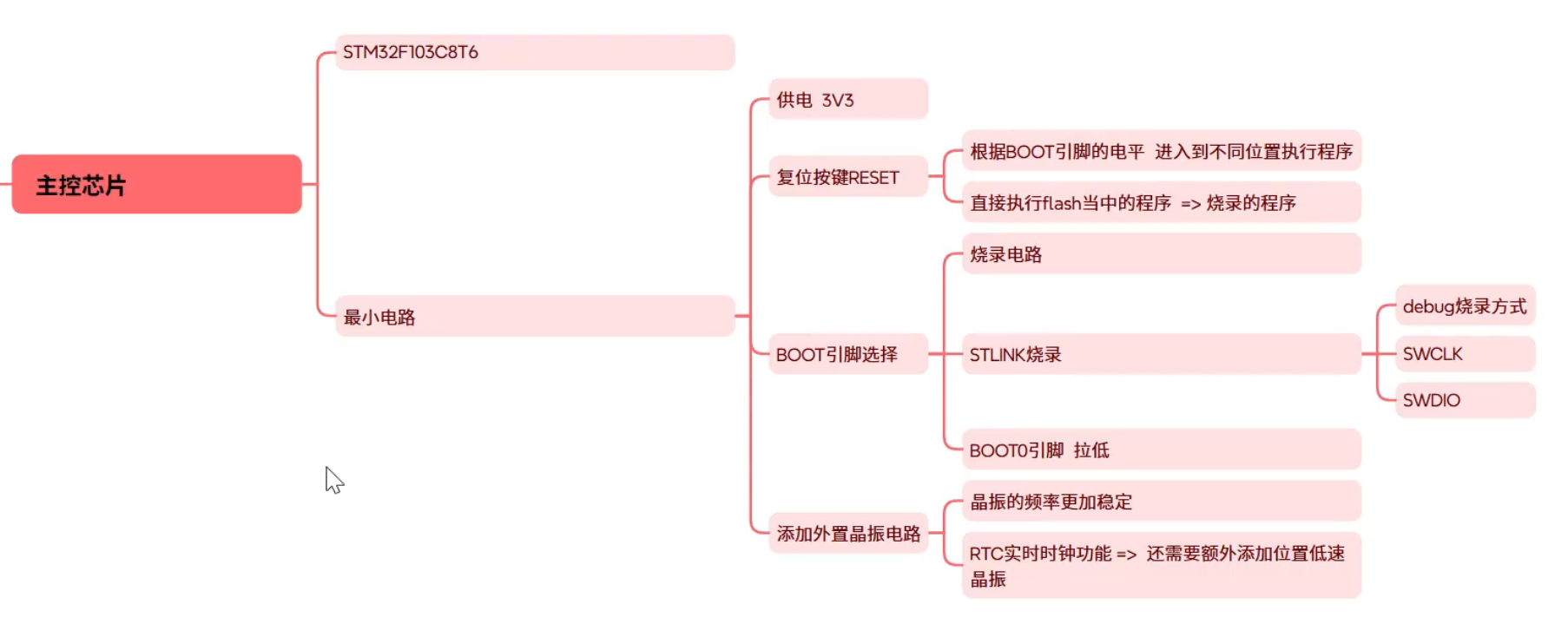

ALT+TAB可以快速切换页面方便对板

如果你对下面描述的部分有异或,比如不确定RTC是什么?BOOT引脚对烧录的方式有什么影响?都可以在《参考资料》中ctrl+F快速搜索,免得你去百度了~

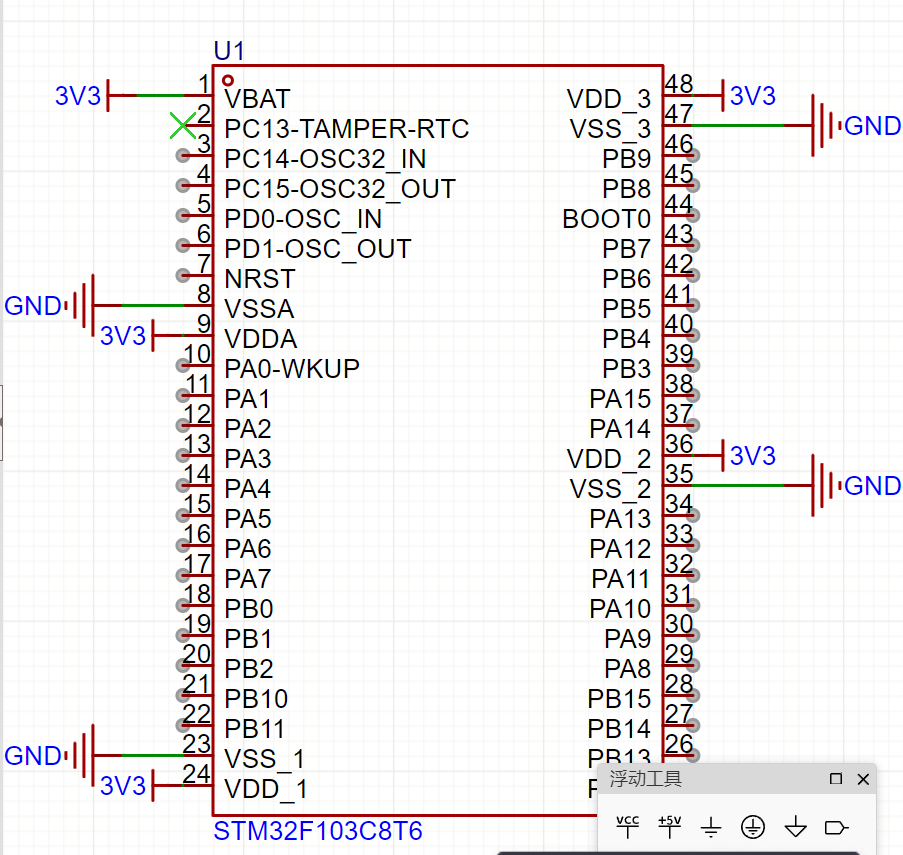

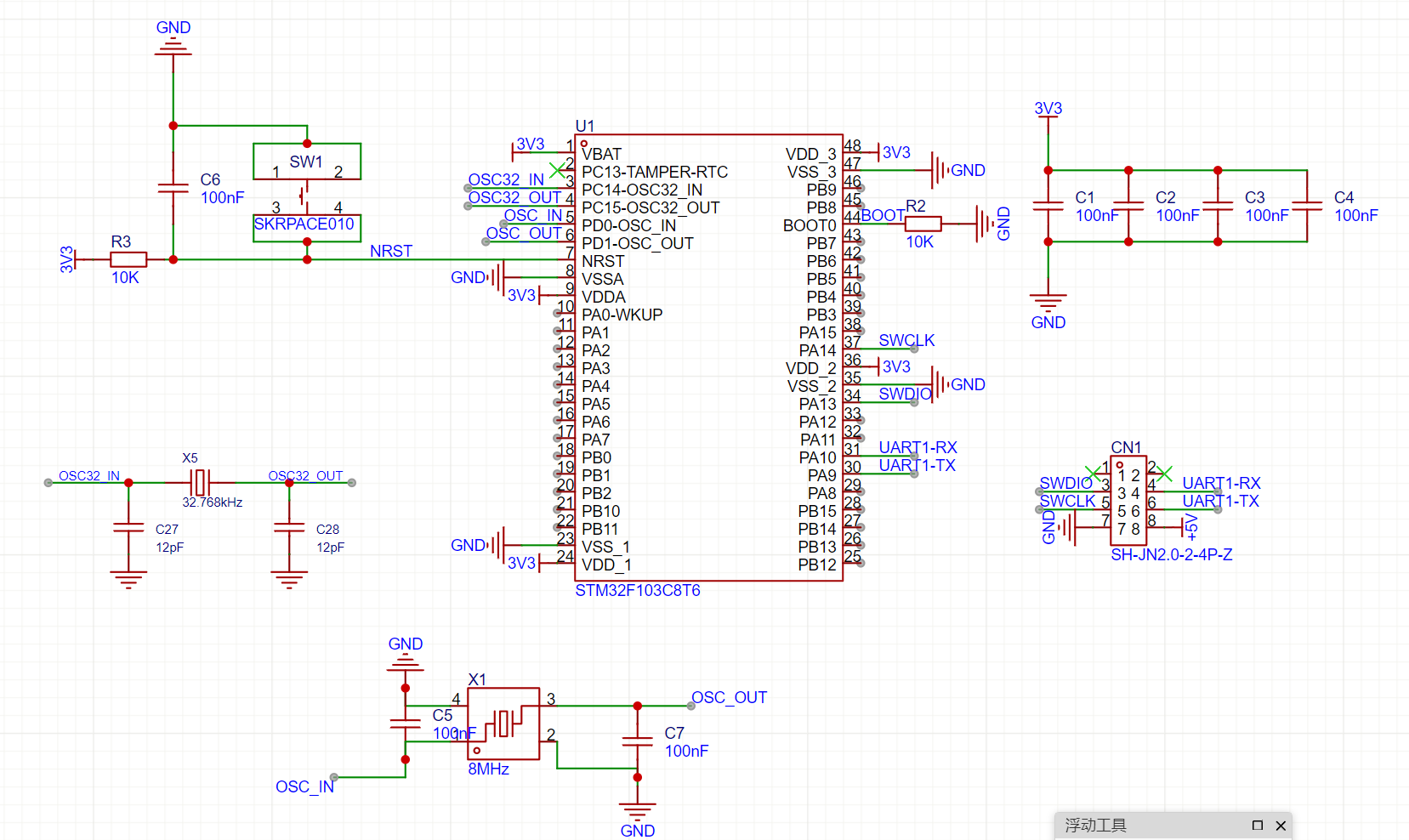

电源模块

首先画电源模块,找到主控的VSS VDD以及VBAT,接入GND和3V3,这个VBAT是给备用区供电的,备用区用于掉电后仍然运行的程序,比如外部RTC(Real-Time-Clock)电路,用于解决时间戳不一致的问题(没有 RTC 的设备,每次上电时间都会回到 1970-01-01(Unix 时间起点),导致日志乱序、定时任务失效、摄像头时间戳错误等问题 。)。

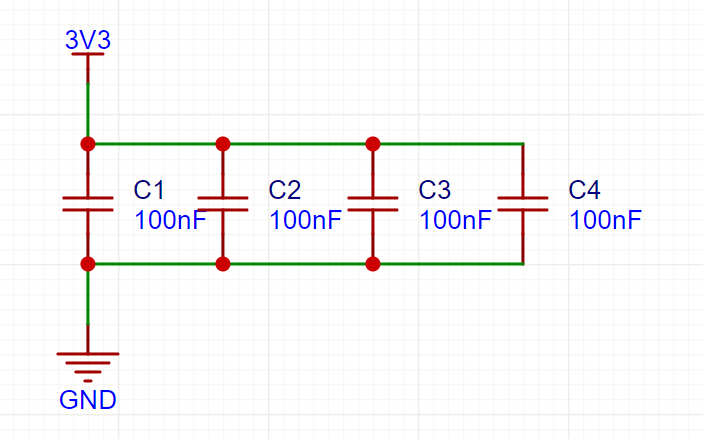

然后在电源上加一个小的滤波电容,因为DCDC输出的3V3并不稳定,有可能导致掉电重启,因此需要小电容来储能,在掉电的时候为其补充到3V3。

这几颗电容和stm32主控是并联的关系,找到他们共同的网络标签就知道了

复位电路模块

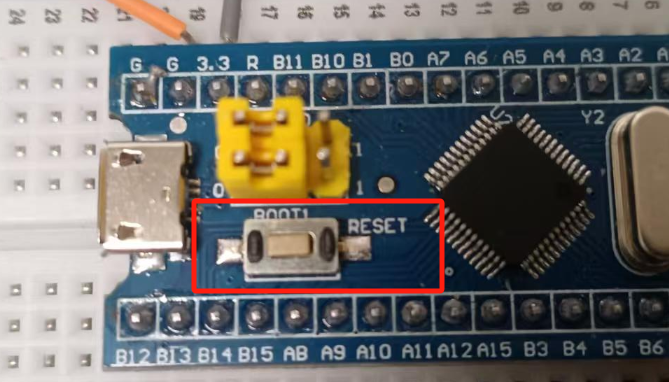

复位电路有个按钮,按下后就会重启单片机,进入某个内存块中开始执行程序,但是具体会从哪个内存块读取,取决于BOOT引脚。具体来说有三种配置方式,我们默认BOOT0 = 0 → 从 主 Flash 启动,其他方式参考《参考资料》。

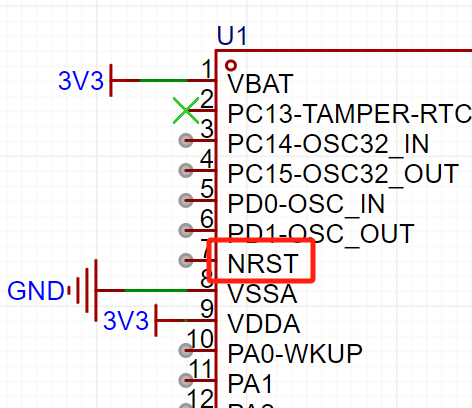

接收这个复位信号的引脚是NRST,N代表低电平有效,RST是reset的简写。

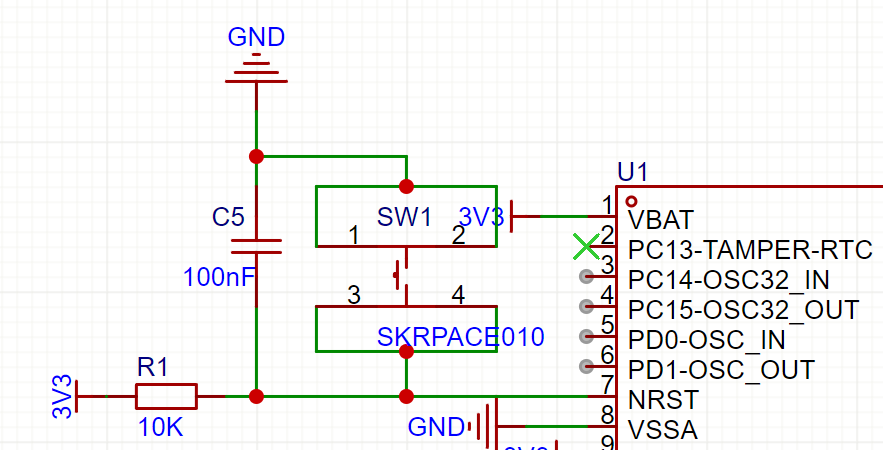

因此,按下按钮应该使其切换一瞬间低电平,一般运行时应处于高电平,因此需要加一个上拉电阻。

按下SW1后3V3与GND联通,NRST处的电压和R1下端电压,也就是GND电压一致,为LOW。

弹起后NRST处电压和C5下端电压一致,为3V3,为HIGH。

BOOT烧录电路模块

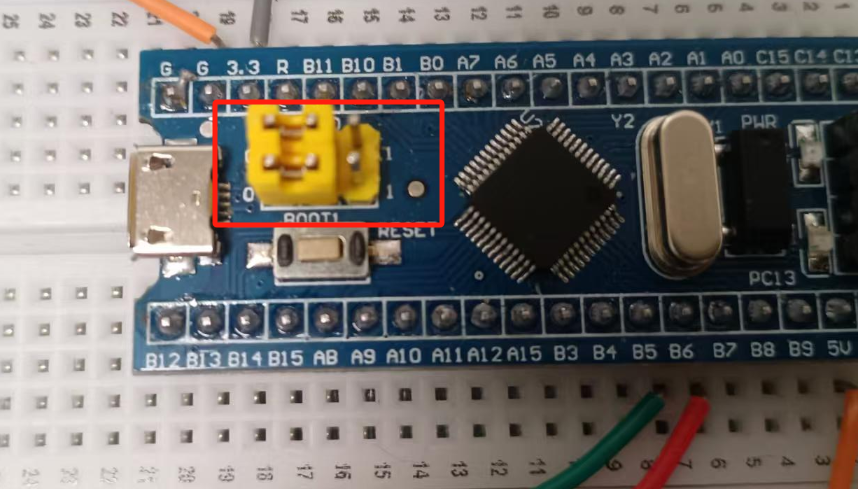

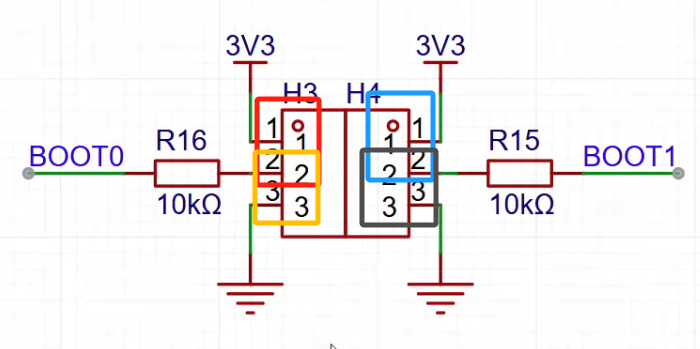

烧录模式的切换通过引脚帽开关实现。

通过切换两个引脚帽的位置(红黄、蓝灰),有四种烧录方式。

我们只需要从主Flash开始读取程序,因此只需要BOOT=0的烧录方式,也就是把BOOT0置低电平。这样即可:

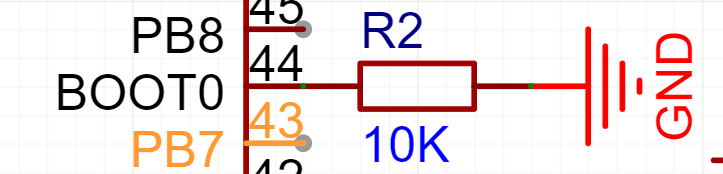

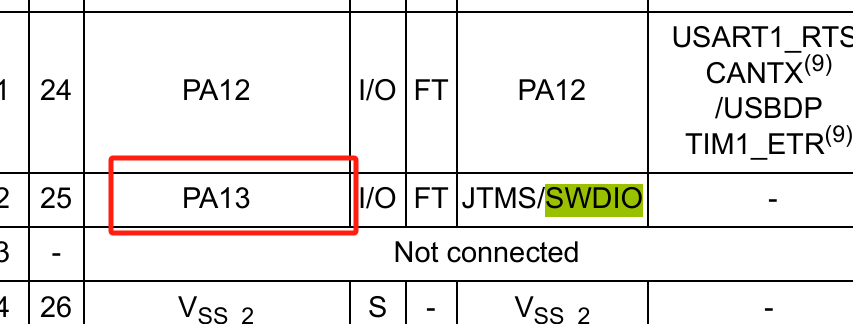

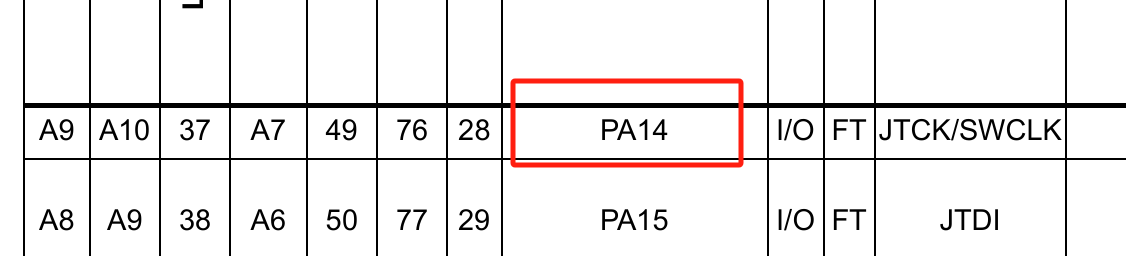

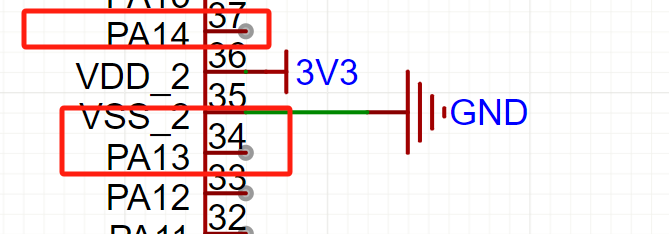

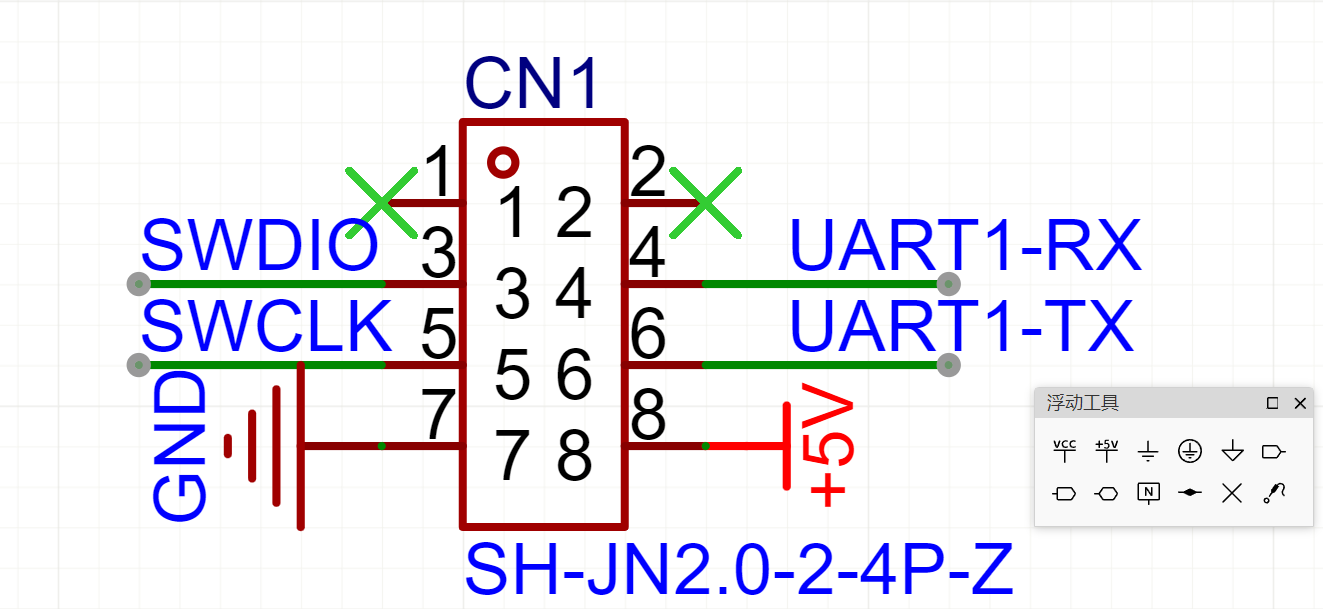

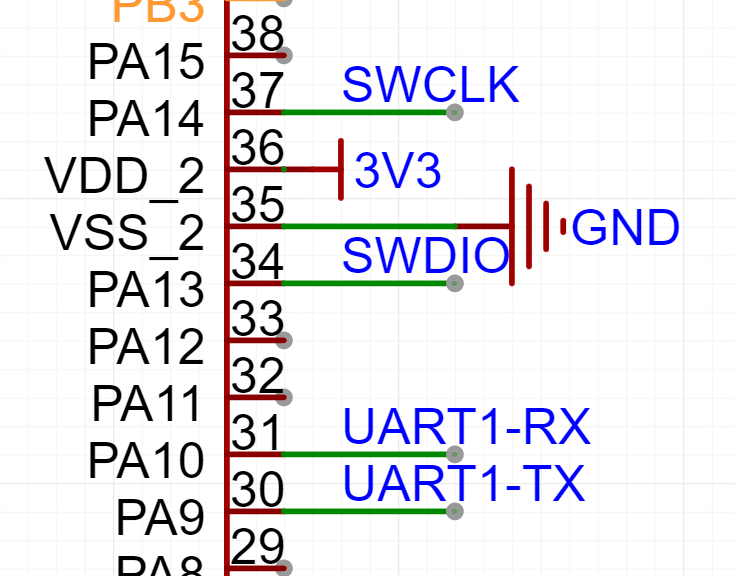

烧录的时候需要SWCLK SWDIO两个引脚,因此去手册找这两个引脚对应的芯片内引脚

是PA13 PA14

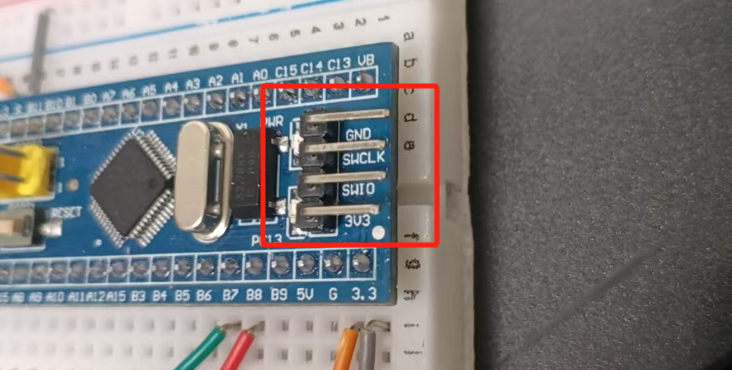

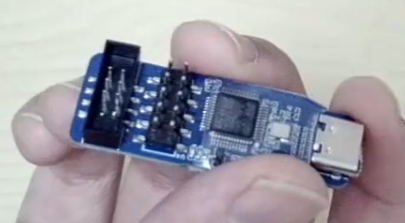

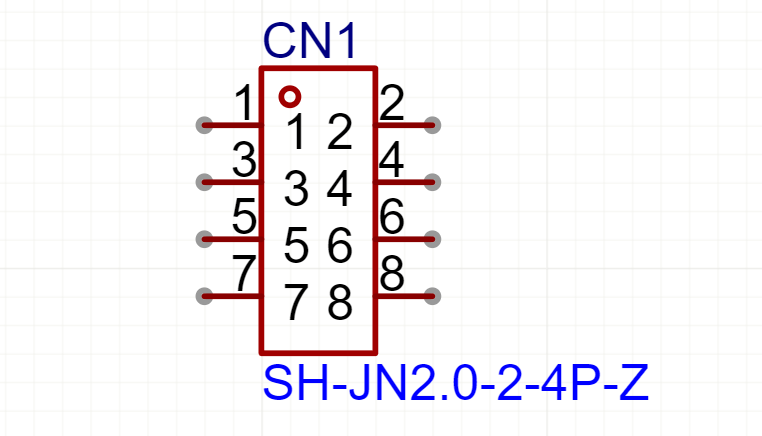

这两个引脚要和烧录器连接,可以直接使用排针,也可以使用简牛插口,就是这个东西:

在烧录器和这块板子上都会有这种接口,这样就不需要每次自己对应着插排针了。

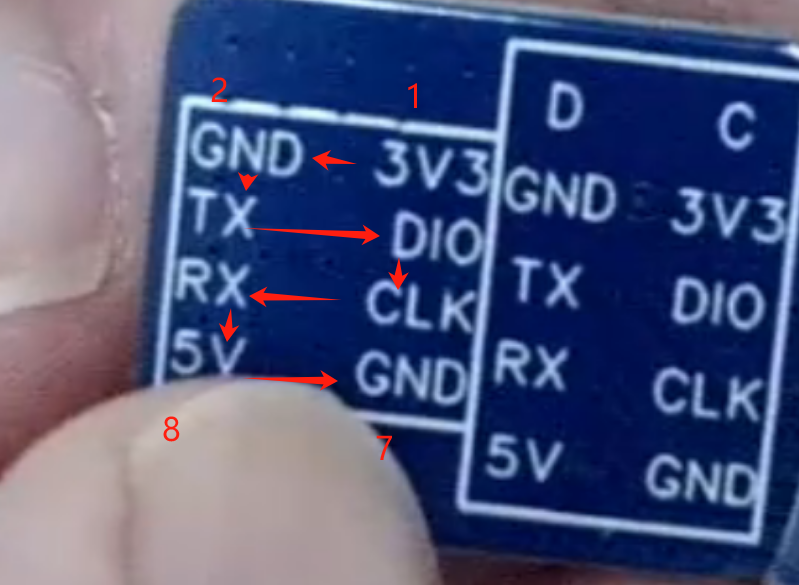

首先查看烧录器端的引脚定义。注意,我们看的是背面,因此正面来看右侧是1号引脚,顺序如上图。

DIO CLK支持SWD烧录,RXTX支持UART ISP烧录方式(虽然在这个项目只需要SWD,如果要UART ISP烧录,则需要将BOOT0置为高电平)

我们采用5V供电,因此3V3可以叉掉。

虽然虽然在这个项目只需要SWD,但我们保留USART ISP接口。

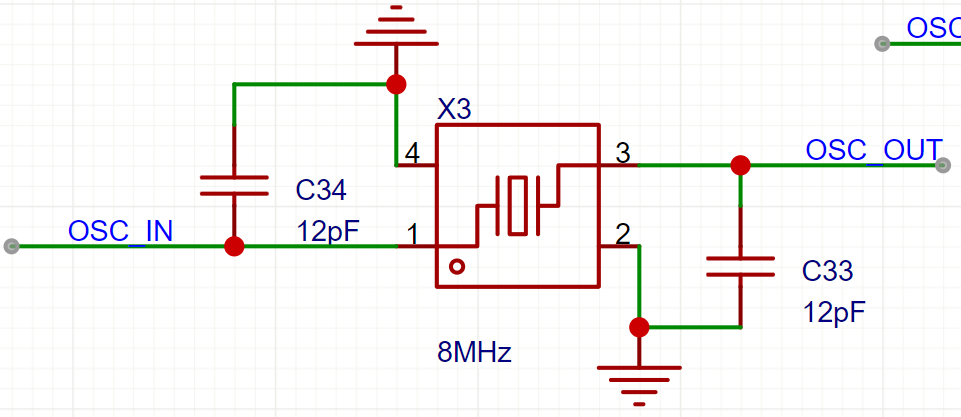

外部晶振电路模块

内部晶振会受到温度影响,因此不准,需要加外部晶振。

32k晶振是低速晶振,我们需要的是一个能替代内晶振的晶振,要用8MHz

这是高速晶振的电路图:

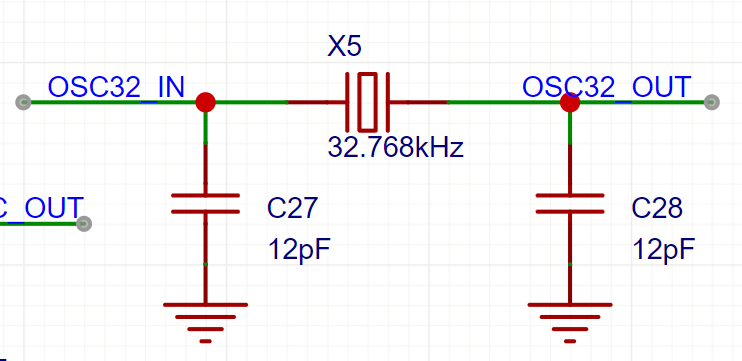

这是低俗晶振的电路图:

都是固定的,记住就好,注意这个电容,选型号的时候会告诉你,比如这款3225,就要用12pF的电容。

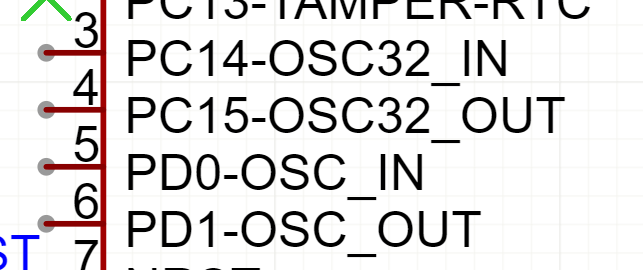

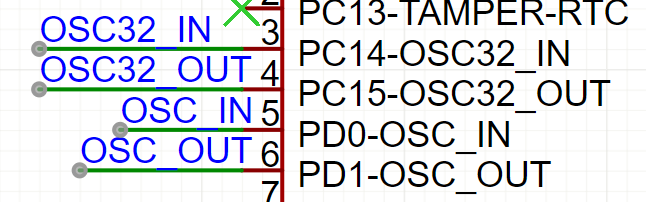

然后我们看主控上的引脚:

可以看到两组引脚,分别对应外部高低速晶振:

| 引脚名称 | 全称 | 对应时钟源 | 典型频率 | 主要用途 |

|---|---|---|---|---|

| OSC_IN / OSC_OUT | 外部高速振荡器输入/输出 | HSE(High-Speed External) | 4~26 MHz(常见 8MHz) | 提供系统主时钟,经 PLL 倍频后驱动 CPU、总线、外设 |

| OSC32_IN / OSC32_OUT | 外部低速振荡器输入/输出 | LSE(Low-Speed External) | 32.768 kHz | 驱动 RTC(实时时钟) 和 低功耗模式下的唤醒定时器 |

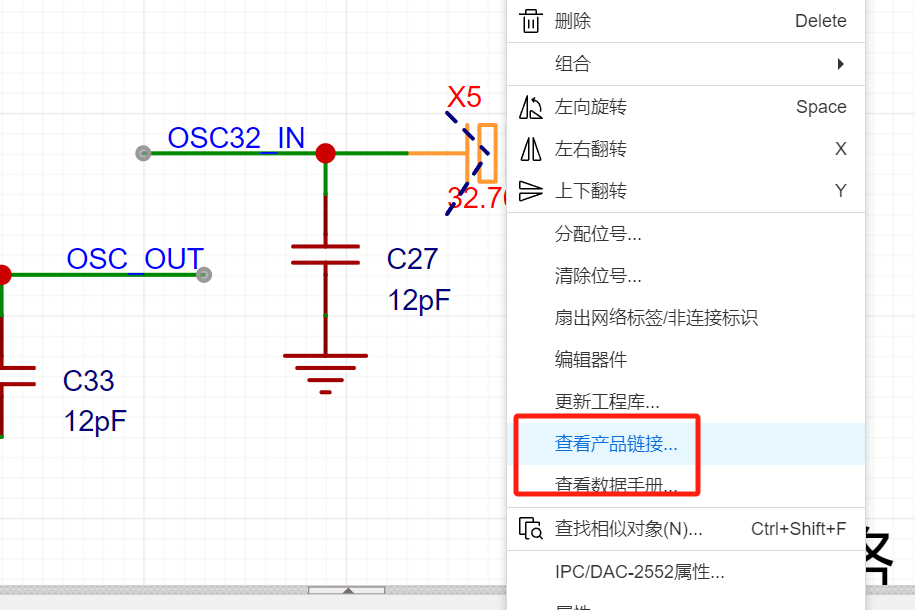

如果不知道用那个型号,可以在实力电路找到对应元件,右键,找查看产品链接即可。

为什么晶振要接电容到地?

根本原因 :晶振是一个被动谐振元件 ,必须依靠外部电容构成完整的 LC 谐振回路,才能:

- 满足振荡起振条件(相位 + 增益)

- 匹配负载电容,确保频率精准

- 抑制噪声和 EMI,提高稳定性

- 提供可靠的直流偏置参考

整体

以上就是如何绘制stm32的最小电路的流程。

参考资料

Cortex-M 是什么?

它不是某个具体的品牌或产品,而是 ARM 公司设计的一种"CPU 蓝图" 。

就像发动机的设计图一样,ARM 把这个"低功耗、反应快、省电又便宜"的 CPU 设计好,然后授权给 ST(意法半导体)、NXP、兆易创新等公司,让他们做成各种微控制器(MCU)卖出去。

Cortex-M 有什么用?

让小设备变聪明,而且不费电、不贵、反应快。

DSP(数字信号处理器)

是一种专门用来"快速处理声音、图像、传感器信号等实时数据"的专用芯片。

假设你戴着一副 主动降噪耳机,外面很吵(比如地铁轰隆声),但你听到的却是安静的音乐。

这个神奇效果是怎么来的?

→ 耳机里的麦克风先"听"到噪音,

→ 然后 DSP 芯片立刻计算出一个"反向声波" ,

→ 再把反向声波和原音乐混合,

→ 噪音就被抵消了!

整个过程必须在 几毫秒内完成 ,否则你就听出延迟了。

这种"高速+大量数学运算"的任务,普通 CPU 或单片机搞不定,但 DSP 就是干这个的!

🔧 DSP 的核心特点(简单说):

-

专精数学运算

特别擅长做 乘法 + 加法 (比如

a×b + c),这是处理声音、图像的基础操作。普通芯片要好几个步骤,DSP 一个时钟周期就搞定。

-

哈佛架构

程序和数据分开存、分开读,就像两条高速公路并行,不堵车,速度更快。

-

流水线工作

像工厂流水线:取指令、解码、运算同时进行,效率翻倍。

-

有专用指令

比如"快速傅里叶变换(FFT)"------把声音从"时间域"转成"频率域"(比如识别你是男声还是女声),DSP 一条指令就能加速完成。

-

实时性强

数据来了马上处理,绝不拖延,适合雷达、电机控制、语音通话等对时间敏感的场景。

为什么很多音频处理要通过FFT转换到频率域处理?

在"时间域"里,声音是一团乱麻;而在"频率域"里,它被拆成了清晰的"音高成分",处理起来就像调音台一样简单直接。

什么是RTC 为什么实现RTC还需要添加外部低速晶振而不是高速晶振

RTC = Real-Time Clock(实时时钟)

你可以把它理解成设备里的 "电子表" ------即使主芯片断电、关机,它依然能靠一颗小纽扣电池(比如 CR2032)继续走时,记住当前的 年、月、日、时、分、秒、星期。

📌 没有 RTC 的设备,每次上电时间都会回到

1970-01-01(Unix 时间起点),导致日志乱序、定时任务失效、摄像头时间戳错误等问题 。

✅ 二、为什么 RTC 需要晶振?而且必须是 低速 的(32.768 kHz)?

🔧 核心原因:为了精准地"每秒走一步"

RTC 的本质是一个计数器:它靠一个稳定的时钟信号不断计数,数到一定值就认为"过了一秒"。

而 32.768 kHz 这个数字不是随便选的 ------它等于 2¹⁵(32768)!

这意味着:

- 晶振每秒振动 32768 次

- 只需一个 15 级二分频电路(就是连续除以 2,15 次)

- 就能得到 1 Hz 的精确秒脉冲(32768 ÷ 2¹⁵ = 1)

✅ 优势:

- 电路简单(只需计数器,无需复杂 PLL)

- 功耗极低(微安级,适合电池供电)

- 成本低、稳定性好'

备份域

| 问题 | 答案 |

|---|---|

| 什么是备份域? | MCU 中由 VBAT 供电的"保险柜",用于在掉电/复位时保存 RTC 时间和关键数据。 |

| 为什么不直接用 1Hz 晶振? | 物理上不可行 (太大太贵)、抗干扰差 、无法支持高精度时间,而 32.768kHz 是经过验证的最优解。 |

BOOT引脚的选择对烧录方式有什么影响

一、核心机制:BOOT 引脚决定"启动入口"

以 STM32 为例(其他如 ESP32、NXP i.MX 类似):

- BOOT0 = 0 → 从 主 Flash 启动(运行用户程序)✅ 正常工作模式

- BOOT0 = 1, BOOT1 = 0 → 从 系统存储器(System Memory) 启动 → 运行 ST 出厂预置的 Bootloader ✅ 串口/USB 烧录模式

- BOOT0 = 1, BOOT1 = 1 → 从 SRAM 启动(调试用)

🔑 关键点:只有进入 Bootloader 模式,才能通过 UART、USB 等接口接收新固件。

二、对不同烧录方式的影响

1️⃣ SWD/JTAG 烧录(如 ST-Link、J-Link)→ ❌ 不受 BOOT 引脚影响

- 原理 :调试器通过 SWD 接口直接访问芯片内核和 Flash 控制器,绕过 CPU 启动流程。

- 即使 BOOT0=0(从 Flash 启动),只要芯片未被写保护,ST-Link 仍可擦除/烧录。

- 无需切换 BOOT 引脚,开发最方便。

📌 结论:使用 ST-Link/DAP-Link 烧录时,BOOT 引脚保持默认(BOOT0=0)即可 。

2️⃣ UART/USB 串口烧录(Bootloader 模式)→ ✅ 必须正确设置 BOOT 引脚

- 前提 :芯片必须从系统存储器启动,才能运行内置 Bootloader。

- 操作要求 :

- 烧录前:BOOT0 = 1, BOOT1 = 0

- 按复位(或上电),使芯片采样到该状态

- 通过串口发送固件(如使用 STM32CubeProgrammer)

- 烧录完成后:必须将 BOOT0 改回 0,否则下次上电仍进 Bootloader,不运行用户程序!

⚠️ 常见错误:烧完忘记改 BOOT0,设备"变砖"(其实只是没跑用户代码)。

3️⃣ U 盘拖拽烧录(DAP-Link 的 MSD 模式)→ ❌ 不依赖 BOOT 引脚

- DAP-Link 内部模拟 U 盘,实际仍是通过 SWD 协议烧录。

- 和 ST-Link 一样,直接操作 Flash,不经过 CPU 启动流程。

- BOOT 引脚状态无关紧要。

4️⃣ OTA / 应用层更新 → ❌ 完全不需要动 BOOT 引脚

- 用户程序自己实现升级逻辑(如接收新固件写入 Flash 某区域)。

- 启动时由用户代码跳转,BOOT 引脚始终为 0。

- BOOT 引脚只在出厂首次烧录或救砖时才需要干预。

1️⃣ 主 Flash(Main Flash / User Flash)------ 你的"程序仓库"

- 是什么 :芯片内置的 非易失性存储器(断电不丢数据),容量从几 KB 到几 MB 不等。

- 存什么 :你写的 用户程序(.bin/.hex 文件)、常量数据、配置参数等。

- 特点 :

- 只能按 页(Page)擦除(比如 2KB 一页),写入前必须先擦。

- 写入速度慢,但读取快。

- 掉电后内容永久保存(可擦写约 10 万次)。

- 类比 :就像电脑的 硬盘 ------ 存放操作系统和软件。

✅ 正常运行时,CPU 就是从这里加载并执行你的代码。

2️⃣ 系统存储器(System Memory)------ 出厂预装的"救火队长"

- 是什么 :芯片厂商(如 ST)在生产时固化在芯片内部的一段特殊 ROM 区域(通常 16--32KB)。

- 存什么 :官方 Bootloader 程序(不可修改!)。

- 作用 :当你的主 Flash 程序损坏、或首次烧录时,可通过它 从串口(UART)、USB 等接口接收新固件。

- 如何进入 :设置 BOOT0=1, BOOT1=0,上电复位 → 芯片从 System Memory 启动。

- 类比 :就像手机的 Recovery 模式 或 电脑 BIOS 的 PXE 网络启动 ------ 用于"救砖"或无调试器烧录。

⚠️ 注意:它不是 RAM,也不是普通 Flash,而是 掩膜 ROM(Mask ROM),出厂就写死,无法更改。

3️⃣ Bootloader ------ "启动脚本"(可以是多个角色)

这个词有两层含义,容易混淆:

🔹 A. 系统级 Bootloader(即 System Memory 里的那个)

- 厂商提供,固定功能:接收 UART/USB 数据 → 写入主 Flash。

- 用户不能改,只能"用"。

🔹 B. 用户自定义 Bootloader(放在主 Flash 开头)

- 你自己写的程序,放在主 Flash 起始位置。

- 功能更强大:比如支持 OTA 升级、加密校验、多应用切换等。

- 启动流程:

上电 → 主 Flash 的 Bootloader 运行 → 检查是否要升级 → 跳转到 App 区执行

✅ 很多智能设备(如路由器、IoT 终端)都采用这种"双区设计"。

📌 关键区别:

- System Memory 里的 Bootloader = 厂商给的"急救包"

- 主 Flash 里的 Bootloader = 你自己写的"智能管家"

4️⃣ SRAM(Static RAM)------ CPU 的"工作台"

- 是什么 :芯片内部的 高速易失性内存(断电清零)。

- 存什么 :

- 程序运行时的 变量、堆栈、函数调用记录

- 中断服务程序(ISR)的临时数据

- DMA 缓冲区(如串口接收缓存)

- 特点 :

- 读写速度极快(纳秒级),与 CPU 同频

- 容量小(几 KB 到几 MB)

- 掉电即丢失(所以不能存程序)

- 类比 :就像你办公桌上的 桌面 ------ 所有正在处理的文件都放这儿,关灯(断电)就收走了。

✅ 所有计算、逻辑判断、实时控制,都是在 SRAM 上完成的!

🔄 它们如何协作?------ 一个完整启动流程

-

上电 → 芯片采样 BOOT 引脚

-

情况 A:BOOT0=0

→ 从 主 Flash 启动

→ CPU 直接执行你的程序

→ 程序中的变量自动分配到 SRAM

→ 正常工作 ✅

-

情况 B:BOOT0=1, BOOT1=0

→ 从 系统存储器 启动

→ 运行 ST 官方 Bootloader

→ 等待 PC 通过串口发送新固件

→ 收到后写入 主 Flash

→ 烧录完成,需手动改回 BOOT0=0 才能运行新程序

-

(高级)用户 Bootloader 模式

→ 主 Flash 开头放自研 Bootloader

→ 它先运行,检查是否有新固件(比如从 SD 卡或网络下载)

→ 有则擦写 App 区,无则跳转到 App

→ 实现"无缝升级"

一、"APP区"是什么?

📌 简单说:

"APP区"就是主 Flash 中专门存放你写的"应用程序"的那一块内存区域。

它通常和 Bootloader 区 配对出现,构成一种常见的 双区固件架构。

🔧 为什么要有 APP 区?

想象你的智能手环需要升级固件:

- 如果直接覆盖整个 Flash,升级中途断电 → 设备变砖!

- 所以工程师把 Flash 分成两部分:

表格

| 区域 | 地址范围(示例) | 内容 | 特点 |

|---|---|---|---|

| Bootloader 区 | 0x08000000 ~ 0x08007FFF | 启动管理程序 | 小、稳定、不常更新 |

| APP 区 | 0x08008000 ~ 0x0807FFFF | 用户应用程序 | 大、经常 OTA 升级 |

🔄 工作流程:

- 上电 → CPU 先运行 Bootloader

- Bootloader 检查:

- 是否有新固件?

- APP 是否有效?(校验 CRC/签名)

- 如果一切正常 → 跳转到 APP 区地址,开始执行你的 main() 函数

- 如果需要升级 → 从网络/SD卡接收新固件 → 写入 APP 区 → 重启

💡 这样即使 APP 升级失败,Bootloader 还在,可以重新下载,永不掉砖!

二、为什么 STM32 开发板除了 4 针 SWD 烧录口,还有一个 USB 的"T字口"?

你看到的这个 USB Type-C 或 Micro-USB 接口(常标为 "USB USER" 或 "USB OTG") ,和烧录口是完全不同的功能!

🔌 它主要有三大用途:

1️⃣ 给开发板供电(Power Supply)

- 最基础的作用:插上 USB 线,5V 电源进来 → 板载 LDO 转成 3.3V → 给 STM32 供电。

- 不需要额外电源适配器,方便调试。

⚠️ 注意:这个 USB 不用于烧录(除非特殊设计),只是供电!

2️⃣ STM32 的 USB 功能测试(Device / Host / OTG)

- 模拟 U 盘、键盘、鼠标(USB Device)

- 读取 U 盘(USB Host)

- 实现手机与开发板互传数据(OTG)

✅ 举例:

📌 这个 USB 是 STM32 自己的功能引出,和烧录无关!

3️⃣ 某些开发板支持 USB DFU 烧录(但需配合 BOOT 引脚)

一、整体框架:STM32 的 4GB 地址空间(Cortex-M 架构)

STM32 基于 ARM Cortex-M 内核,是 32 位处理器,理论寻址空间为:

0x0000_0000 ~ 0xFFFF_FFFF(共 4GB)

但实际硬件资源远小于 4GB,ARM 预先将这 4GB 划分为 8 个 512MB 的 Block,STM32 在此基础上填充真实硬件:

表格

| 地址范围 | 名称 | 主要内容 |

|---|---|---|

| 0x0000_0000 -- 0x1FFF_FFFF | 代码区(Code) | Flash、System Memory、ITCM RAM(H7) |

| 0x2000_0000 -- 0x3FFF_FFFF | SRAM 区 | 主 SRAM、DTCM RAM、备份 SRAM |

| 0x4000_0000 -- 0x5FFF_FFFF | 外设寄存器区 | GPIO、UART、TIM、ADC 等控制寄存器 |

| 0x6000_0000 -- 0x9FFF_FFFF | 外部存储器区 | FMC/FSMC 控制的 PSRAM、NOR Flash、SDRAM |

| 0xE000_0000 -- 0xFFFFFFFF | 内核私有外设区 | NVIC、SysTick、MPU、调试组件 |

✅ 所有存储器(包括外设寄存器)都统一编址 ,CPU 用

LDR/STR指令就能访问它们。

🧱 二、内部存储器详解(芯片集成部分)

1️⃣ 主 Flash(Main Flash / User Flash)

- 地址 :

0x0800_0000开始(物理地址) - 类型:非易失性 NOR Flash

- 容量:64KB ~ 2MB(依型号而定,如 STM32F103C8T6 是 64KB)

- 用途 :

- 存放 用户程序(APP)

- 可划分出 Bootloader 区 + APP 区

- 剩余空间可模拟 EEPROM(存配置参数)

- 特点 :

- 掉电不丢失

- 写入前需按 页擦除(Page Erase)

- 支持 XIP(Execute In Place)------直接在 Flash 运行代码

🔍 APP 区 = 主 Flash 中从某个偏移地址开始的一段区域,由链接脚本定义。

2️⃣ 系统存储器(System Memory)

- 地址 :

0x1FFF_0000开始(不同系列略有差异) - 类型 :掩膜 ROM(Mask ROM) ------ 出厂固化,不可修改

- 内容 :ST 官方 Bootloader(支持 UART、USB DFU、CAN 等 ISP 协议)

- 用途:首次烧录、救砖、无调试器时更新固件

- 如何启用 :通过 BOOT0/BOOT1 引脚 选择启动源

⚠️ 注意:这不是 Flash,不能写!只是只读的"急救包"。

3️⃣ 选项字节(Option Bytes)

- 地址 :

0x1FFF_F800附近 - 类型:特殊 Flash 区域(可擦写,但次数有限)

- 用途 :配置芯片行为,如:

- 读保护(RDP)

- 写保护(WRP)

- BOOT0 引脚功能重映射

- 看门狗使能

- 特点:独立于主程序,烧录时可选择是否覆盖

4️⃣ SRAM(Static RAM)

-

地址 :

0x2000_0000开始(主 SRAM) -

类型:高速易失性静态 RAM

-

容量:几 KB ~ 1MB+(如 H7 有 1MB)

-

细分(以 STM32H7 为例):

- DTCM RAM(0x2000_0000):数据紧耦合内存,CPU 直连,零等待

- ITCM RAM(0x0000_0000):指令紧耦合内存,放关键代码(如中断服务程序)

- AXI SRAM(0x2400_0000):大容量通用 RAM

- 备份 SRAM(0x3880_0000):接 VBAT,掉电保持(需纽扣电池)

-

用途:

- 全局变量(

.data,.bss) - 栈(Stack)和堆(Heap)

- DMA 缓冲区

- RTOS 任务栈、TCB

- 全局变量(

✅ 所有运行时数据都在 SRAM!

5️⃣ 备份域(Backup Domain)

- 不是独立存储器 ,而是 SRAM 和 RTC 寄存器的一个逻辑区域

- 供电 :由 VBAT 引脚(纽扣电池)单独供电

- 包含 :

- RTC 寄存器(时间、闹钟)

- 备份 SRAM(4KB~32KB)

- 备份数据寄存器(BKP)

- 作用:系统复位/掉电后仍保留关键状态

🔌 三、外部扩展存储器(通过 FMC/FSMC 或 OCTOSPI)

6️⃣ PSRAM(Pseudo SRAM)

- 地址 :

0x6000_0000起(Bank1),通过 FMC 控制器映射 - 类型:伪静态 RAM(内部是 DRAM + 自刷新控制器,接口像 SRAM)

- 用途:当内部 SRAM 不够时,扩展图像帧缓存、音频缓冲、AI 模型权重

- 优点:比 SDRAM 接口简单,比 SRAM 成本低、容量大(常见 8~64MB)

💡 常用于 ESP32-S3、STM32H7 视觉项目。

7️⃣ 外部 NOR/NAND Flash、SDRAM

- 也通过 FMC/OCTOSPI 映射到

0x6000_0000~0x9FFF_FFFF - 用于存储大文件(如 UI 图片、语音提示、固件备份)