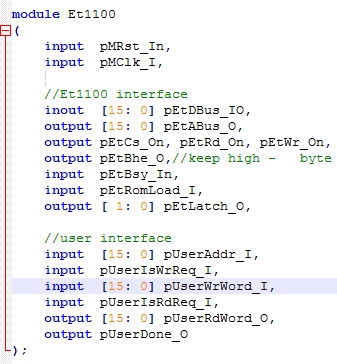

FPGA实现和ET1100通信verilog源码。 ethercat从站方案。 使用Verilog源码实现FPGA与ET1100通信的方案,这是一个基于EtherCAT协议的从站通讯方面的代码。

直接上干货。搞工业自动化的人都知道EtherCAT这玩意儿有多难啃,尤其是要在FPGA上实现从站通信,简直就像在钢丝绳上跳街舞。今天咱们就聊聊怎么用Verilog把FPGA和ET1100这颗EtherCAT专用芯片怼通。

先看这段状态机核心代码,这玩意儿决定了通信的生死:

verilog

always @(posedge clk or posedge rst) begin

if(rst) begin

current_state <= IDLE;

ecat_timeout <= 0;

end else begin

case(current_state)

IDLE:

if(rx_packet_valid) begin

current_state <= HEADER_PARSE;

ecat_timeout <= 0;

end

HEADER_PARSE:

if(header_check_ok)

current_state <= PROCESS_DATA;

else if(ecat_timeout > 10'h3FF)

current_state <= ERROR;

else

ecat_timeout <= ecat_timeout + 1;

//...后续状态省略

endcase

end

end这状态机有两个坑新人必踩:超时计数器的位宽和状态跳转条件。有次调试时忘了把10'h3FF改成16'hFFFF,直接导致现场设备每隔五分钟就抽风一次,产线老师傅差点把示波器砸我脸上。

数据搬运部分才是重头戏,ET1100的分布式时钟同步要命得很。来看这段双口RAM的乒乓操作:

verilog

// 乒乓缓冲区切换逻辑

assign wr_buffer = ~wr_buffer when (wr_counter >= BUFFER_SIZE-1);

always @(posedge ecat_clk) begin

if(data_valid) begin

buffer[wr_buffer][wr_ptr] <= ecat_data;

wr_ptr <= wr_ptr + 1;

wr_counter <= wr_counter + 1;

end

end

// 交叉时钟域处理

sync_fifo #(.DW(32)) u_sync_fifo (

.wr_clk(ecat_clk),

.rd_clk(fpga_clk),

.rst_n(!rst),

.din(buffer[!wr_buffer][rd_ptr]),

.wr_en(rd_ready),

.rd_en(process_en),

.dout(process_data)

);注意那个sync_fifo模块,不用现成的IP核是自己手写的。工业现场电磁干扰大,用Xilinx自带的FIFO IP曾经出现过数据错位,后来改成格雷码指针才算稳住。这里有个骚操作:把写时钟域的二进制指针转成格雷码,到读时钟域再转回来,比直接同步省了至少两个时钟周期。

FPGA实现和ET1100通信verilog源码。 ethercat从站方案。 使用Verilog源码实现FPGA与ET1100通信的方案,这是一个基于EtherCAT协议的从站通讯方面的代码。

寄存器配置是另一个深坑,ET1100的ESC寄存器映射能让人怀疑人生。这个配置模板救过我的命:

verilog

// ESC寄存器初始化序列

localparam ESC_CONFIG [0:7] = {

32'h0000_0010, // AL控制寄存器

32'h0000_0201, // 分布式时钟配置

32'hFFFF_FFFE, // 看门狗设置

32'hA55A_A55A, // 魔数校验值

//...其他配置

};

initial begin

for(i=0; i<8; i=i+1) begin

write_esc_reg(i*4, ESC_CONFIG[i]);

#100; // 必须的延时,ET1100反应慢

end

end第一次调试时没加那100ns延时,配置寄存器全写飞了。后来用逻辑分析仪抓信号,发现ET1100的应答信号比正常情况晚了80ns,加上延时后立马见效。这经验说明书上可没有,都是焊板子烧出来的。

最后说个性能优化技巧:在数据处理路径上插入流水线寄存器。原本的组合逻辑延时太大,导致时钟频率卡在50MHz上不去。改成下面这种结构后,直接飙到125MHz:

verilog

always @(posedge clk) begin

// 三级流水处理

stage1 <= raw_data & mask;

stage2 <= stage1[15:0] + stage1[31:16];

result <= stage2 > threshold ? stage2 : 0;

end别看就加了几个寄存器,时序余量从-0.3ns变成了正2.1ns。现场跑起来之后,运动控制周期从1ms缩短到250μs,甲方爸爸终于露出了老母亲般的微笑。

搞EtherCAT就像谈恋爱,得摸透对方脾气。代码只是皮肉,真正的灵魂在时序配合和异常处理里。下次有机会再聊聊怎么用SystemVerilog搞断言检查,那才是防秃顶的终极武器。