fpga以太网多通道实时同步采集系统 下位机:FPGA AD7606 UDP 上位机:QT5.13 ad7606八通道同步采集最高采样率200khz,上位机发送指令开始采样和改变采样频率,下位机和上位机之间通过千兆以太网udp进行数据传输。 qt udp上位机接收数据绘制采样数据波形和存储数据(.txt) 整套系统,已验证可正常使用。 采样率可以从20kHz以10kHz递进至200kHz,通道可多样选择。

系统整体概述

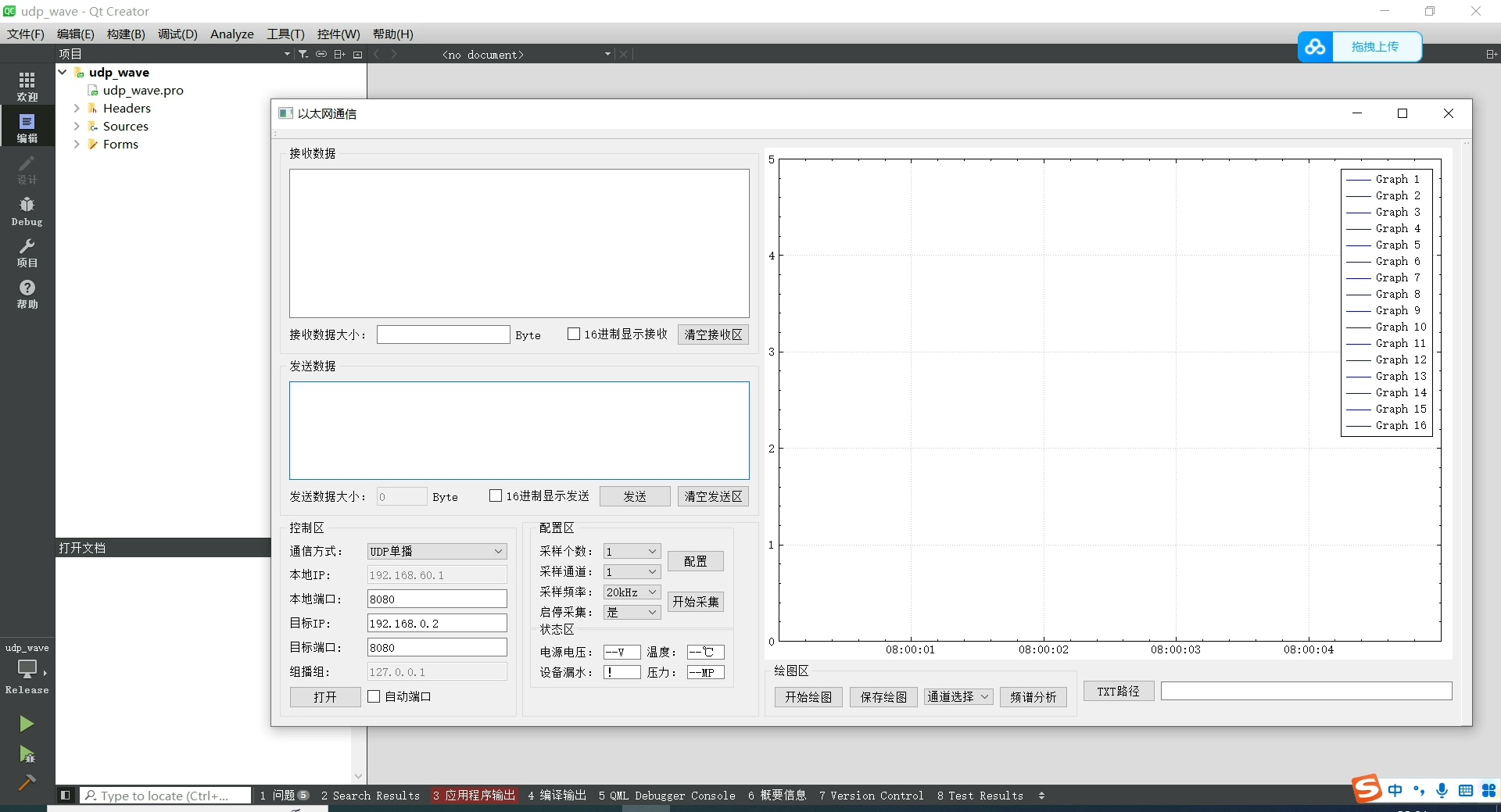

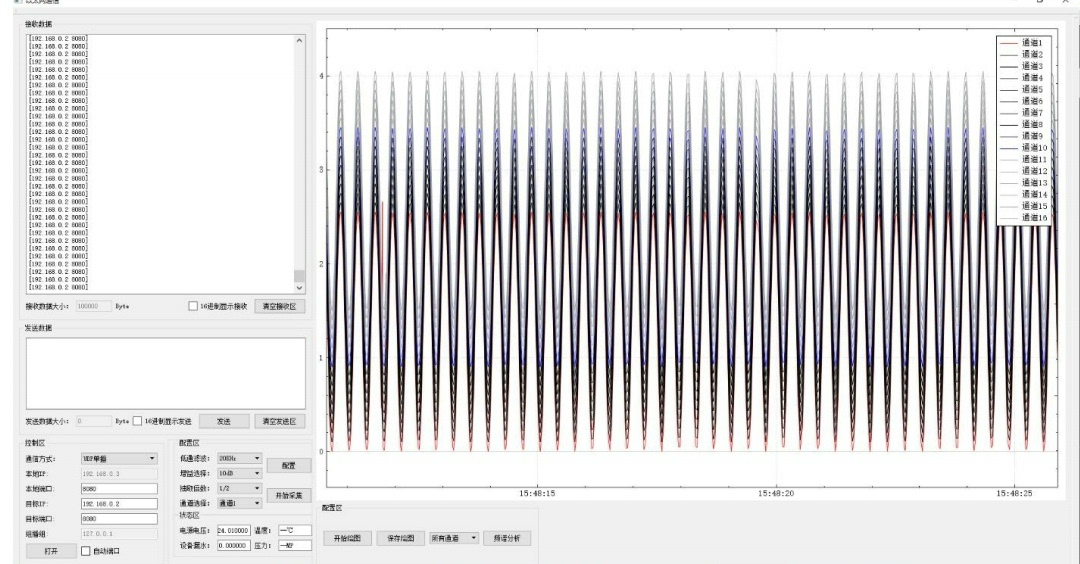

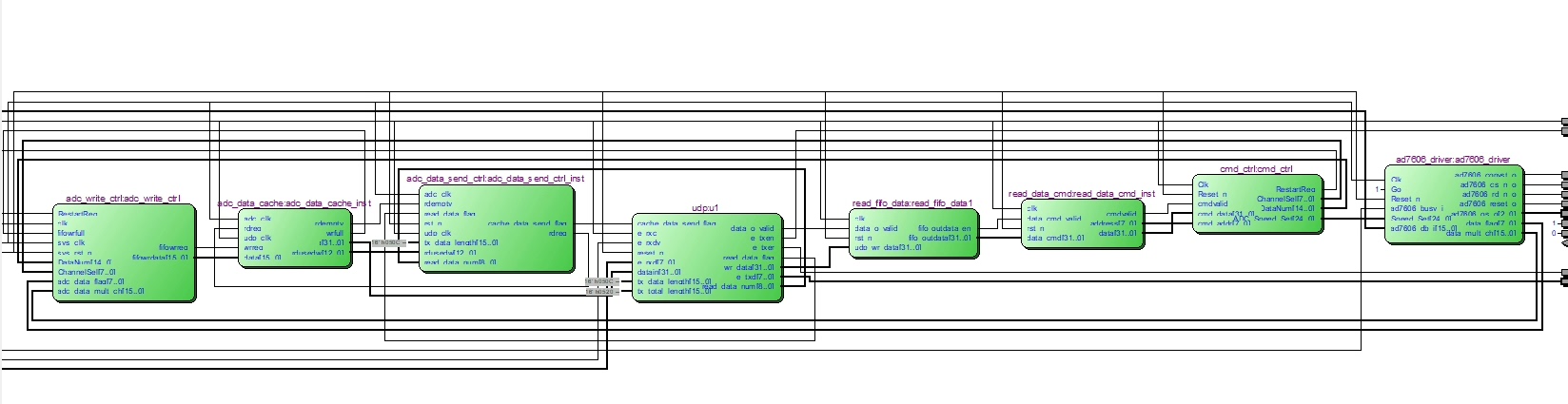

这个系统主要分为下位机和上位机两部分。下位机采用 FPGA 和 AD7606 来完成数据的采集,并且使用 UDP 协议进行数据传输。上位机则是基于 QT5.13 开发的,负责接收下位机传来的数据,绘制采样数据波形,还能把数据存储成 .txt 文件。

下位机部分

FPGA 与 AD7606

AD7606 是一个八通道同步采集的芯片,最高采样率能达到 200kHz。FPGA 就像是整个下位机的"大脑",负责控制 AD7606 进行数据采集。下面是一段简单的 Verilog 代码示例,用于控制 AD7606 启动采集:

verilog

module ad7606_control (

input wire clk,

input wire rst_n,

output reg convst, // 启动转换信号

input wire busy // AD7606 忙信号

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

convst <= 1'b0;

end else begin

if (!busy) begin

convst <= 1'b1; // 当 AD7606 不忙时,启动转换

end else begin

convst <= 1'b0;

end

end

end

endmodule代码分析:这段代码定义了一个名为 ad7606control**的模块,有时钟信号 clk、复位信号 rst n、启动转换信号 convst 和 AD7606 的忙信号 busy。在时钟上升沿或者复位信号有效时,会进行相应的操作。当复位信号有效时,convst 置为低电平;当 AD7606 不忙时,convst 置为高电平,启动一次数据采集。

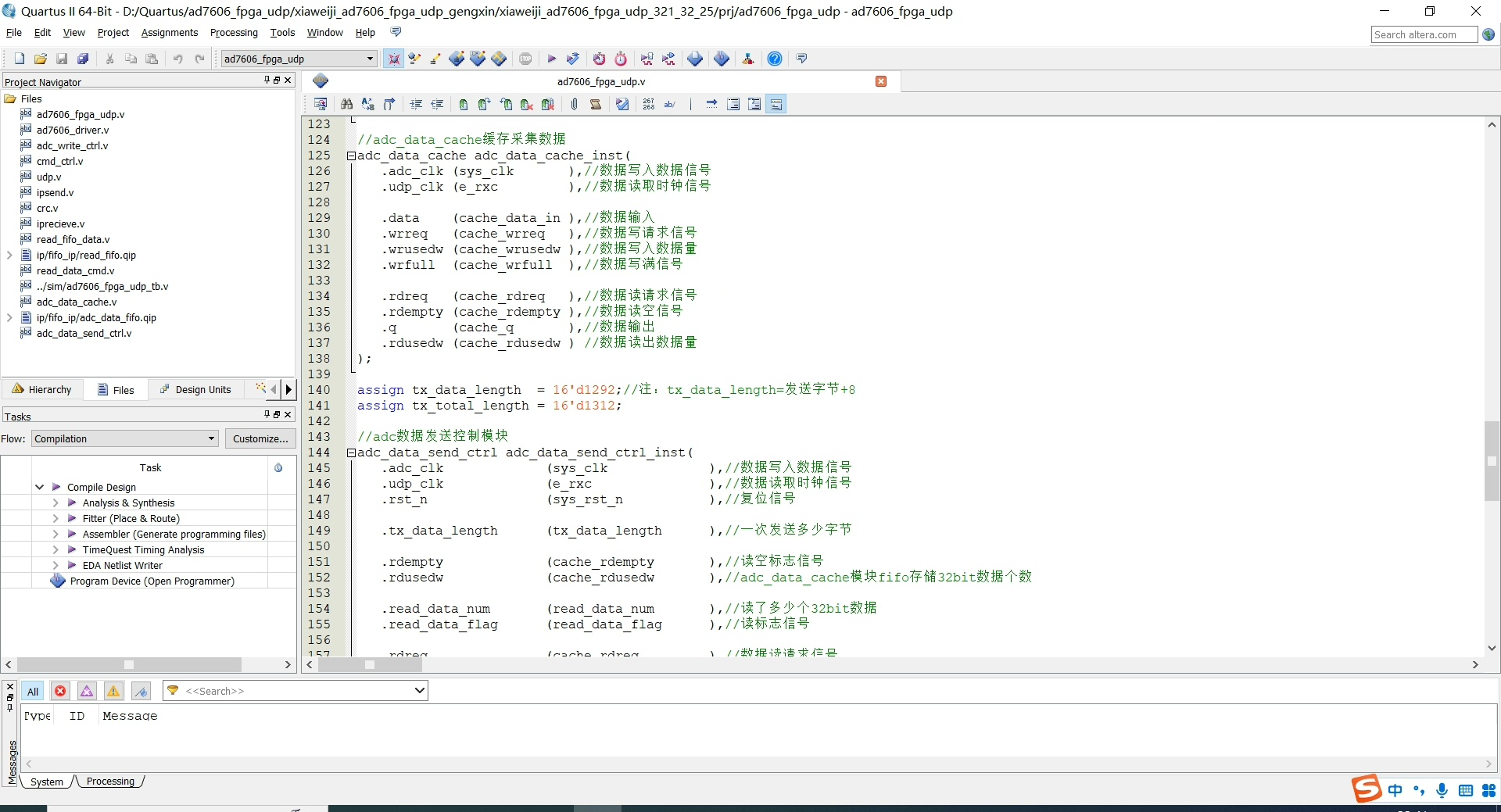

UDP 数据传输

FPGA 采集到数据后,要通过千兆以太网以 UDP 协议把数据发送给上位机。下面是一段简单的 UDP 发送代码示例(这里只是简化示意):

verilog

module udp_send (

input wire clk,

input wire rst_n,

input wire [15:0] data_in, // 采集到的数据

output reg [7:0] tx_data, // 发送的数据

output reg tx_valid // 发送有效信号

);

reg [3:0] state;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

state <= 4'b0000;

tx_data <= 8'b0;

tx_valid <= 1'b0;

end else begin

case (state)

4'b0000: begin

tx_data <= data_in[15:8]; // 先发送高 8 位

tx_valid <= 1'b1;

state <= 4'b0001;

end

4'b0001: begin

tx_data <= data_in[7:0]; // 再发送低 8 位

tx_valid <= 1'b1;

state <= 4'b0000;

end

default: begin

tx_data <= 8'b0;

tx_valid <= 1'b0;

state <= 4'b0000;

end

endcase

end

end

endmodule代码分析:这个 udp_send 模块用于将采集到的 16 位数据分成高 8 位和低 8 位依次发送。通过一个状态机来控制发送过程,状态 0 发送高 8 位,状态 1 发送低 8 位,然后回到初始状态。

上位机部分

上位机是用 QT5.13 开发的。它主要有两个功能,一是接收下位机传来的 UDP 数据,二是绘制采样数据波形并存储数据。下面是一段简单的 QT 代码示例,用于接收 UDP 数据:

cpp

#include <QUdpSocket>

#include <QDebug>

class UdpReceiver : public QObject

{

Q_OBJECT

public:

UdpReceiver(QObject *parent = nullptr) : QObject(parent)

{

socket = new QUdpSocket(this);

if (socket->bind(QHostAddress::Any, 1234)) { // 绑定端口 1234

connect(socket, SIGNAL(readyRead()), this, SLOT(readPendingDatagrams()));

} else {

qDebug() << "Failed to bind socket";

}

}

private slots:

void readPendingDatagrams()

{

while (socket->hasPendingDatagrams()) {

QByteArray datagram;

datagram.resize(socket->pendingDatagramSize());

QHostAddress sender;

quint16 senderPort;

socket->readDatagram(datagram.data(), datagram.size(), &sender, &senderPort);

qDebug() << "Received datagram:" << datagram;

// 这里可以添加绘制波形和存储数据的代码

}

}

private:

QUdpSocket *socket;

};代码分析:这个 UdpReceiver 类继承自 QObject,在构造函数中创建了一个 QUdpSocket 对象,并绑定到端口 1234。如果绑定成功,就连接 readyRead() 信号到 readPendingDatagrams() 槽函数。在 readPendingDatagrams() 函数中,会不断读取接收到的 UDP 数据报,并打印出来。后续可以在这个函数里添加绘制波形和存储数据的代码。

系统特点

这个系统的采样率可以从 20kHz 以 10kHz 递进至 200kHz,而且通道可以多样选择。上位机还能发送指令来控制下位机开始采样和改变采样频率,非常灵活。经过验证,整套系统可以正常使用,能很好地完成多通道实时同步采集的任务。

fpga以太网多通道实时同步采集系统 下位机:FPGA AD7606 UDP 上位机:QT5.13 ad7606八通道同步采集最高采样率200khz,上位机发送指令开始采样和改变采样频率,下位机和上位机之间通过千兆以太网udp进行数据传输。 qt udp上位机接收数据绘制采样数据波形和存储数据(.txt) 整套系统,已验证可正常使用。 采样率可以从20kHz以10kHz递进至200kHz,通道可多样选择。

总的来说,这个 FPGA 以太网多通道实时同步采集系统结合了硬件和软件的优势,在数据采集和处理方面有不错的表现,希望我的分享能给大家一些启发!