马年大吉,恭祝新春快乐

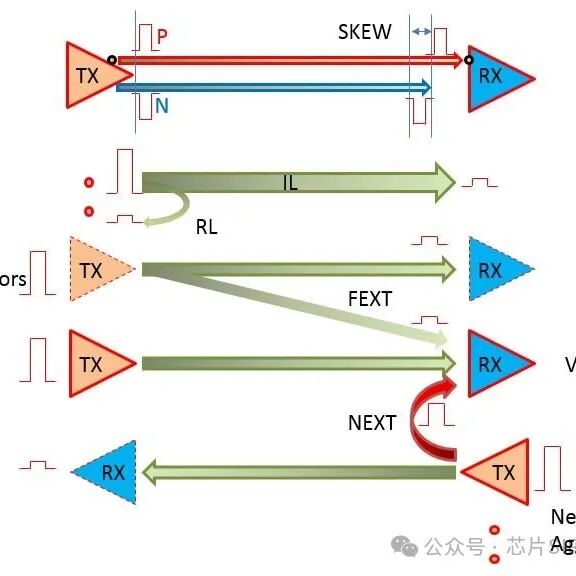

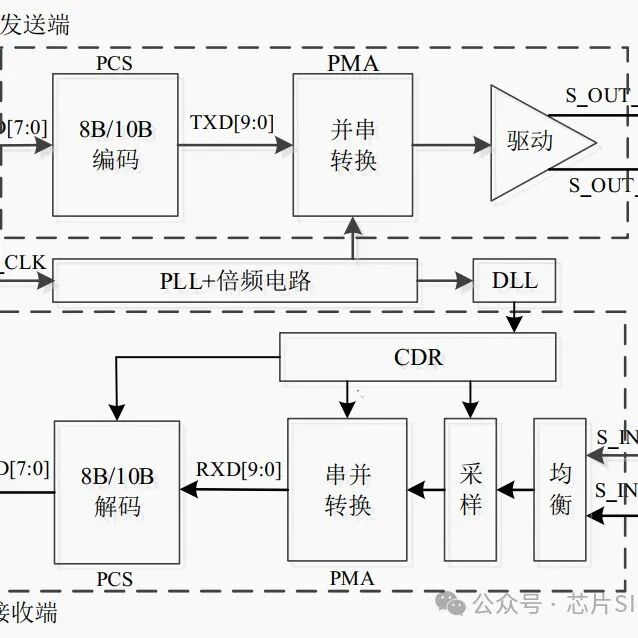

地回流是采用串并转换器(SerDes,Serializer/Deserializer)电路进行高速串行数据传输的关键环节,这类电路采用差分信号传输方式。信号通过印刷电路板(PCB)上的走线传输,而地回流路径对确定走线的特性阻抗至关重要。地回流是指与走线上信号电流方向相反的电流。

为避免不必要的反射、串扰或信号衰减,确保传输信号具备良好的地回流路径至关重要。若地回流路径不明确,由于走线存在有限电阻,信号可能会出现显著的电压降,进而导致信号损耗、偏斜和抖动。这些问题会严重降低信号完整性,引发误码,最终降低通信系统的可靠性和整体性能。

在印刷电路板中,地平面或电源平面充当高速信号的专用回流路径。回流路径的布线应保持连续,以维持走线的阻抗特性,提供低电感、低电阻的回流路径,最大限度地减少走线上的电压降。此外,回流路径应尽可能靠近信号走线,以减小回路面积,从而降低对电磁干扰(EMI)的敏感性。

垂直接入互连(过孔,VIAs)用于连接所有地平面结构,在高速串并转换器(SerDes)电路中常被用作地回流路径,以提供低电感、低电阻的地回流通道。过孔(VIA)是一种金属化孔,用于实现印刷电路板不同层之间的连接,允许地回流在各层之间流动,并将各个地平面/电源平面连接在一起。

封装到基板传输建模的重要性

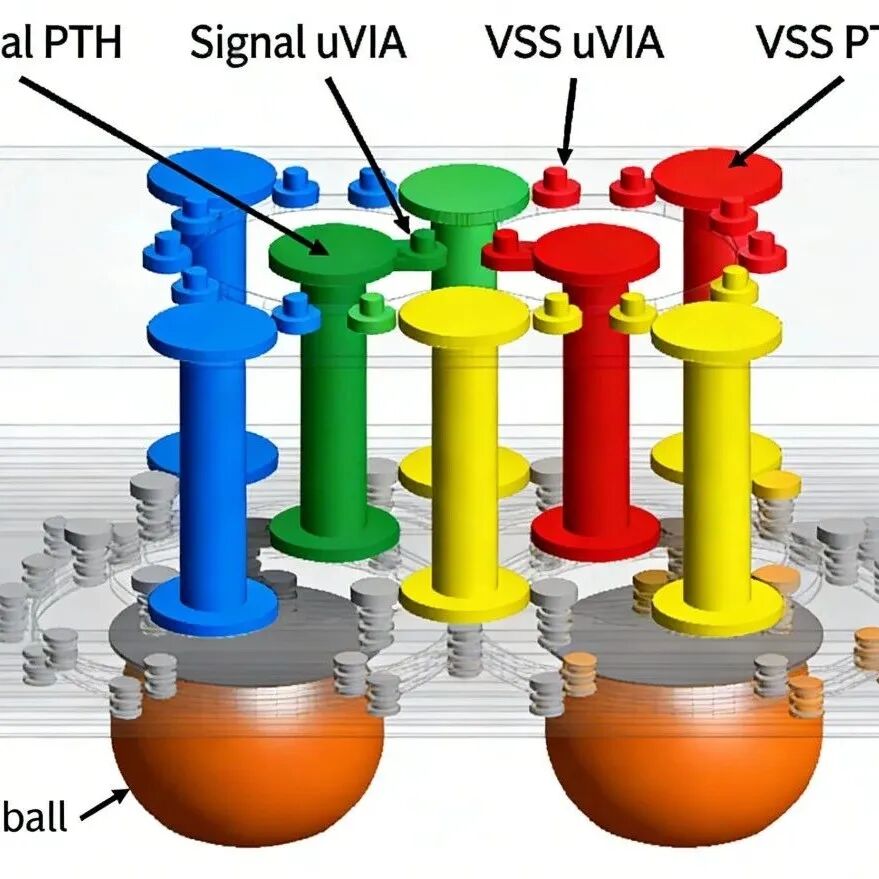

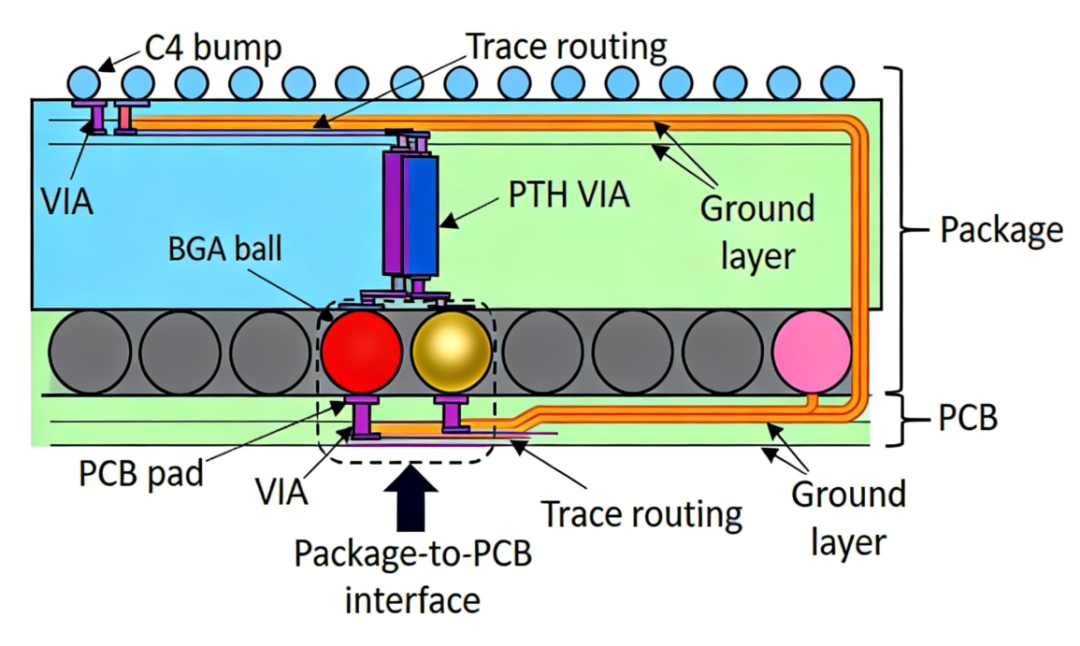

封装到基板的传输建模是包括100G以太网串并转换器(SerDes)在内的高速通信系统设计与开发的关键环节。封装到基板的传输是封装与印刷电路板(PCB)之间的接口,会对系统的整体性能产生显著影响。图1展示了封装到基板的传输示意图。

图1:封装到基板的传输

封装到基板的传输具有阻抗不连续性特征,这会导致信号出现反射和串扰。为最大限度地降低封装到基板传输对信号的影响,对封装和基板进行联合建模至关重要。仿真工具的应用,如3D电磁(EM)仿真和高频电路仿真,对于实现准确的封装到基板传输建模不可或缺。

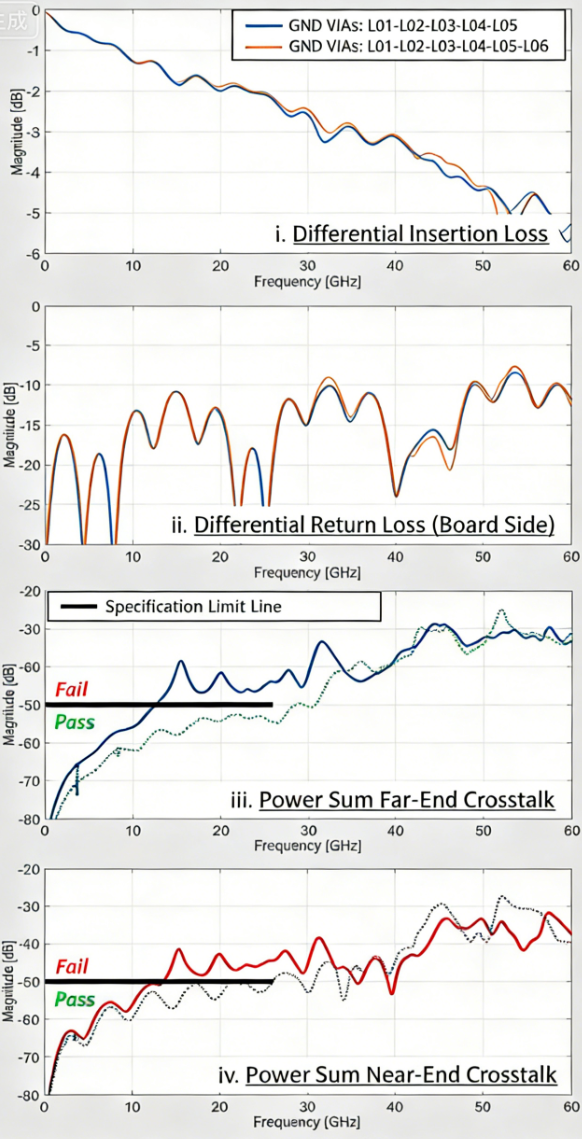

对封装到基板的传输进行了仿真分析,其中封装部分的结构为:可控塌陷芯片连接(C4)凸点→过孔(VIA)→走线布线→镀通孔(PTH)过孔→球栅阵列(BGA)焊球;PCB部分的结构为:焊盘→过孔(VIA)→走线布线。封装和PCB上的走线均采用对称带状线结构,两侧均设置地平面。仿真过程中,针对一组包含1个受害信号对和3个干扰信号对的四对差分信号,对差分插入损耗、差分回波损耗、功率和远端串扰以及功率和近端串扰进行了捕获。在功率和串扰测试中,耦合度定义为受影响信号对中所有干扰信号的功率之和与同一信号对中期望信号功率的比值。

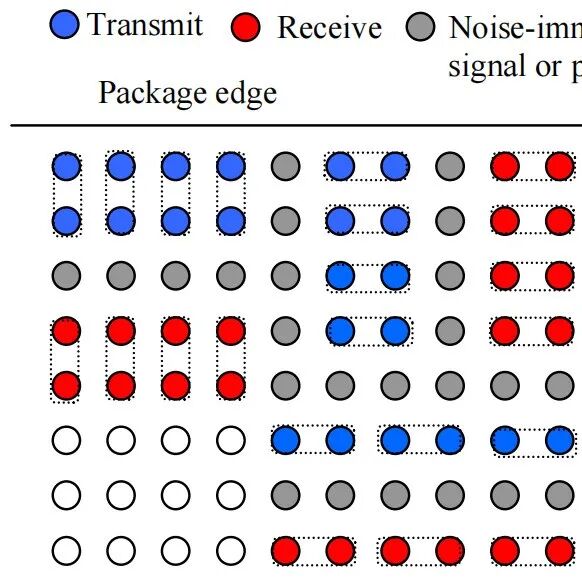

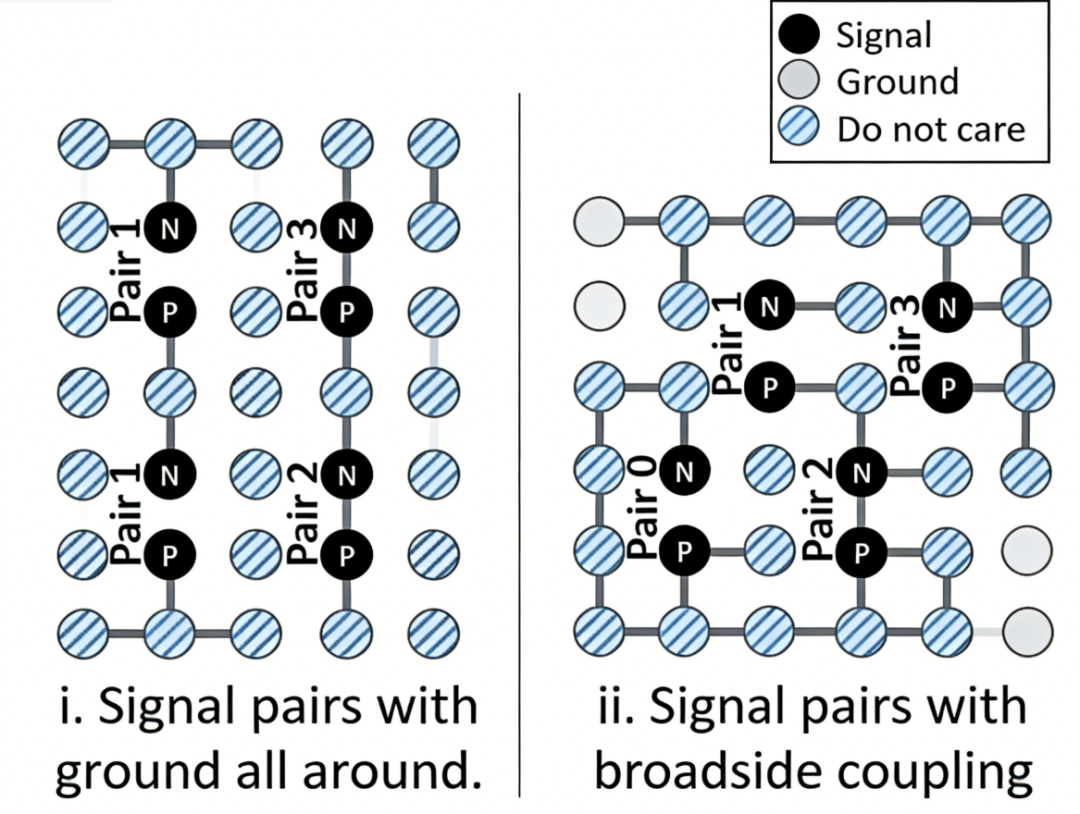

图2:两组串并转换器(SerDes)四通道的BGA焊球图

球图中地平面的重要性

地回流所用过孔(VIA)的数量取决于具体应用需求、电路板设计、走线布线以及功率要求。过孔(VIA)数量越多,可提供的地回流路径电感和电阻越低,信号完整性越好。然而,过多的过孔(VIA)会增加PCB设计的成本和复杂度。通过地过孔(VIA)连接各层地平面是高速串并转换器(SerDes)应用(包括100G以太网)中的常见做法。

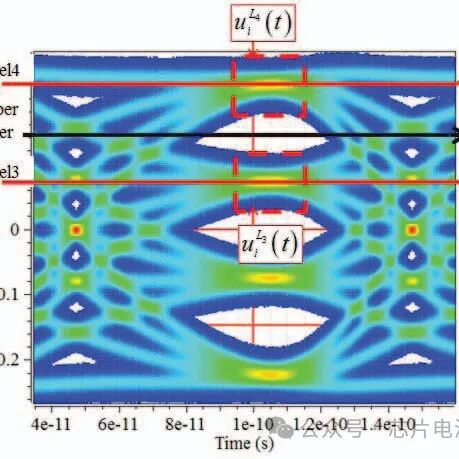

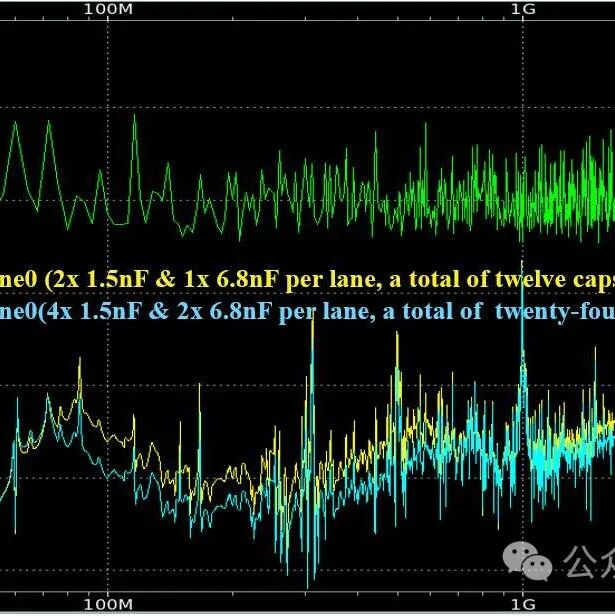

当走线和过孔(VIA)的电感与电容形成谐振电路时,会产生谐振现象,导致信号出现不必要的振荡。这些振荡会造成严重的信号衰减,包括抖动增大和眼图张开度减小。对于奈奎斯特频率为26.5625 GHz的100G PAM4以太网,在高频段可能会出现谐振现象,此时走线和过孔(VIA)的寄生电感和寄生电容可能会降低整体信号质量。

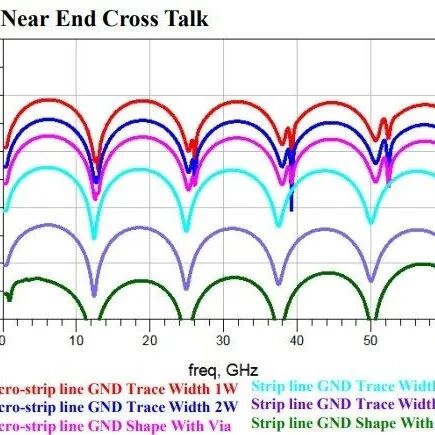

另一方面,串扰是指一条走线上的电场与另一条走线耦合,对信号造成干扰。地过孔(VIA)布局不当会导致走线回路面积扩大,从而增加串扰风险,使信号更容易受到其他信号的干扰。为避免这一问题,应尽可能多地布置地过孔(VIA),确保信号对之间不共享单个地过孔(VIA)。对于100G PAM4以太网,串扰会导致严重的信号衰减,缩短端到端通道的传输距离。

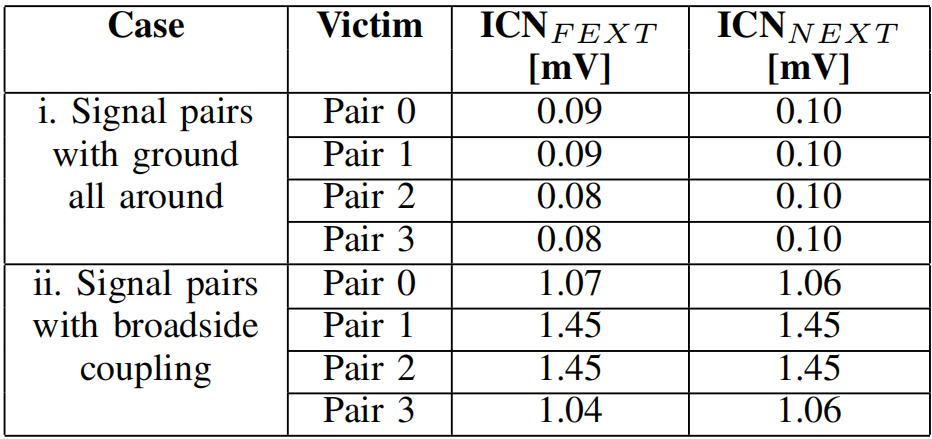

在BGA焊球图设计中,地连接的重要性日益凸显,尤其是在追求满足100G PAM4以太网需求的场景下。积分串扰噪声(ICN)是指在特定时间段内,相邻信号线通过串扰对某一信号造成的总噪声或干扰量。积分串扰噪声考虑了一段时间内这种干扰的累积效应,通常以原始信号幅度的百分比或功率单位来衡量。它是决定以太网等高速通信系统信号完整性的关键参数,可通过合理的信号布线、屏蔽及其他设计技术来最小化。

如图2所示,展示了BGA结构中两组串并转换器(SerDes)四通道的焊球图:第一种是信号对周围环绕地平面,第二种是信号对存在宽边耦合,其中存在宽边耦合的信号对所需的BGA焊球数量更少。由此可见,在焊球图层面,地连接的数量需求明显高于信号连接和电源连接。表1为封装与基板联合仿真后,工作于100G PAM4的一组串并转换器(SerDes)四通道信号对的远端串扰和近端串扰结果。结果清晰表明,与信号对周围环绕地平面的情况相比,存在宽边耦合的信号对的积分串扰噪声(ICN)显著更高(约为12倍)。因此,确保地平面与信号BGA焊球的合理比例,对于维持地平面连续性和良好的地回流路径至关重要。

表1:工作于100G PAM4的一组串并转换器(SerDes)四通道信号对的串扰结果

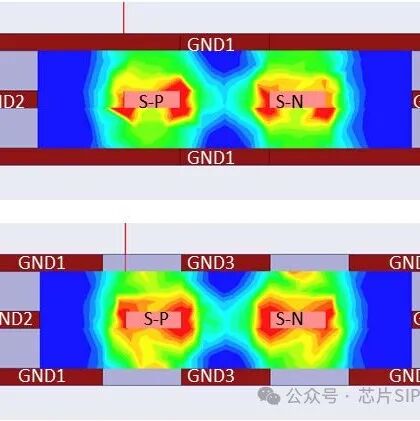

地缝合过孔

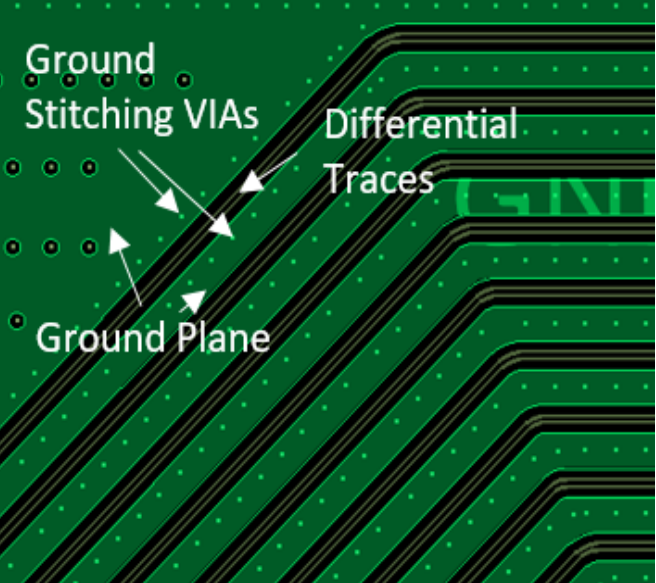

地缝合过孔是在印刷电路板上周期性排列的过孔阵列,用于连接多个层上的地网络。它们有助于减小回路面积,并提供明确的地回流路径。图3展示了地缝合过孔在差分串并转换器(SerDes)走线上的应用。

图3:差分串并转换器(SerDes)走线的地过孔墙

五、地过孔的不连续性

串扰是100G PAM4以太网串并转换器(SerDes)系统中的一个重要问题,因为它会导致严重的信号衰减,并使接收器接收到的数据出现大量错误。串并转换器(SerDes)电路的设计也会影响100G以太网串并转换器(SerDes)对串扰的敏感性。例如,采用差分信号传输(信号在一对极性相反的走线上传输)有助于降低对串扰的敏感性。此外,运用均衡技术(如均衡滤波器和均衡电路)也有助于最大限度地减小串扰对信号的影响。

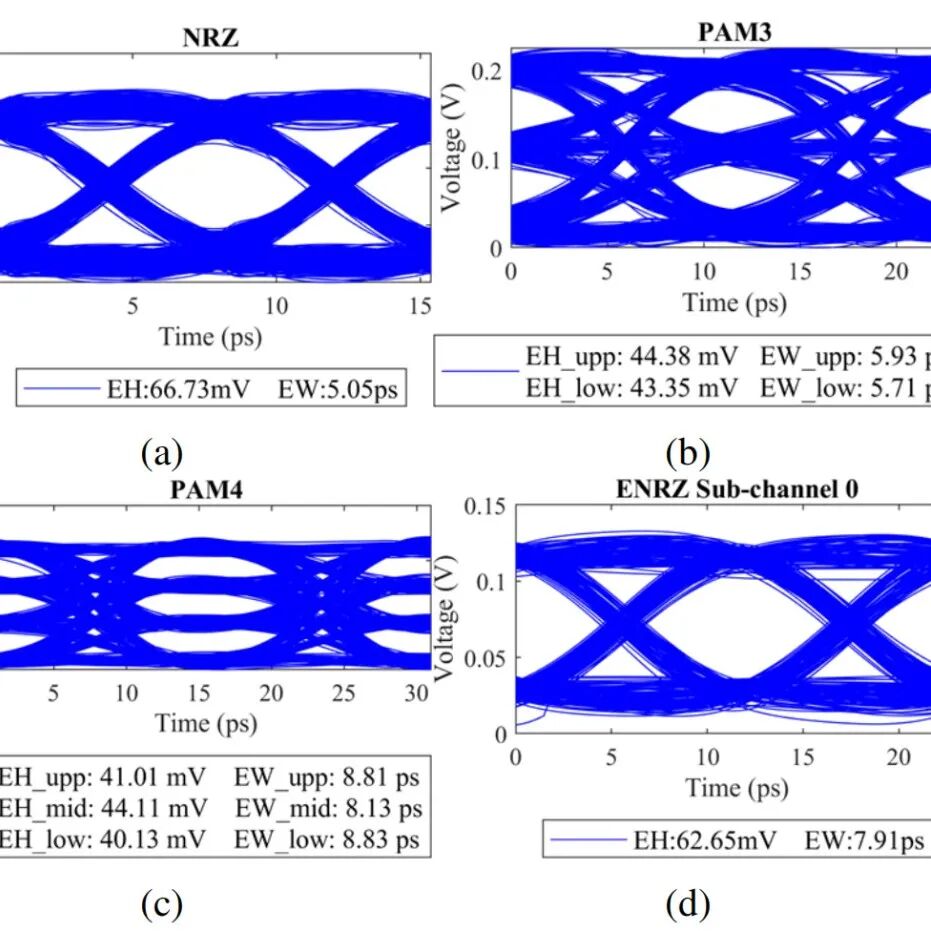

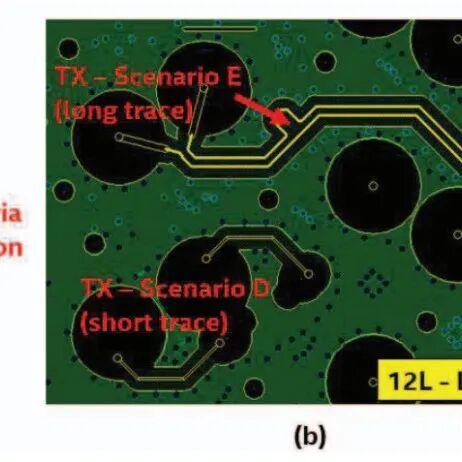

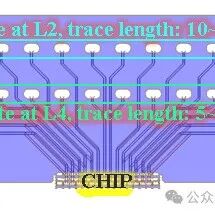

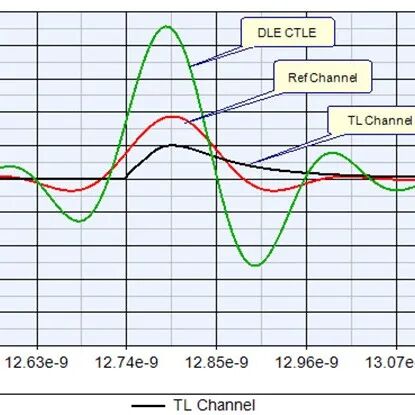

图4展示了通过100G PAM4以太网仿真得到的封装到基板传输处地过孔不连续性对差分插入损耗、差分回波损耗、功率和远端串扰以及功率和近端串扰的影响。信号从封装到基板的传输通过BGA焊球实现:BGA焊球连接至焊盘,再通过过孔(VIA)连接至布线层。布线层位于第5层,第4层和第6层为地参考平面。地过孔(VIA)为信号从顶层传输到布线层提供通路。此外,布线层(第5层)至下方第6层地平面也需设置地过孔(VIA),为第5层走线上的信号提供地参考。

图4:封装到基板传输处地过孔不连续性的相关结果

远端串扰和近端串扰的仿真结果表明,当通过地过孔(VIA)连接两个地参考平面,建立明确的地回流路径以抑制谐振时,设计符合规格限制线要求。然而,需要注意的是,差分插入损耗和回波损耗并不总能准确反映地回流路径的质量。因此,至关重要的是,确保印刷电路板上所有与布线走线耦合的结构都具备良好的地连接,尤其是在封装到基板的传输区域,即使基板上已布置地缝合过孔,也需避免地平面出现任何不连续性。

基于芯粒的设计

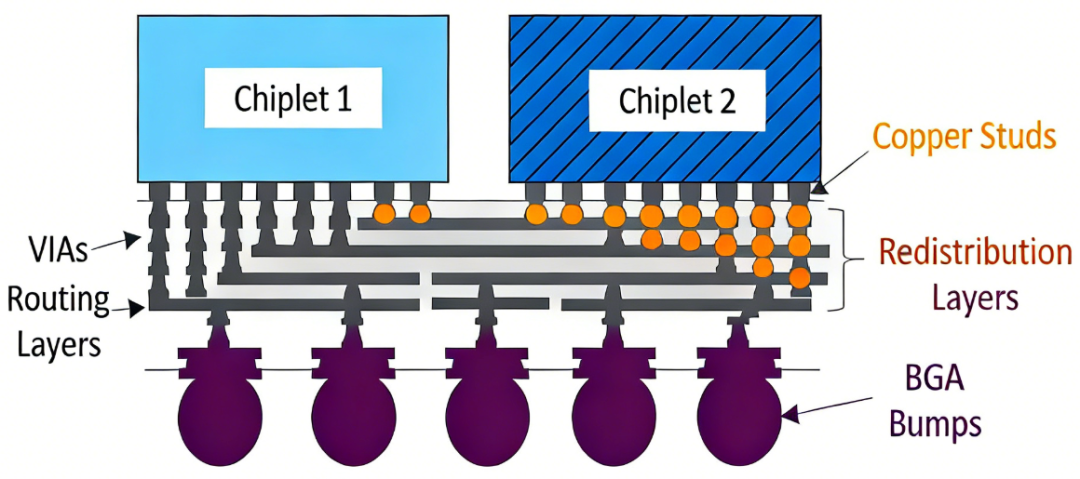

基于芯粒的设计是一种微电子设计与制造方法,即将多个较小的芯片(称为芯粒)组合在一个封装内,形成完整的片上系统(SoC)解决方案。这种方法能够整合制造工艺互不兼容的功能模块,从而提高设计灵活性,并实现不同工艺技术的高效利用。图5展示了基于芯粒的设计实现方式,即两个芯粒在基板上的连接结构。

图5:基板上连接的两个芯粒

地平面在基于芯粒的设计中起着重要作用,它提供公共参考点,以抑制噪声和干扰,但这一过程面临诸多挑战。其中一个挑战是芯粒之间的复杂互连,这些互连通常采用高速接口。这些互连可能会向系统引入显著的噪声和串扰,难以维持干净、低阻抗的地参考。另一个挑战是电源分配网络,由于芯粒通常来自不同供应商,可能导致电源分配网络存在差异。确保所有芯粒都具备一致、低阻抗的地参考具有一定难度。此外,芯粒内部的高速信号需要精心布线和屏蔽,以防止串扰并维持信号完整性,因此地连接是保证信号质量的关键因素。最后,用于封装芯粒的封装体本身也可能引入与地相关的问题,如阻抗不连续性和寄生参数,从而影响信号质量。

结论

对于速率接近100G的高速串并转换器(SerDes)设计,对封装到基板的传输进行建模以表征阻抗不连续性至关重要,因为阻抗不连续性会导致信号出现反射和串扰。BGA焊球图中充足的地连接有助于确保信号和地回流从封装到基板的平稳传输。信号从焊盘传输到布线层的过程中,每经过一层都应配备相应的地过孔(VIA)。在封装到基板的传输区域,尤其需要确保印刷电路板上所有与布线走线耦合的结构都具备良好的地连接,以避免地平面出现任何不连续性。

基于芯粒设计中的地连接是一个复杂问题,需要审慎考虑和合理的设计技术。为确保系统可靠、高性能运行,必须解决基于芯粒设计中地连接面临的挑战,包括复杂互连、电源分配难题、信号完整性问题和封装限制。为克服这些挑战,设计人员必须采用合理的设计和建模技术,确保地连接系统满足系统需求,并为芯粒内部的高速信号提供稳定、低阻抗的参考。这需要了解系统各组件对地连接系统的影响,以及各组件之间的相互作用。合理的地连接设计对于确保系统满足性能要求、可靠运行并适应广泛的工作条件至关重要。

112G PAM4/56G NRZ芯片封装互连设计和SI性能

四种编码的噪声性能比较:ENRZ、NRZ、PAM3与PAM4

56Gbps Serdes高速接口在FCBGA封装低IL设计方法

高速serdes接口在FCBGA封装设计上的Crosstalk问题的考虑