【引言:从"灰色世界"到"智能筛选"】

在 ISP 的设计中,自动白平衡(Auto White Balance, AWB)是决定图像"色彩高级感"的核心模块。初学者的 AWB 往往停留于"灰色世界假设(Gray World)",即认为整幅图的 R/G/B 平均值应该相等。但在实际商用场景中,大面积绿色草地或红色墙面会直接误导这种简单逻辑,导致画面严重偏色。

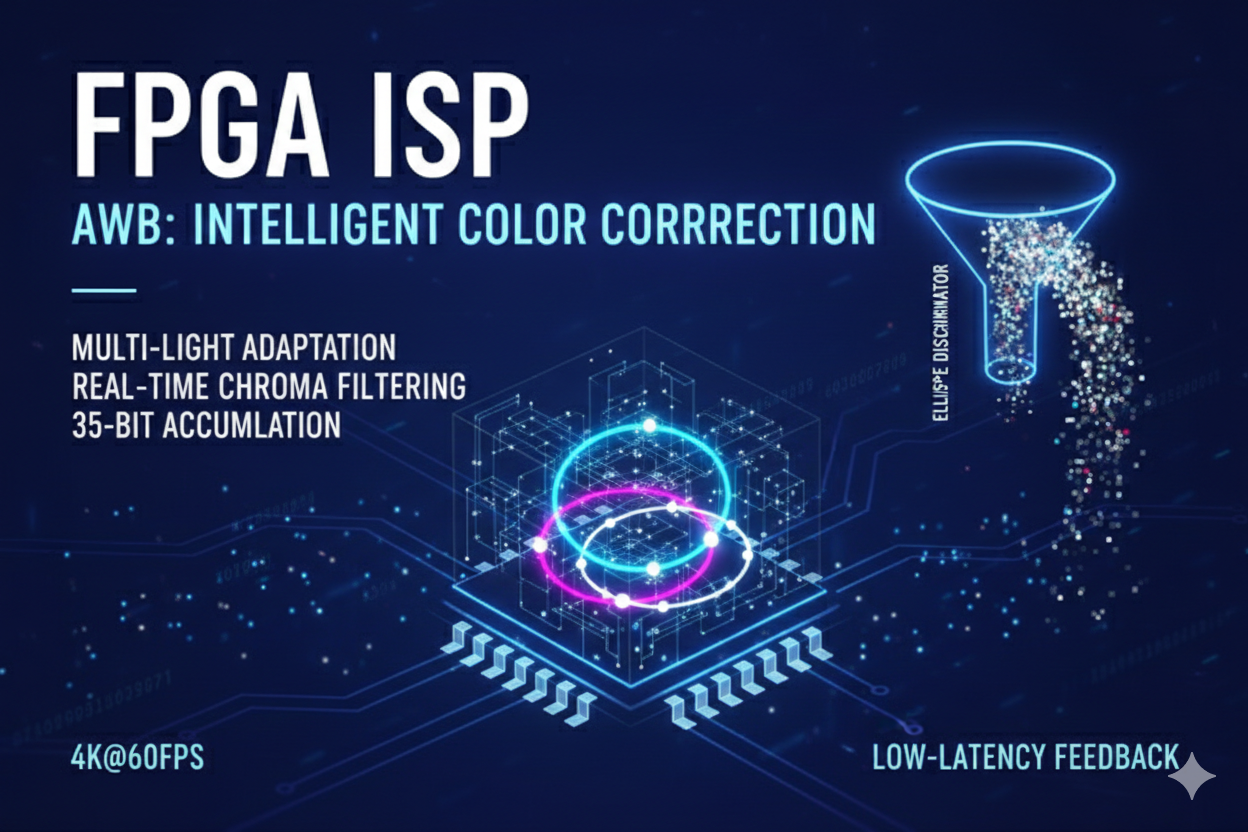

商用级 ISP 的解决方案是:统计引擎(Measurement Engine)硬件化。它通过复杂的筛选逻辑,在千万级像素流中实时"剔除假白点,保留真白点"。

一、 AWB 硬件流水线架构全景

一套成熟的 AWB 硬件架构通常分为预处理、空间转换、甄别统计、增益应用四个阶段。

-

预过滤阶段 (Pre-filtering):

根据硬件电路实现,系统在统计前会经过一个硬核的中值滤波器(Median Filter)。

- 源码逻辑: 硬件采用的是 5 点中值滤波(f_med5) 逻辑。相比于简单的均值滤波,这种 5 抽头的设计能在保留边缘特征的同时,精准剔除传感器产生的孤立高频噪点(热像素)。

- FPGA 实现: 通过 Line Buffer 缓存行数据,配合比较器阵列实时输出 5 个邻域像素的中值,为后续的色度判定提供极其"纯净"的像素输入。

-

色彩空间转换 (CSM):

RGB 空间并不利于白点的提取,硬件会将像素转换为 YCbCr 或专用的色度空间(如 U=R/G,V=B/GU = R/G, V = B/GU=R/G,V=B/G)。

- 架构细节: 通过流水线化的 3x3 矩阵乘法器实现。为了节省算力,定点数运算通常保留 10-12 bit 的精度。

二、 核心算法:色度椭圆甄别(Ellipse Discriminator)

这是博文中最重要的硬核技术点。为什么商用 ISP 偏爱椭圆?因为不同色温的光源在色度平面上的分布并非规则矩形,而是沿着黑体辐射曲线分布的。

1. 数学模型:

对于每一个像素的色度坐标 (x,y)(x, y)(x,y),我们需要判断它是否落在某个预设光源的范围内。判断公式为:

A(x−x0)2+B(x−x0)(y−y0)+C(y−y0)2<Rmax2A(x-x_0)^2 + B(x-x_0)(y-y_0) + C(y-y_0)^2 < R_{max}^2A(x−x0)2+B(x−x0)(y−y0)+C(y−y0)2<Rmax2

其中 (x0,y0)(x_0, y_0)(x0,y0) 是该光源下的白点中心。

2. FPGA 架构实现:

- 并行计算: 硬件内部通常配置 8 组以上的系数(A, B, C, Rmax),支持 8 种光源(如:D65、TL84、A光源等)并行判定。

- 计算链:

Subtract -> Square -> Multiply -> Accumulate。通过 FPGA 内部的 DSP Slice 级联,实现一个时钟周期处理一个像素的判定。 - 联合判定: 只有满足椭圆判定,且亮度 Y 在

[Y_min, Y_max]范围内的像素,才会被送入最终的统计单元。

三、 统计引擎:高动态范围的累加技术

当一个像素被判定为"有效白点"后,统计引擎会记录它的情报。

- 三通道累加器 (Accumulator):

- 挑战: 4K 图像有 800 万像素,如果全屏都是白点,累加值会非常大。

- 解决: 硬件采用 35-bit 宽度的加法器,确保即便在最大分辨率下也不会产生溢出(Overflow)。

- 白点计数器 (White Point Counter):

- 记录有多少像素进入了统计范围。如果计数值过小,算法层会判定当前统计结果"不可信",从而维持上一帧的增益。

- 均值计算 (Sequential Division):

- 每一帧结束后的垂直空白期(V-Blank),硬件利用一个时分复用的除法器,自动计算 Sum_R/CountSum\_R / CountSum_R/Count、Sum_G/CountSum\_G / CountSum_G/Count 等数值并存入结果寄存器。

四、 软硬件协同:AWB 的闭环反馈逻辑

AWB 的核心竞争力并不单纯在于硬件,更在于如何通过统计上报 -> 软件决策 -> 增益反馈建立实时闭环。结合工业级寄存器交互流程,我们可以清晰反推出这套架构的运作逻辑:

-

初始化与 ROI 设定:

在每一帧开始前,驱动程序通过总线配置统计窗口(Region of Interest)。

- 关键寄存器:

awb_h_offs(起始列)、awb_v_offs(起始行) 配合awb_h_size和awb_v_size。这不仅能避开暗角,还能让算法只关注画面中心区域。同时,驱动会预载多组椭圆系数(如ellip_a、ellip_b等)至硬件判定阵列。

- 关键寄存器:

-

硬件并行的"光源探测":

硬件在实时处理像素时,会并行比对多个光源库。通过观察底层的累加寄存器堆可以发现,系统会同时维护多个光源下的 R/G/B 分量加和。这种设计允许 ISP 在同一帧内同时获得"日光"和"阴影"下的统计数据,为后续的混合光源判定提供依据。

-

中断驱动的数据读取:

当硬件检测到帧结束信号(V-End)后,会自动触发均值计算并拉高

awb_done中断。此时,驱动程序从只读统计寄存器中取出核心情报:- White_Pixel_Count: 判定当前场景是否有足够的有效参考白点。

- Mean_R / Mean_G / Mean_B: 获取当前场景下最贴近真实光源色彩的分量均值。

-

增益的"原子化"更新:

驱动计算出最新的 R/G/B Gain 后,写入增益控制寄存器(如

gain_r,gain_b)。- 核心细节: 所有的增益更新必须配合一个"更新触发位(Config_Update)"。只有当该位被置 1 时,硬件才会利用

Start of Frame信号将新系数同步到全流水线。这种影子寄存器(Shadow Register)机制确保了即便在 AWB 快速剧烈抖动时,单帧图像内部的色彩也绝对一致,彻底杜绝画面撕裂。

- 核心细节: 所有的增益更新必须配合一个"更新触发位(Config_Update)"。只有当该位被置 1 时,硬件才会利用

五、 性能优化与工程经验分享

在实际 FPGA 开发中,有几个关键点需要关注:

- ROI 窗口策略: 图像边缘通常有镜头暗角,建议在 AWB 窗口设置中避开边缘 5% 的区域,以获得更准确的色彩统计。

- 增益平滑(Anti-Oscillation): 不要直接应用计算出的全量 Gain。建议在软件层做一个平滑滤波,让 Gain 缓慢趋近目标值,防止画面在微小光线变化下频繁闪烁。

- 阈值保护: 结合

min_y和max_y寄存器限制,剔除过暗或过亮的无效像素,能显著提升在极端环境下的稳定性。

【结语】

自动白平衡 AWB 是 ISP 系统中最具挑战性的环节之一。它将解析几何(椭圆判定) 、统计学 与FPGA 高速流水线架构完美结合。理解了这套筛选与累加的机制,你就掌握了商用 ISP 色彩管理的核心密码。