本文介绍一种基于FPGA的低资源AGC(自动增益控制)设计与Verilog实现。该设计仅消耗1个DSP乘法器资源,在50MHz时钟下收敛时间仅需10μs。文章详解AGC工作原理、反馈环路设计,包含完整的工程代码与仿真结果。

一、引言

AGC(Automatic Gain Control,自动增益控制)是一种能够根据输入信号强度自动调整增益的闭环控制系统,其核心目标是无论输入信号强弱如何变化,输出信号的幅度都能保持在期望的范围内。

这种特性使得AGC在无线通信、音频处理、雷达接收机等众多领域成为不可或缺的关键模块。

在实际工程应用中,AGC的设计需要在资源消耗、收敛速度和控制精度之间进行权衡。

二、AGC 工作原理

见第四部分资源下载,下载后word有AGC工作原理介绍。

三、仿真结果及分析

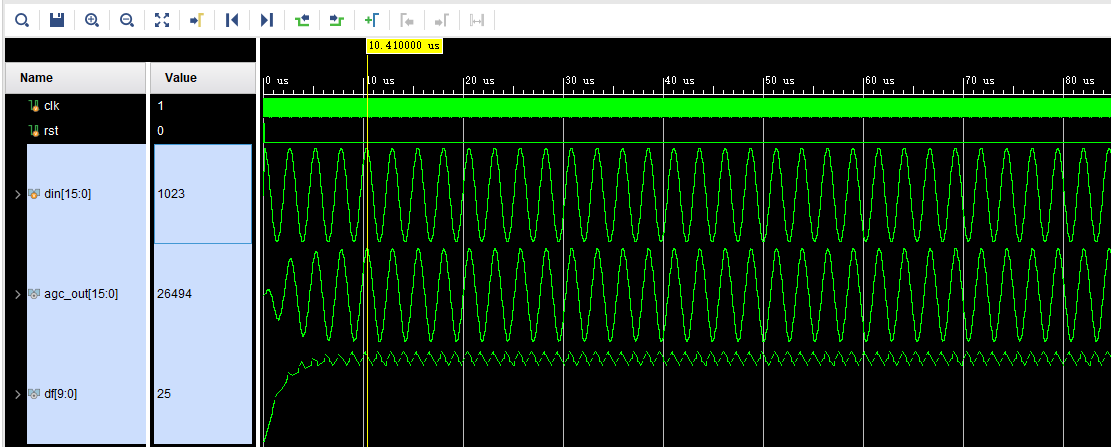

仿真结果如下图所示。

| 信号 | 说明 | 预期行为 |

|---|---|---|

din |

输入信号 | 稳定的正弦波,幅度约±1024 |

agc_out |

AGC 输出 | 初始有瞬态过程,随后稳定放大 |

df |

增益系数 | 从 0 开始增长,最终稳定在某一值 |

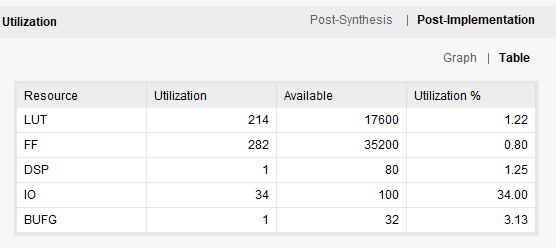

资源消耗如下图所示。

可见本文介绍的AGC方案仅使用1个DSP核配合移位寄存器和加法器即可实现稳定的增益控制,在50MHz工作时钟下收敛时间约为10μs,具有资源占用少、响应速度快、易于实现等优点。

四、源代码下载

点击下面文字即可下载。

FPGA实现AGC自动增益控制的Verilog实战代码(Vivado工程)