一、 概述

在上一章节我们介绍了hdmi的输入接口详情,和热插拔的工作原理,为了能使对方的HDMI读取EEPROM中的EDID数据,我们可以在FPGA模拟EEPROM的响应程序,介入EDID内容,再通过IIC协议将EDID内容传输给显示器。

二、 了解IIC通信协议

1、IIC介绍:

IIC(inter-Integrated Circuit)即集成电路总线,它是一种具有两线传输的串行通信总线,使用多主从架构,由飞利浦公司在1980年为了让主板、嵌入式系统或手机连接低速周边设备而发展,适用于数据量不大且传输距离短的场合。

IIC串行总线由两根信号线组成,一根是双向的数据线SDA,另一根是单向的时钟线SCL,在空闲状态时,SDA和SCL线都置'1',为高电平。

IIC为同步的半双工通信方式

2、 传输协议:

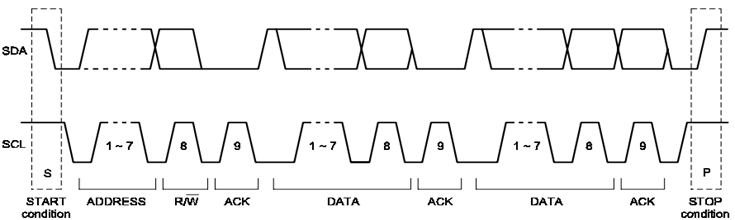

在空闲状态下,SCL及SDA都是置高的状态,当需要进行一次IIC传输时,由START信号指示当前数据传输开始,由STOP信号指示当前的数据传输结束,START信号的标识是在SCL高电平情况下,SDA信号由高变低 ,即视为START开始,STOP信号标识是在SCL高电平情况下,SDA信号由低变高,即视为STOP结束,START信号与STOP信号之间的信号流即为所传输信号。每传输一个字节数据需要九个时钟脉冲,前8个时钟用来传输数据,第九个时钟脉冲期间由对方反馈ACK应答。

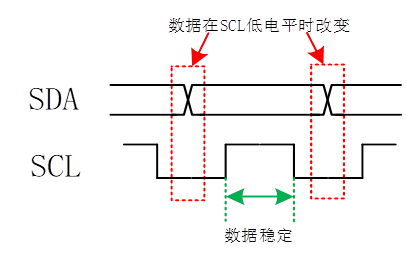

3、数据有效性:

IIC进行传输时,数据data的改变必须在SCL信号为低电平时进行,在SCL为高电平时保持稳定,此时认为在SCL为高电平时的数据有效,其时序如下图所示:

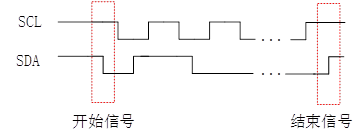

开始&结束信号:

IIC传输的开始及结束如下图2所示,在SCL为高电平期间,SDA由高变低,即为start信号;在SCL为高电平期间,SDA信号由低变高,即为stop信号

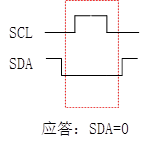

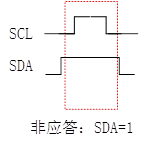

应答信号:

单片机发完8bit数据后就不再驱动总线了(SDA引脚变输入),而SDA和SDL硬件设计时都有上拉电阻,所以这时候SDA变成高电平。那么在第8个数据位,如果外接IIC设备能收到信号的话接着在第9个周期把SDA拉低,那么处理器检测到SDA拉低就能知道外接IIC设备数据已经收到。IIC数据从最高位开始传输。响应的具体时间开始于第8个时钟下降沿后,结束于第9个时钟的下降沿后。再这一段时间内,SDA端口要保持高阻态,释放SDA,用于接收从器件的应答信号。SDA和SDL硬件设计时都有上拉电阻,默认为高电平,如果从器件正确接收到了8bit的数据,就会在第9个时钟周期将SDA拉低,SDA信号为低。如果从设备没有足球接收到8bit数据,不会讲SDA拉低,SDA将保持高电平,说明该8bit数据发送失败,主机会先发送停止信号,终止该次传输,然后重新启动一个新的数据传输。

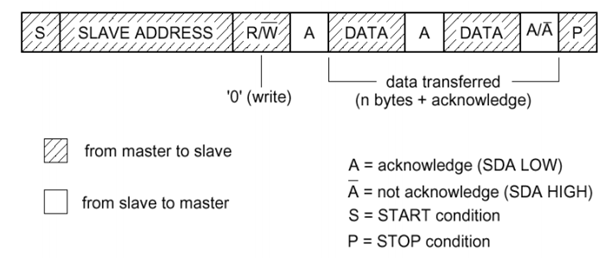

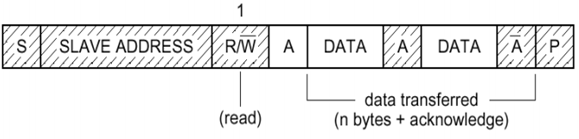

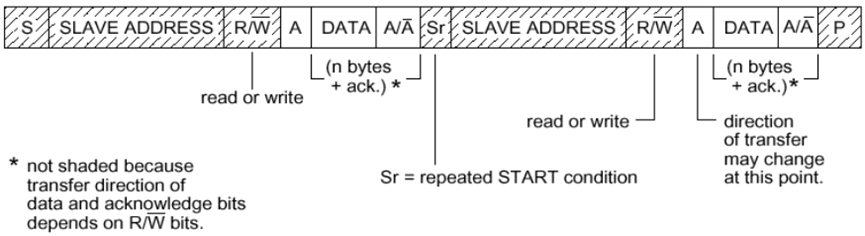

4、 七位地址格式

数据的传输遵循图所示的格式。在起始条件(S)后,发送了一个从机地址。这个地址共有7位,紧接着的第8位是数据方向位(R/ W)---'0'表示发送(写),'1'表示发送请求数据(读)。数据传输一般由主机产生的停止位(P)终止。但是,如果主机仍然希望在总线上通讯,它可以产生重复起始条件(Sr)和寻址另一个从机,而不是首先产生一个停止条件。在这种传输中,可能有不同的读/写格式结合。注1:IIC总线协议中文手册 page 12、13

可能的数据传输格式有:

主机发送器件地址+写指令-----主机发送数据,从机接收数据。(图5)

主机发送器件地址+读指令-----从机发送数据,主机接收数据。(图6)

当想要传输方向改变的时候,起始条件和发送的器件地址和寄存器地址都会重复,但传输方向取反。如果主机接收器发送一个重复起始条件,它之前应该发送了一个不响应信号。(图7)

三、 总结

在本章节我们讲述了IIC的通信协议,并详细介绍了IIC的数据有效性、结束、开始信号、以及应答信号。数据的传输使用7位地址格式。通过本章节应该会对IIC协议有一个大概得了解,后边我们会讲解IIC的读写时序,并通过仿真验证IIC的数据传输流程。

本文章由威三学社出品

对课程感兴趣可以私信联系