最近尝试使用zynq的flash固化功能,我们都知道ZYNQ7000的PL端是可以固化flash到了ZU+就只能通过PS端固化了。

1.design生成就不在赘述了。我们的目的是让PL端的逻辑工作。

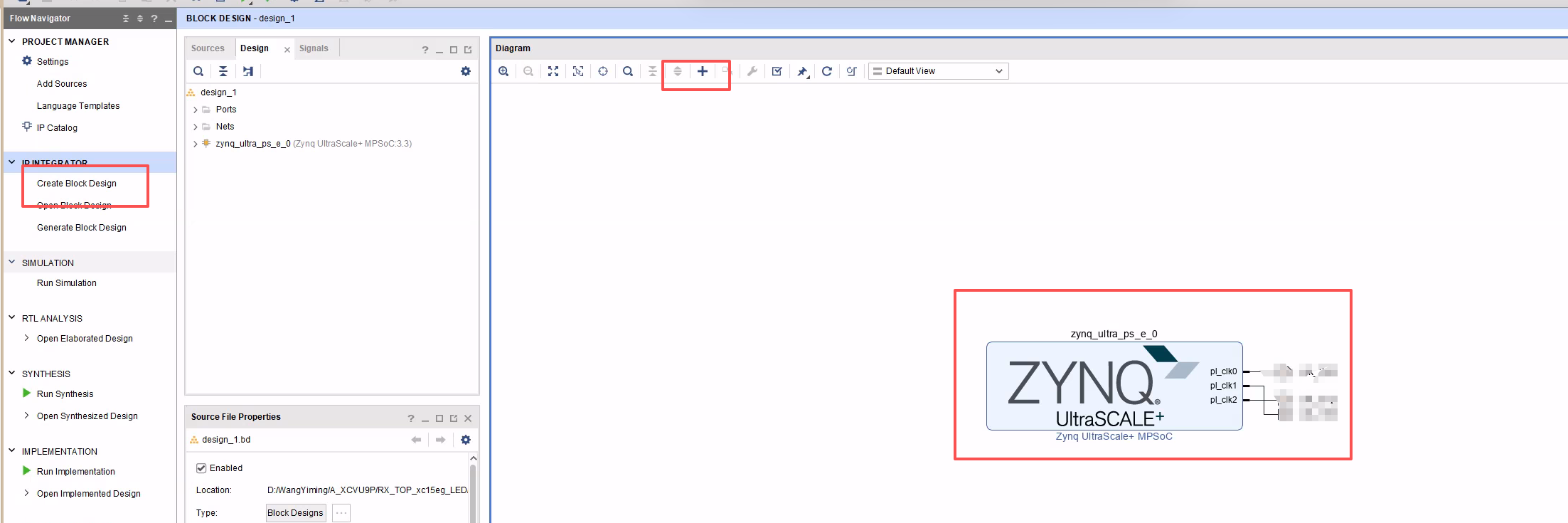

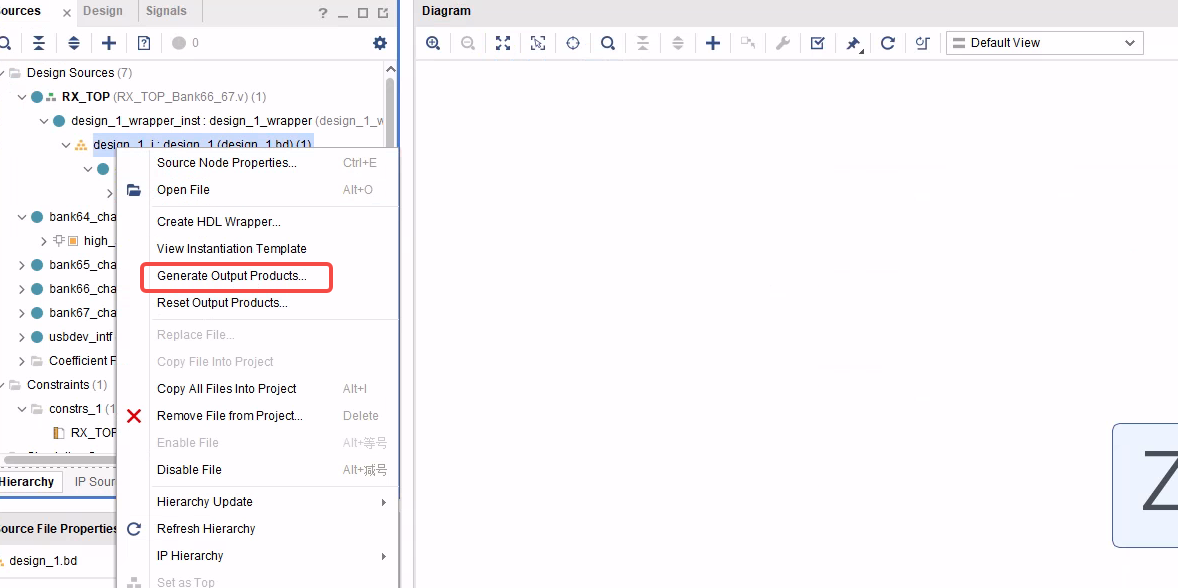

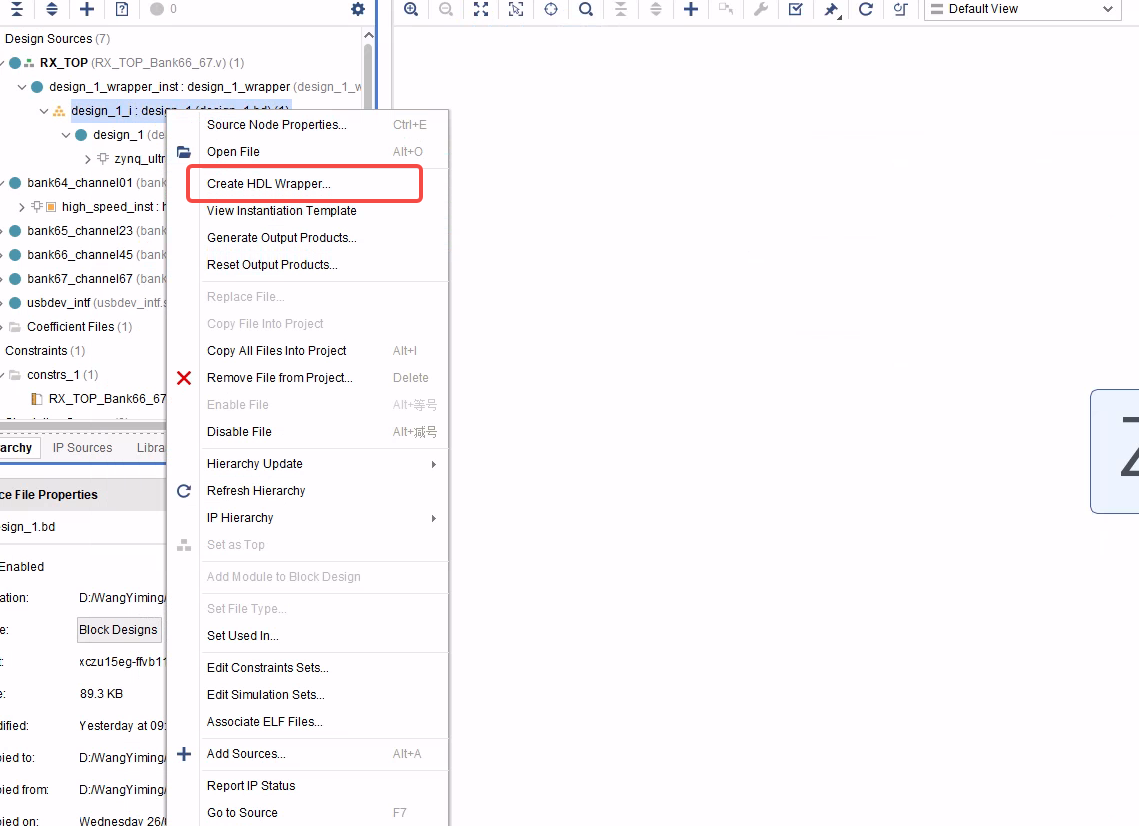

2.生成block-design IP

3.生成例化文件,必须先生成Ip再生成例化

4.将上诉例化到逻辑顶层;

5.生成bit文件;

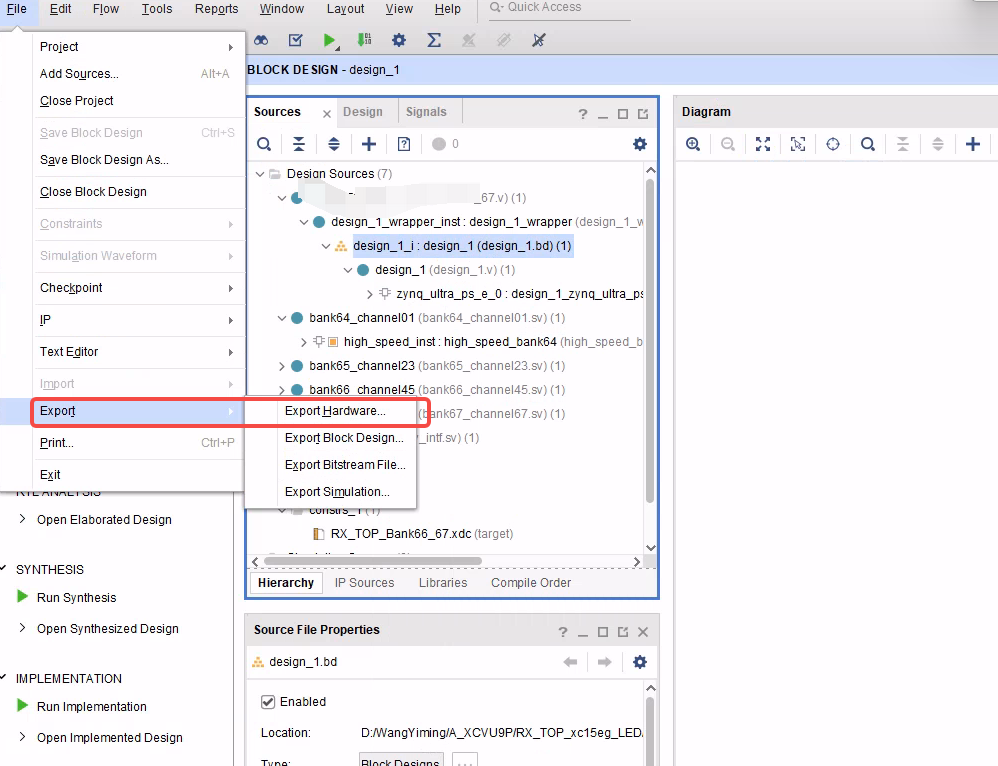

6.Export Hardware

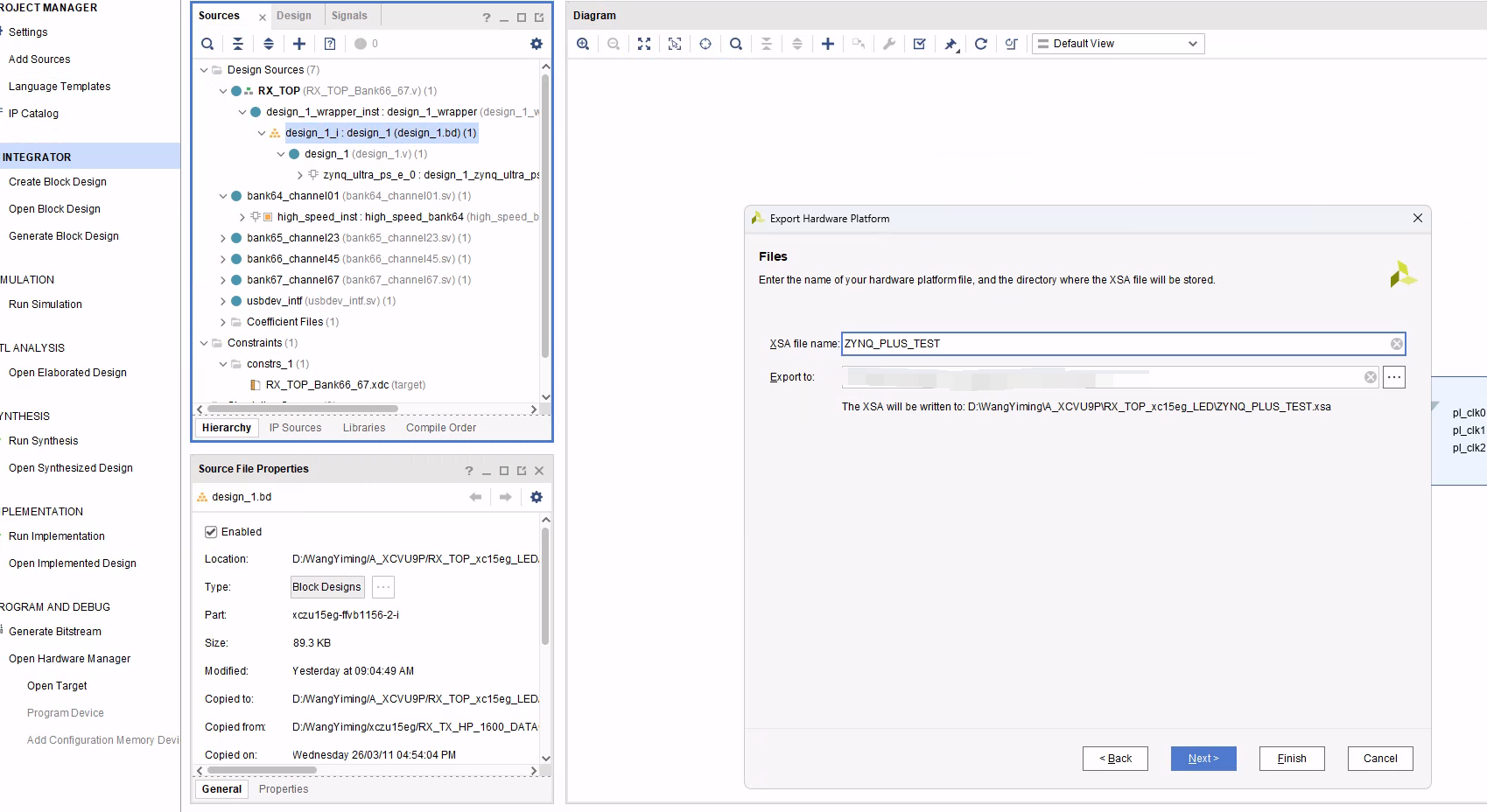

7.命名xsa文件

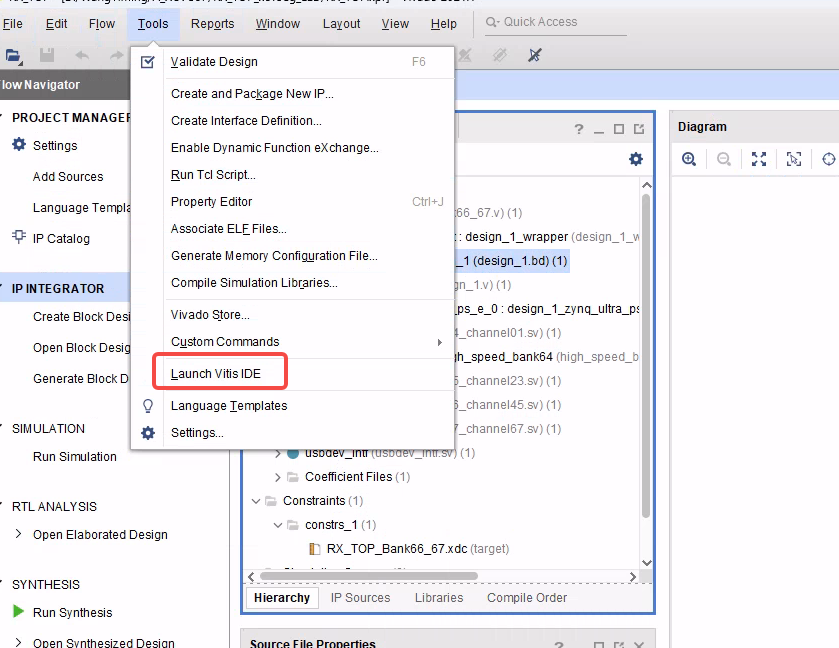

8.launch Vitis IDE

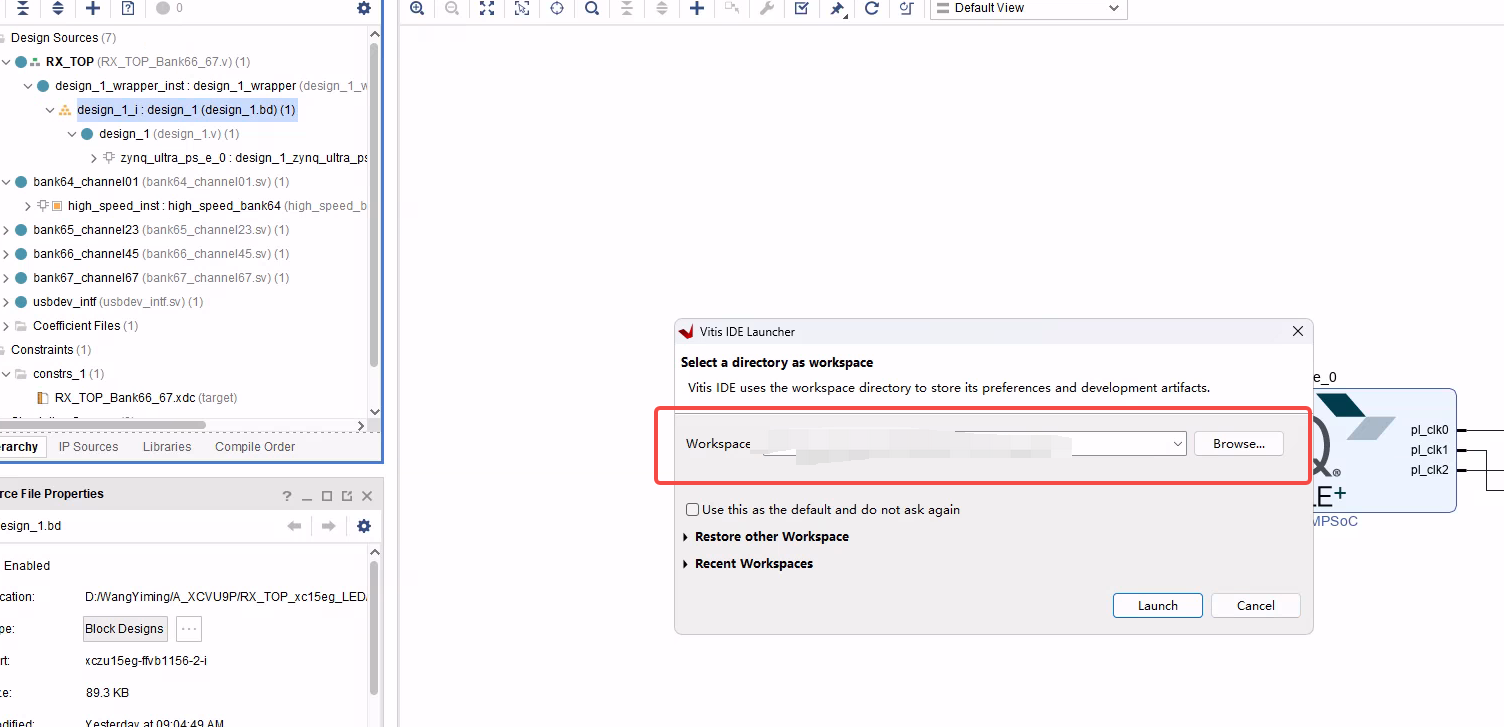

9.选择工程路径(第8步完成自动就会弹出)

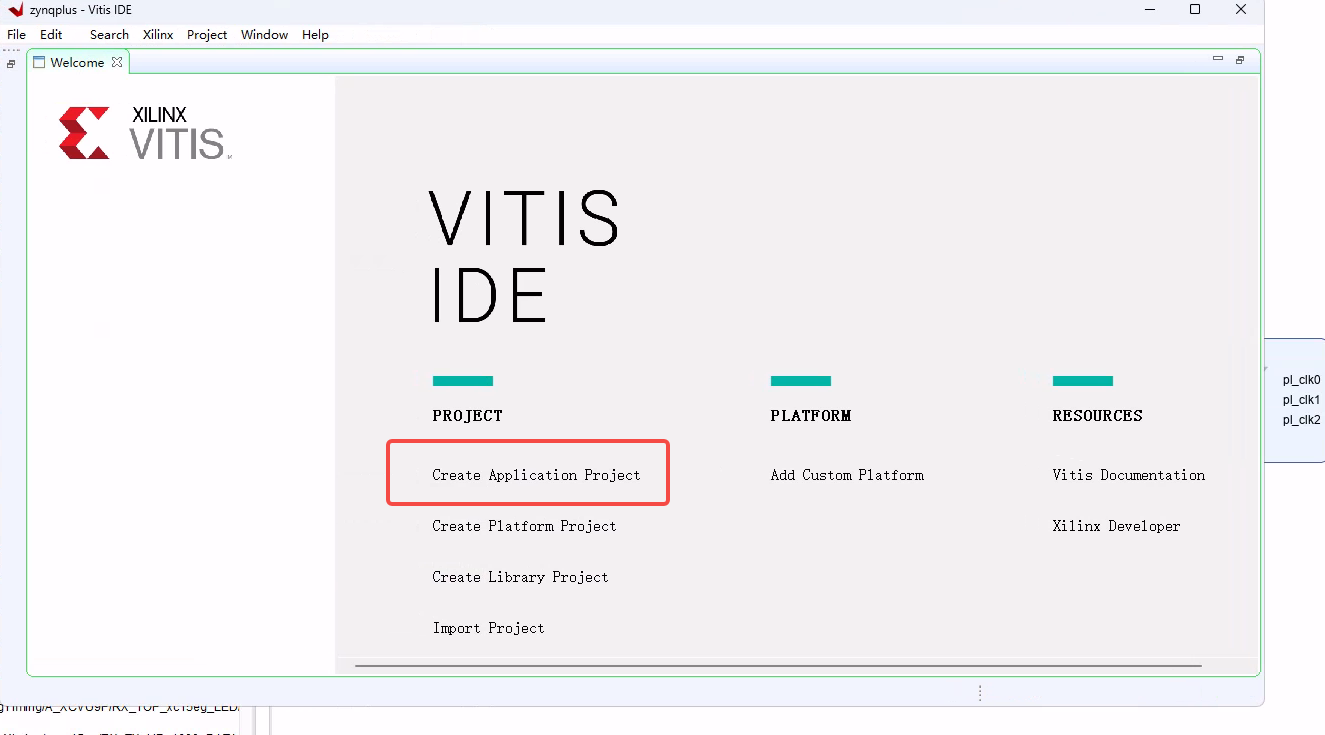

10.选择生成新的App

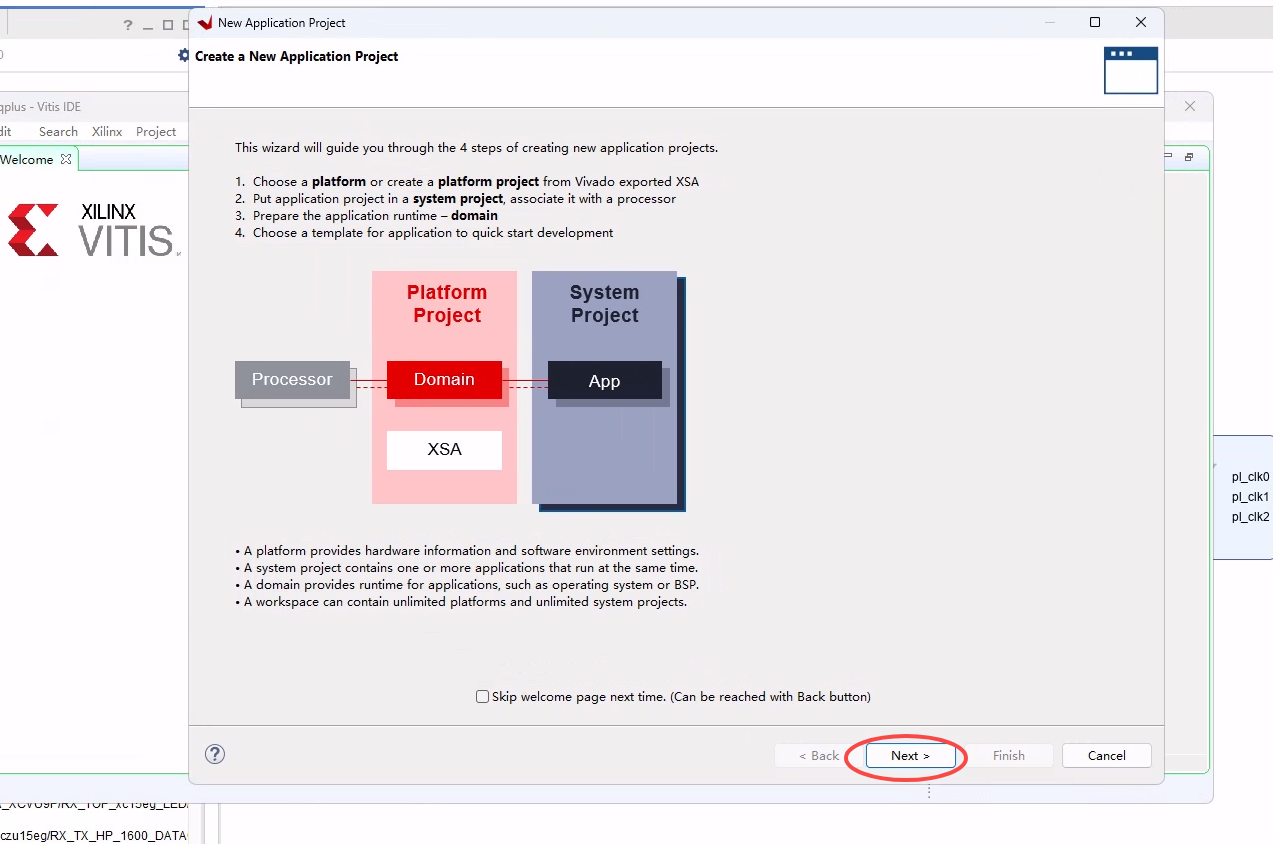

11.自动弹出新界面,选择next就可

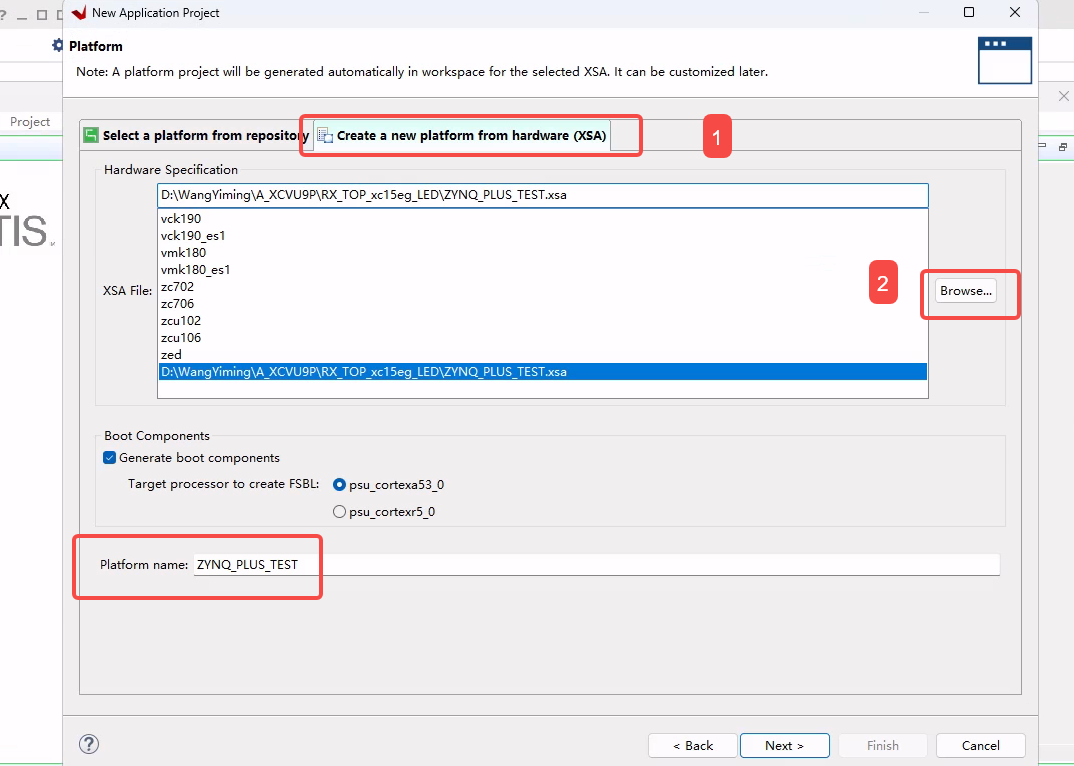

12.选择第7步生成的xsa文件。

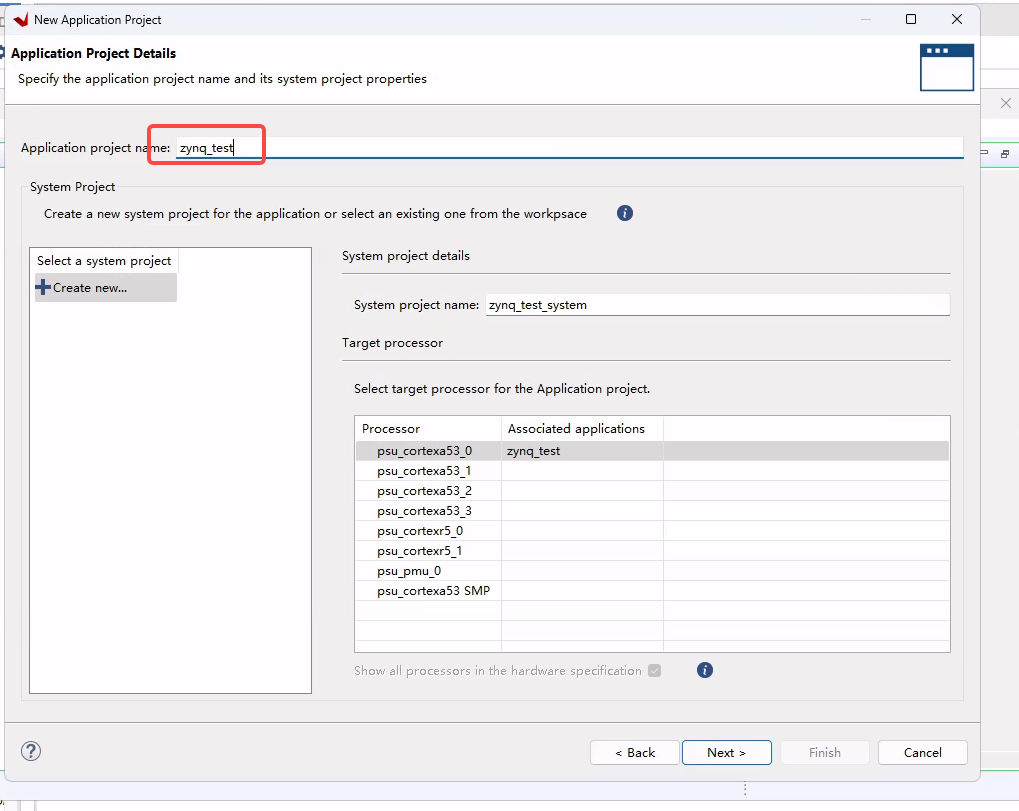

13.给app起个名字

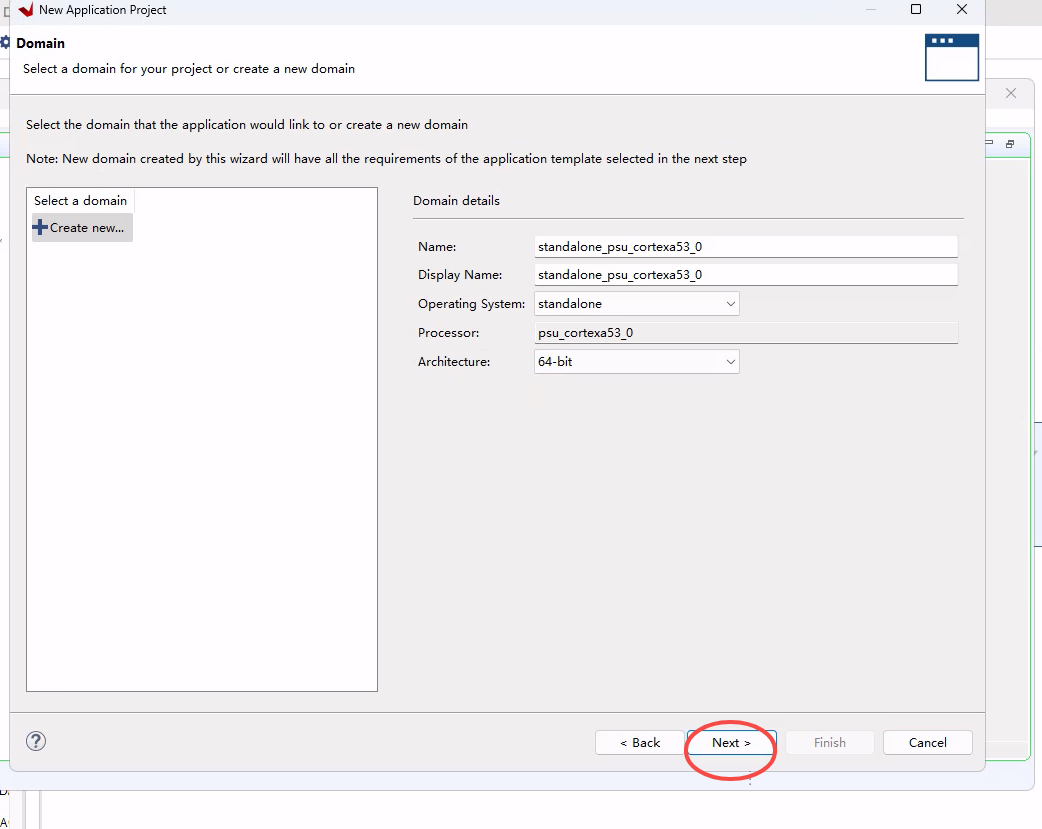

14.弹出点击next

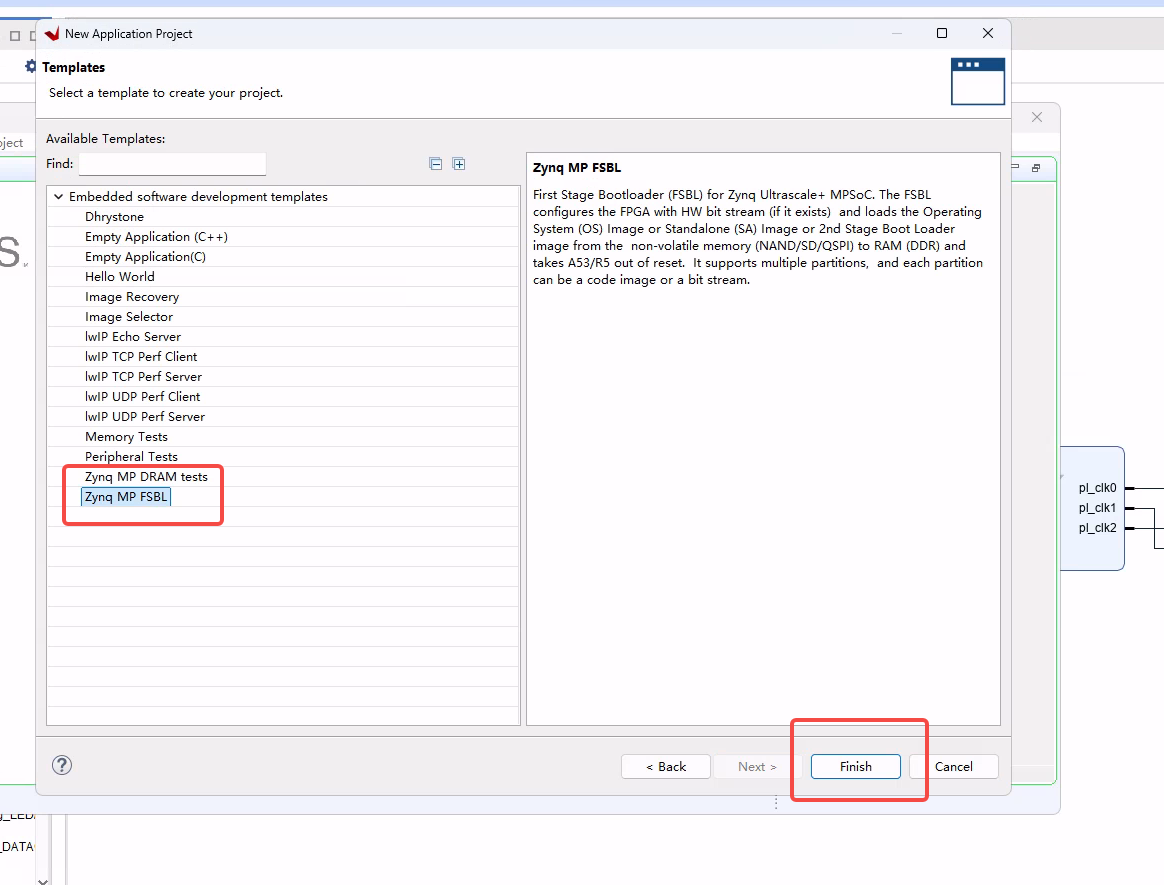

15.选择最小系统FSBL即可,当然选择hello word也行

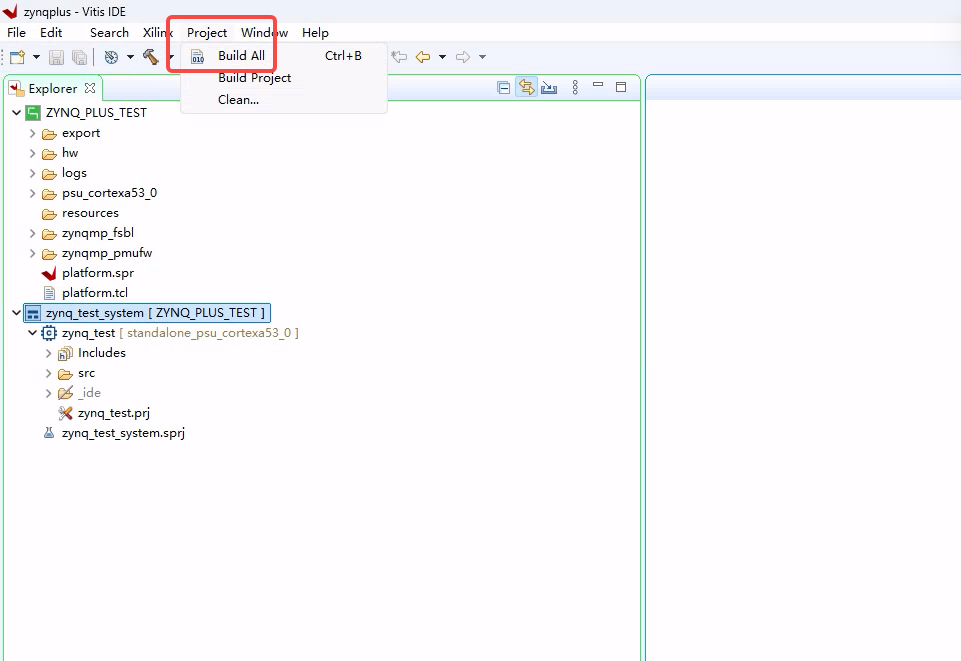

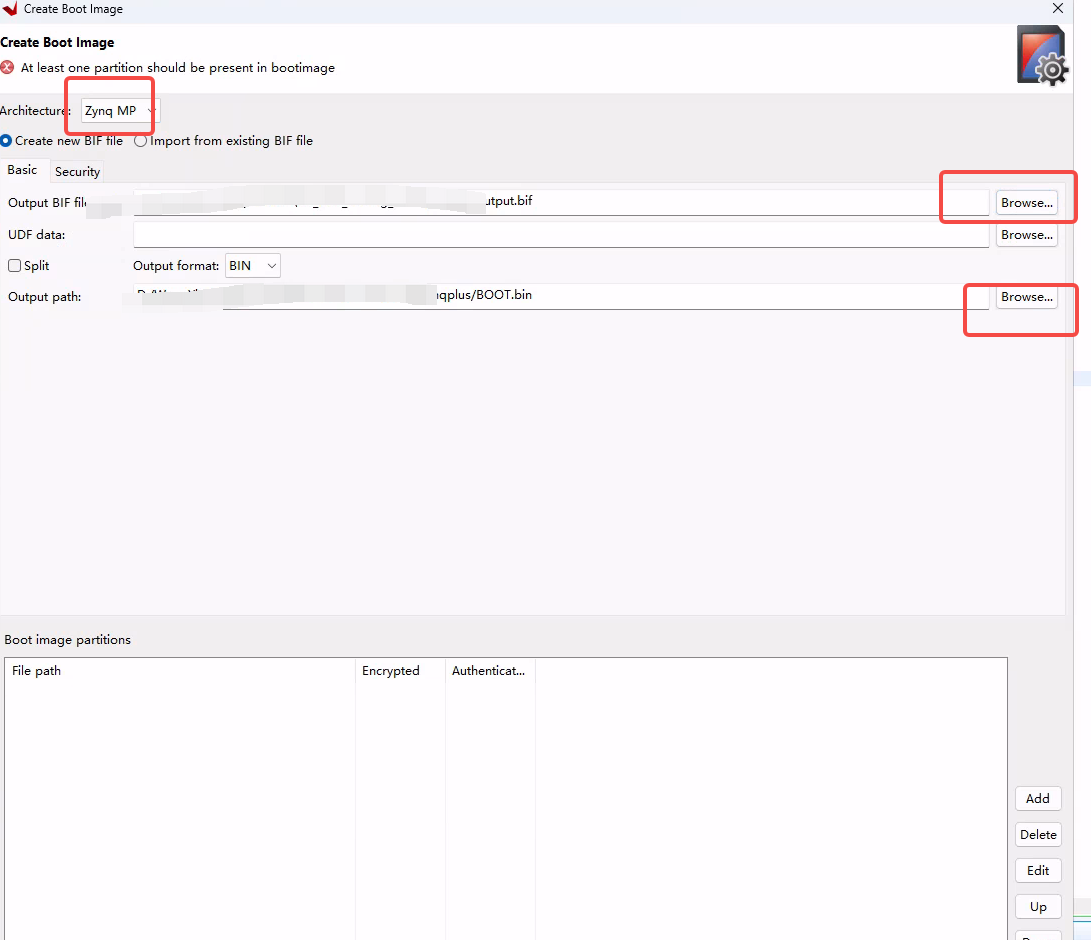

16.进入界面build all

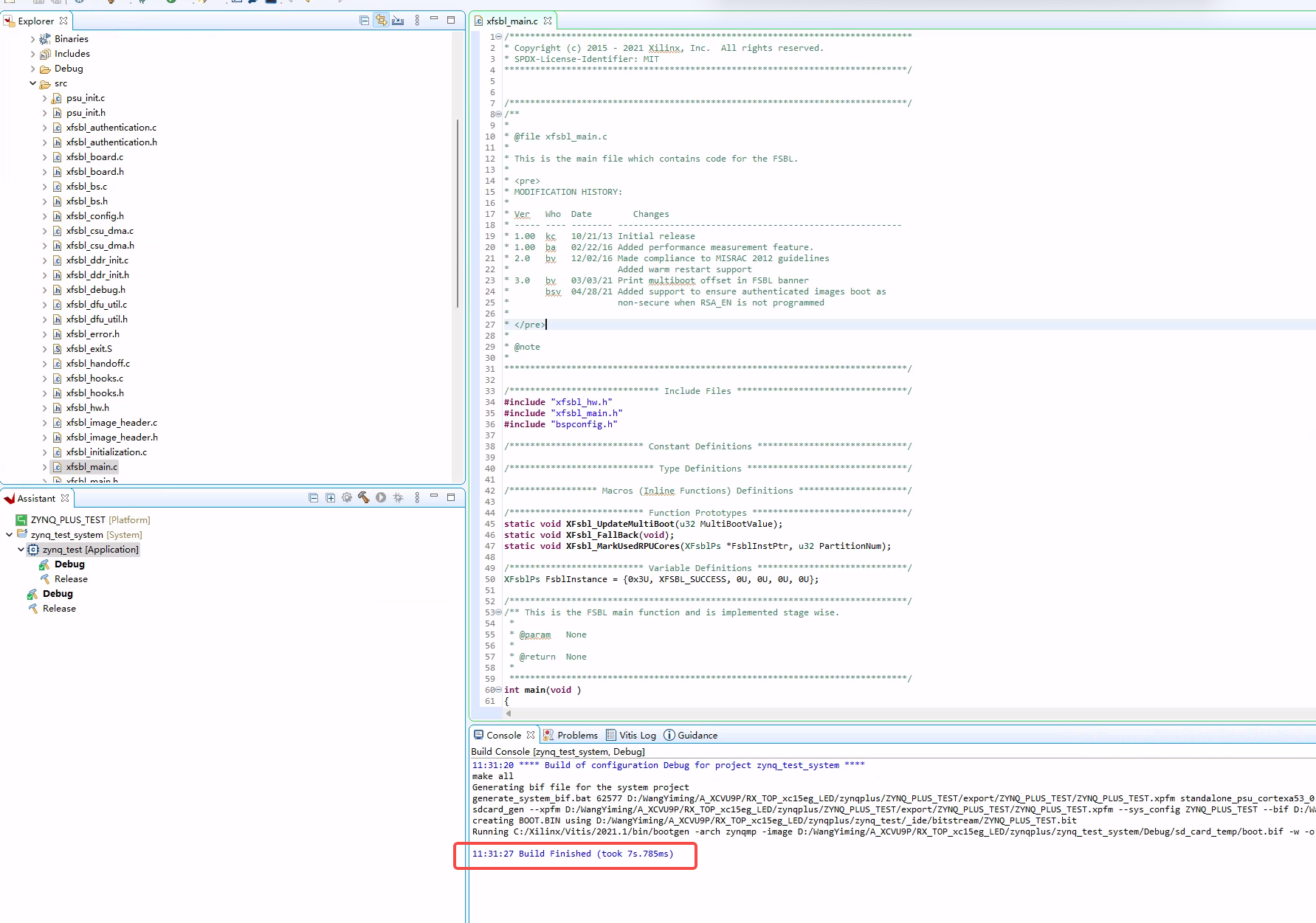

17.build 完成

18.生成boot文件

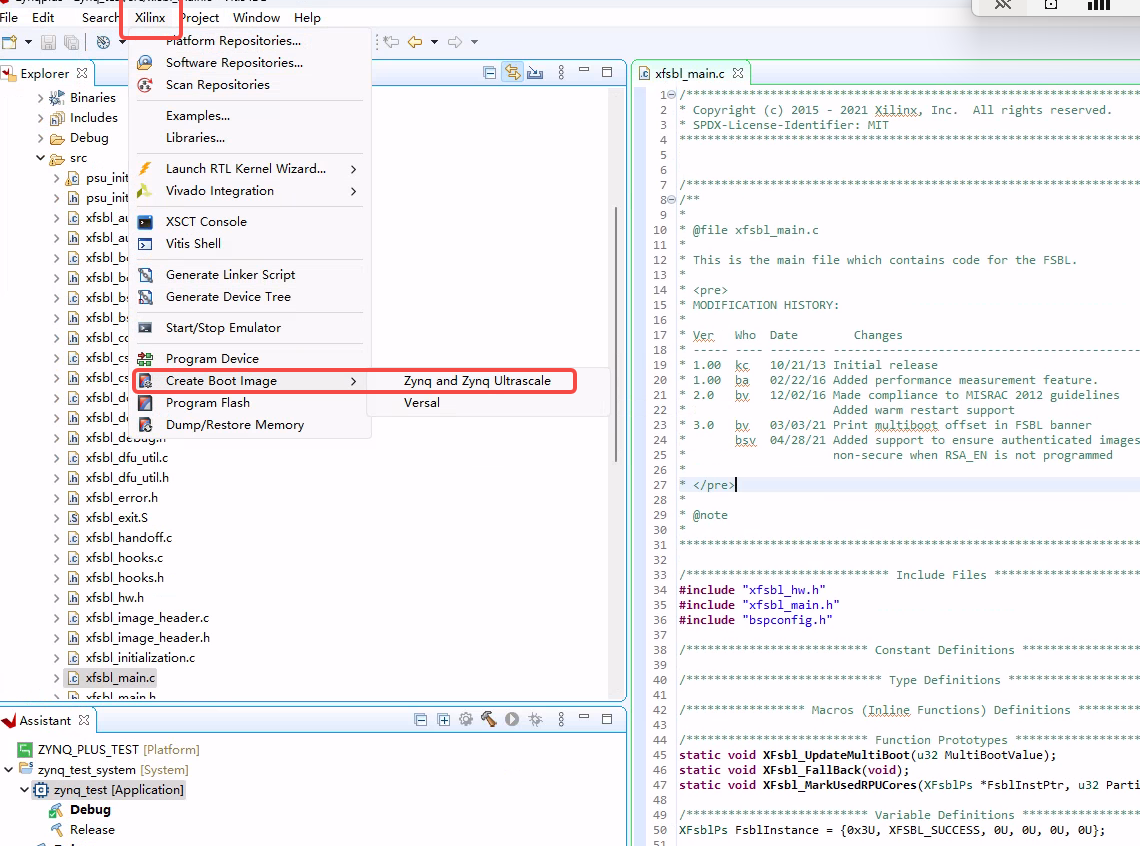

19.输出路径记好,zynqplus要选择ZYNQ-MP

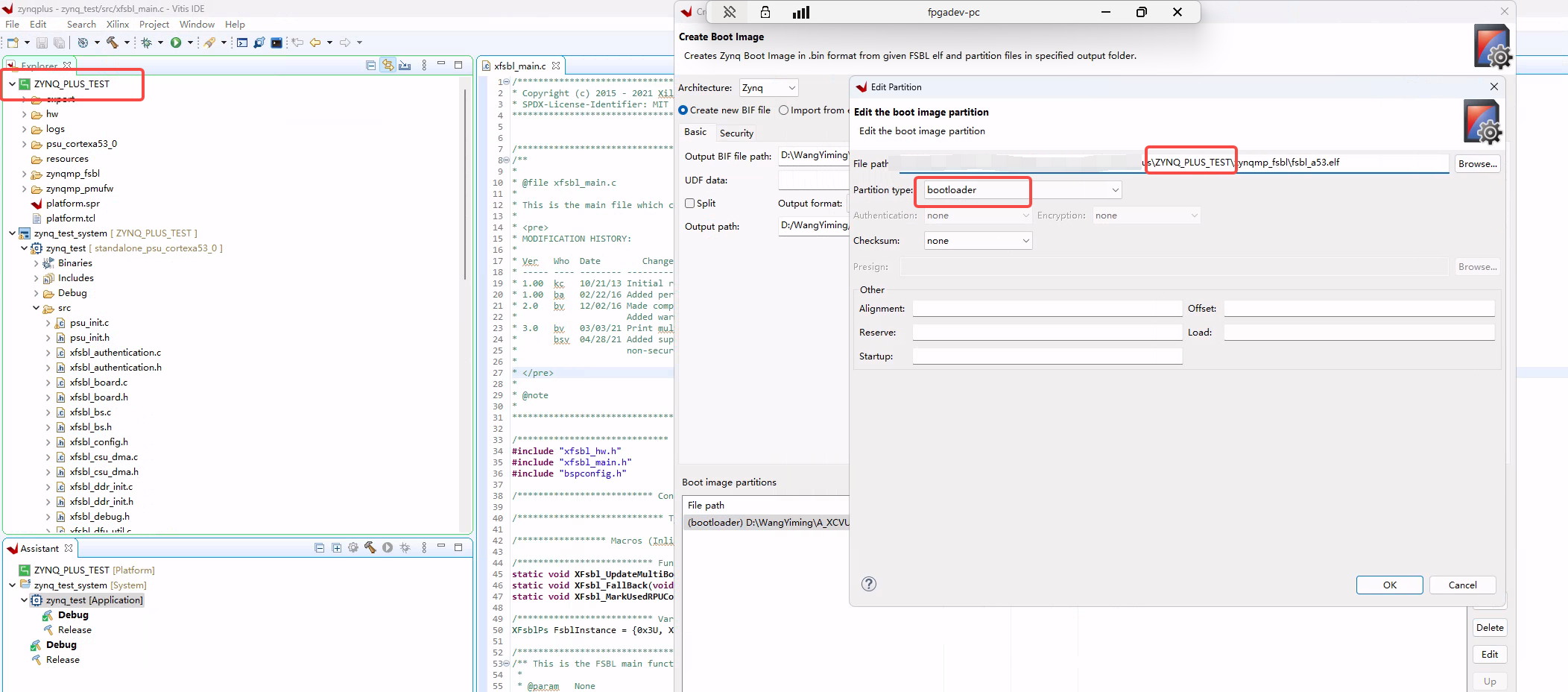

20.增加合成文件(这是最关键的一步,一定要确认好elf文件。一个是平台ZYNQ_PLUS_TEST另一个是app,一定要选择平台下的elf文件,否则启动失败)

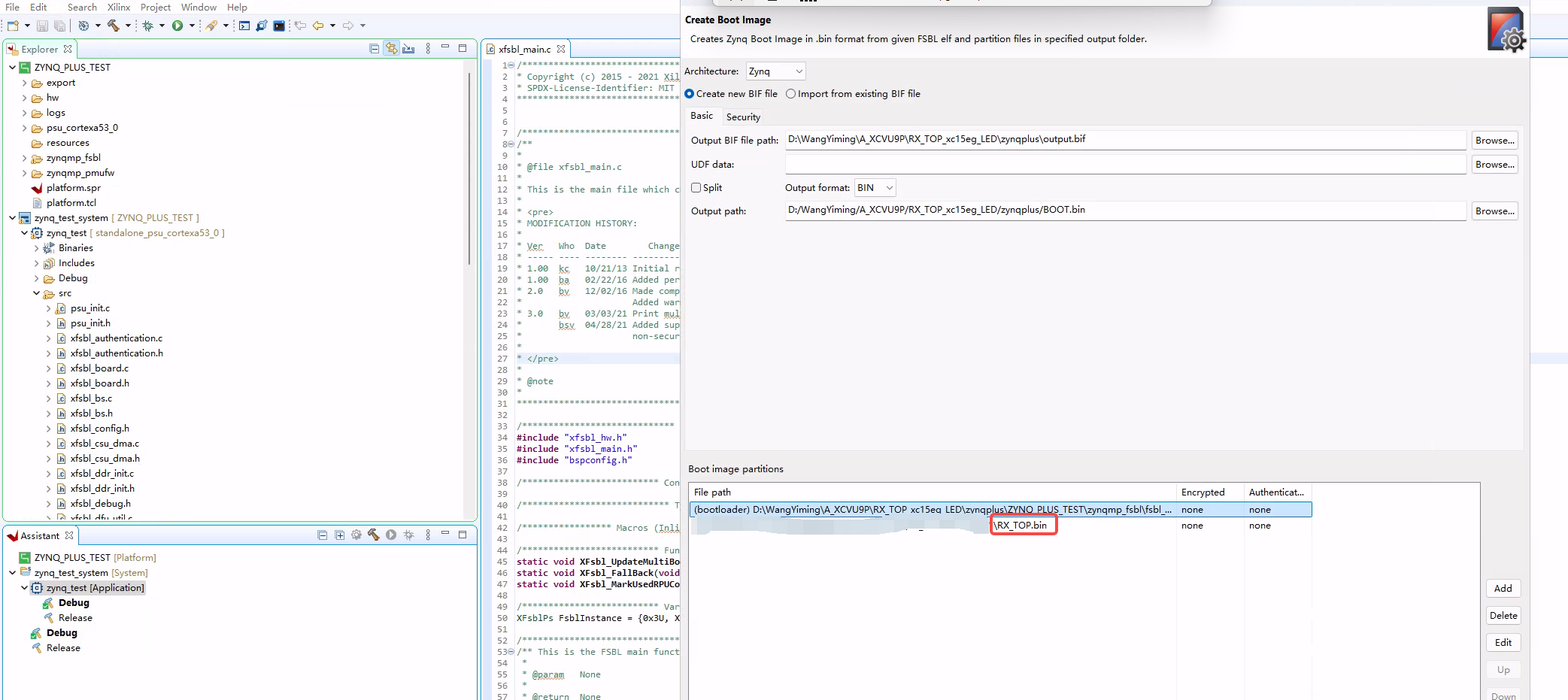

21.增加逻辑生成的bin文件

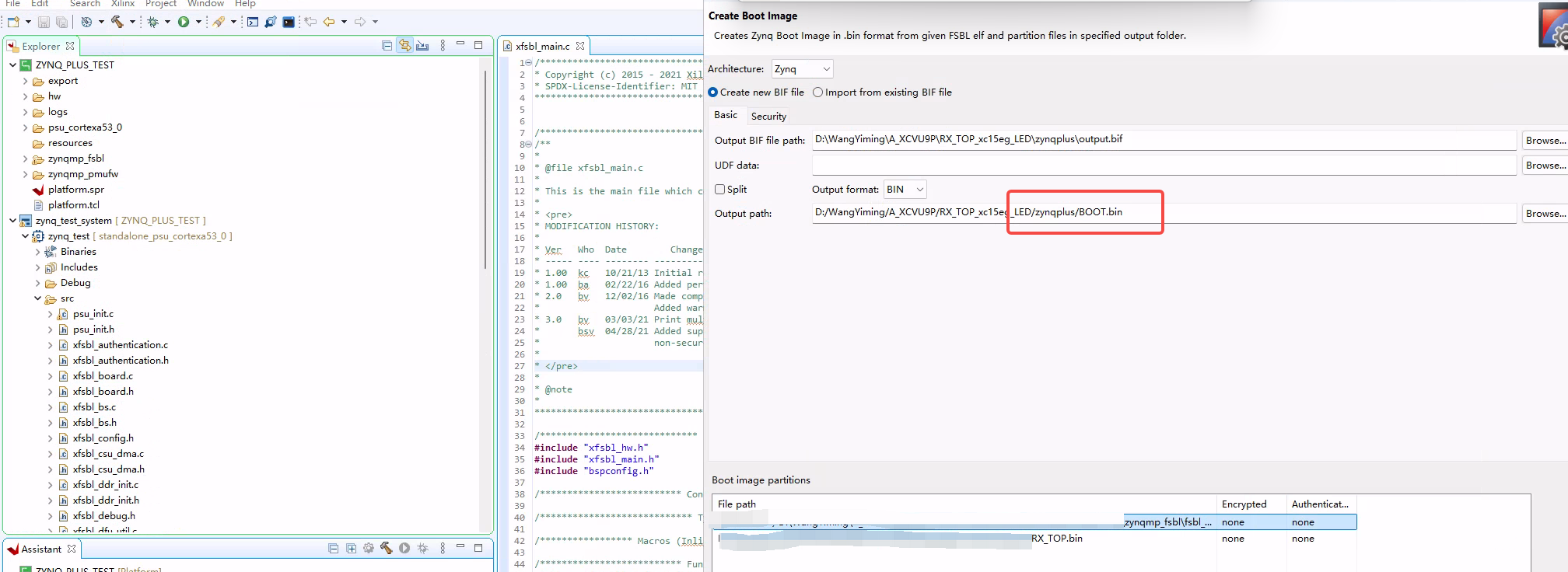

22.确定boot文件的路径

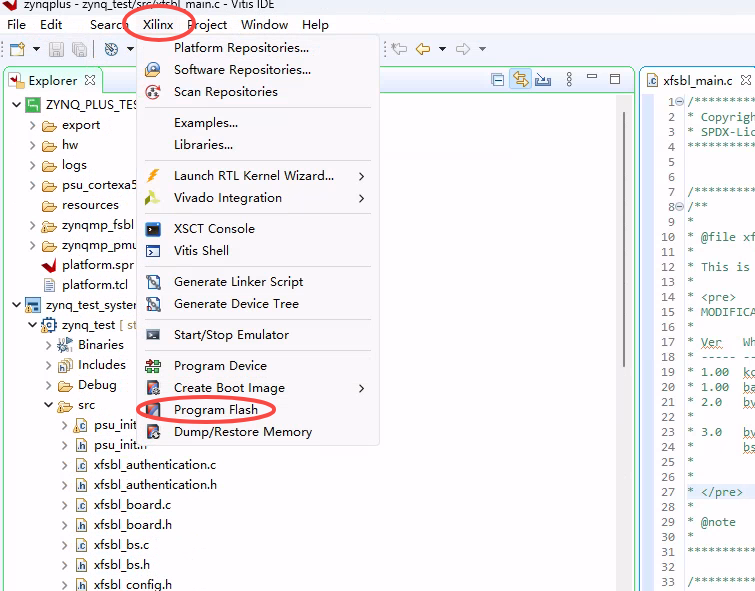

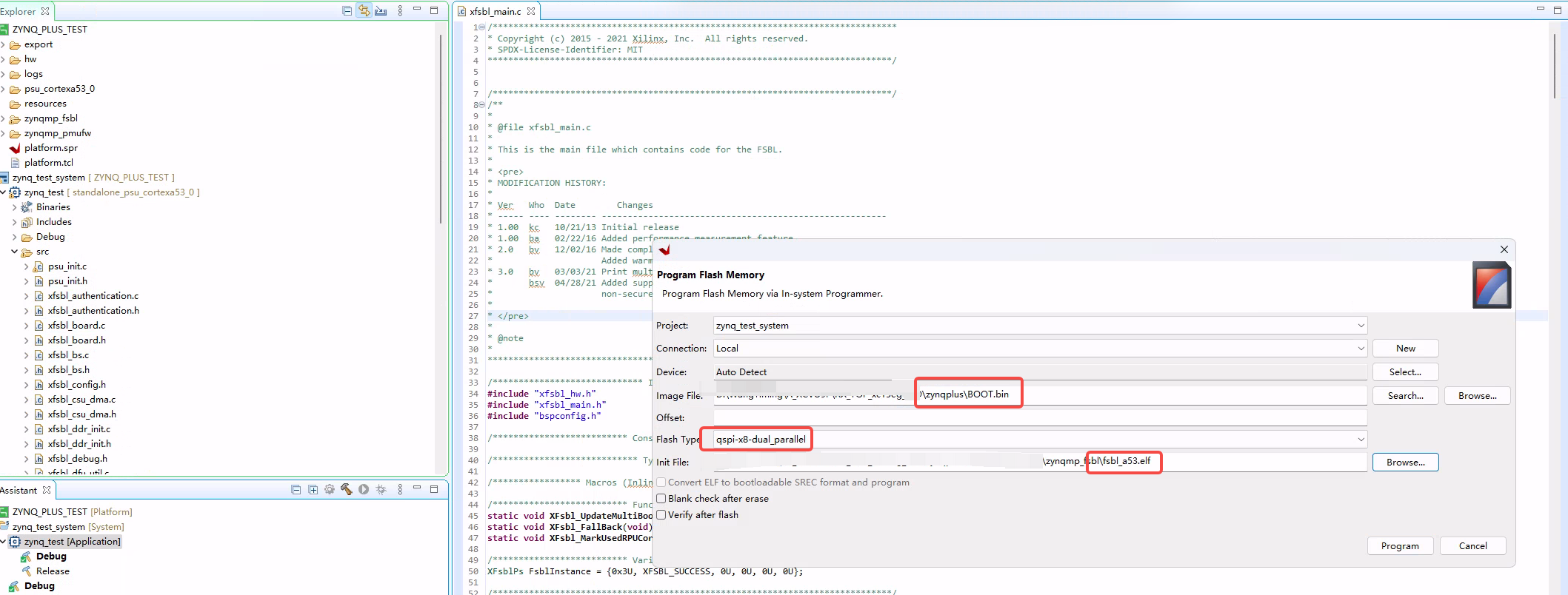

23.开始flash固化

24.固化(boot为刚刚生成的路径,elf文件还是要使用平台的文件),这样固化就成功了

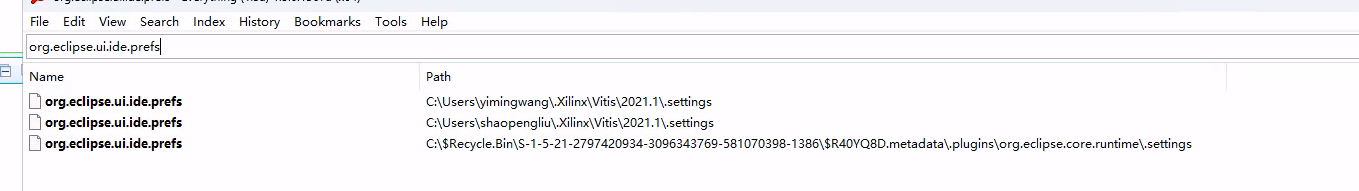

ps:可能遇到的问题1:几次固化失败,vitis启动失败。第一步任务管理器把vitis的软件关掉,

第二步:通过everything找一下这个文件,直接删掉就可以启动了。

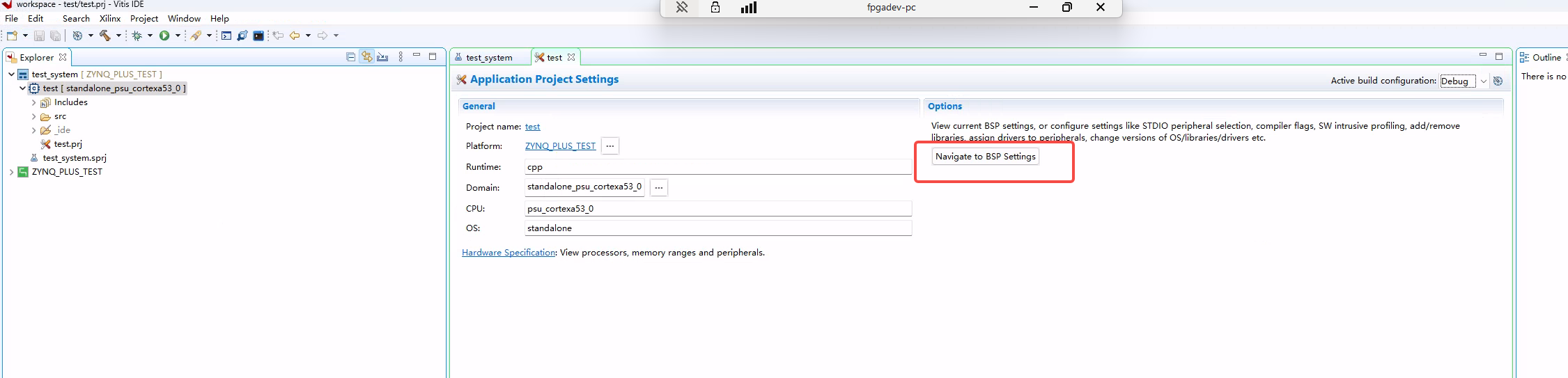

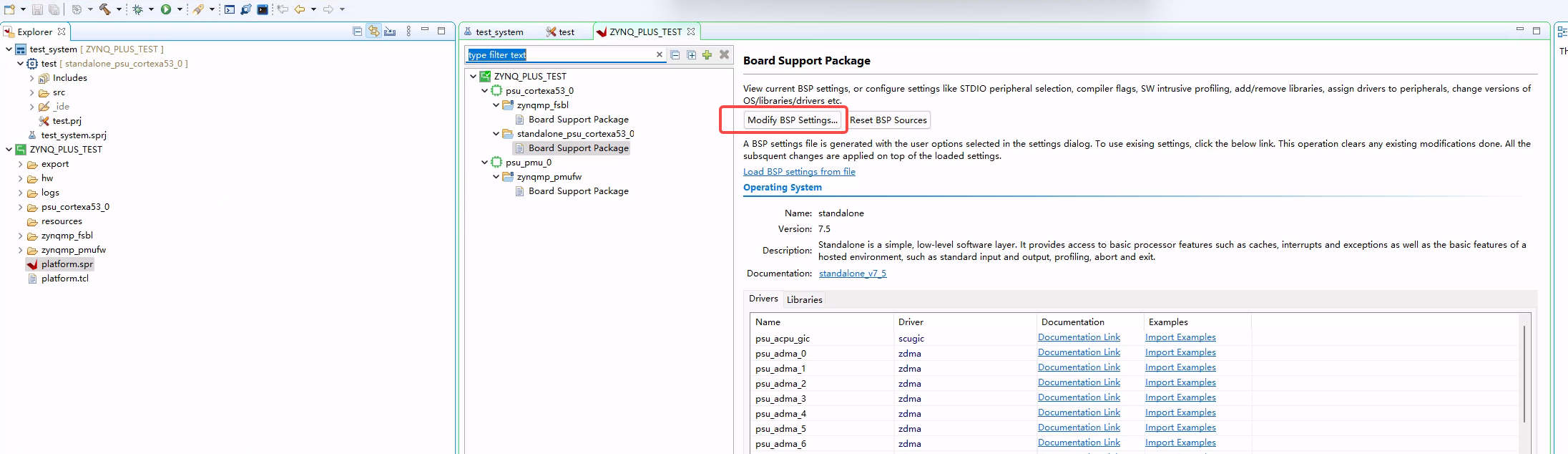

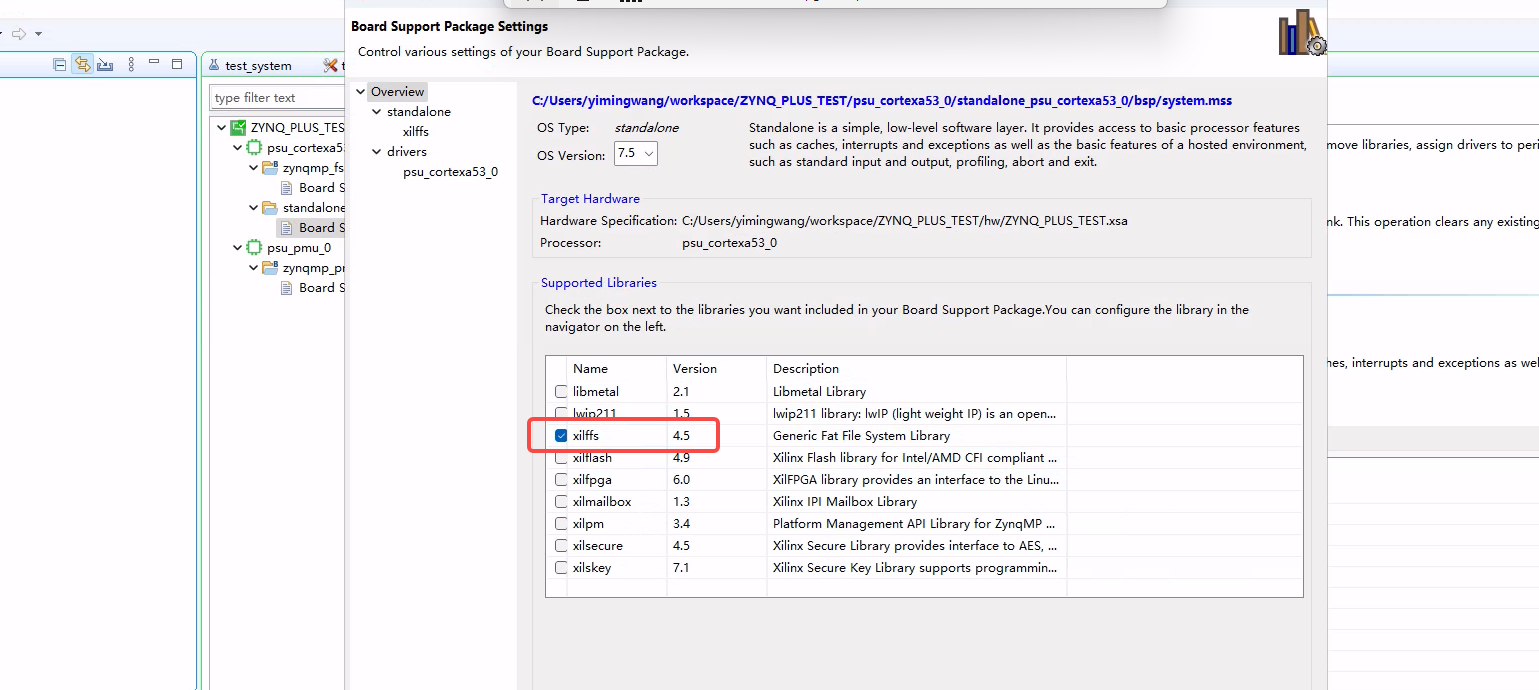

可能遇到的问题2:第15步的时候,最小系统失败。直接取消重新进入vitis;修改一下按照下面三个步骤进入就行。