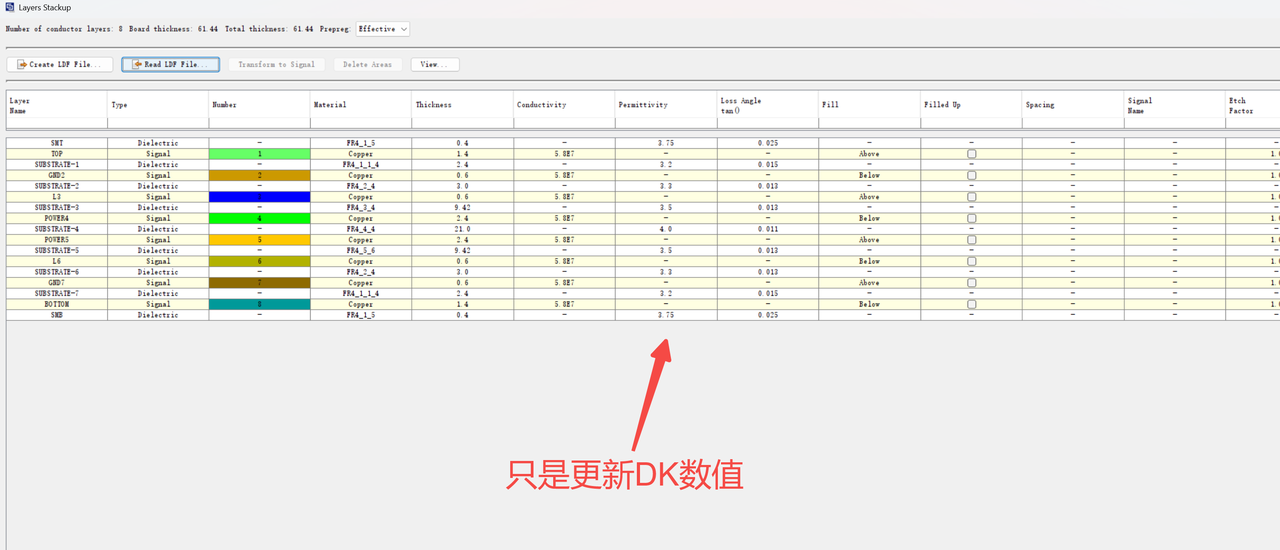

一,导入ODB++数据和层叠设置:其中我们把层叠信息中DK值变更一下,看下它的数值对PDN曲线的影响有多少?

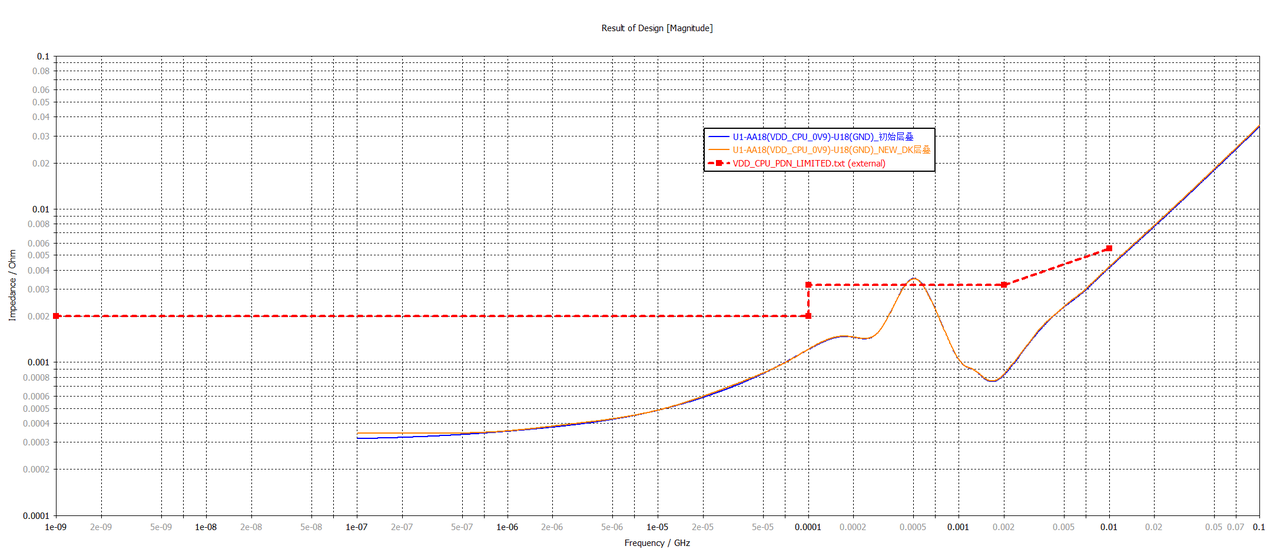

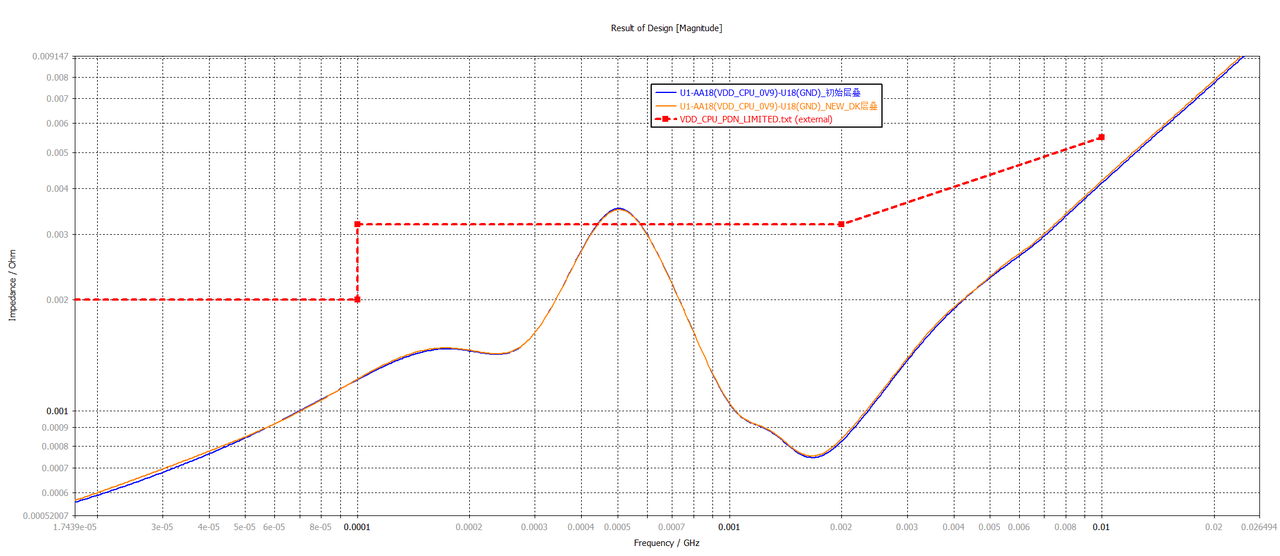

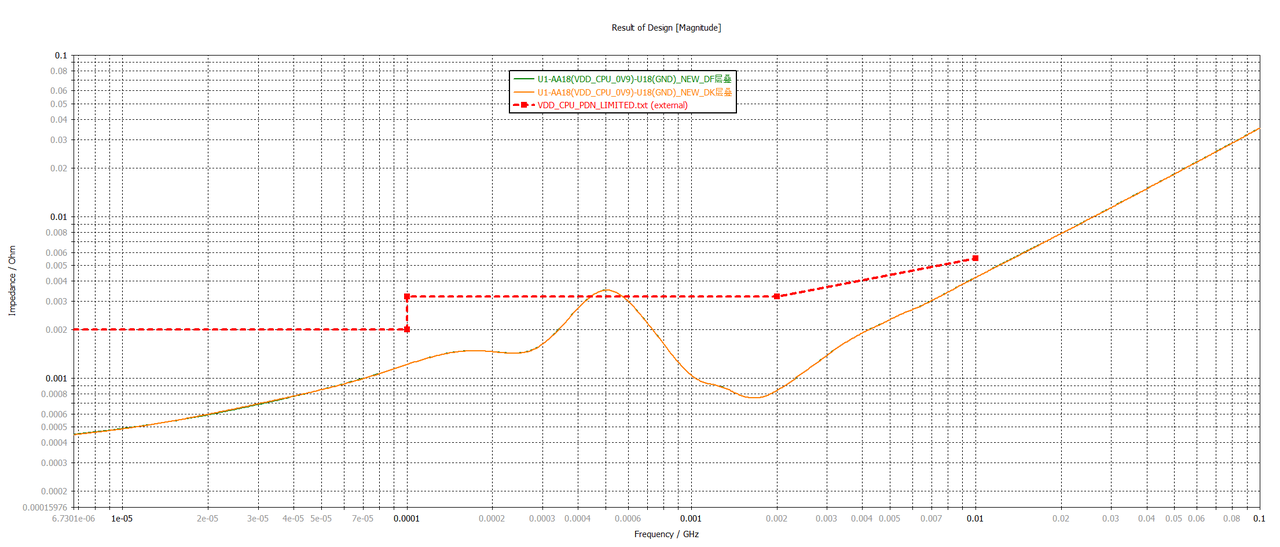

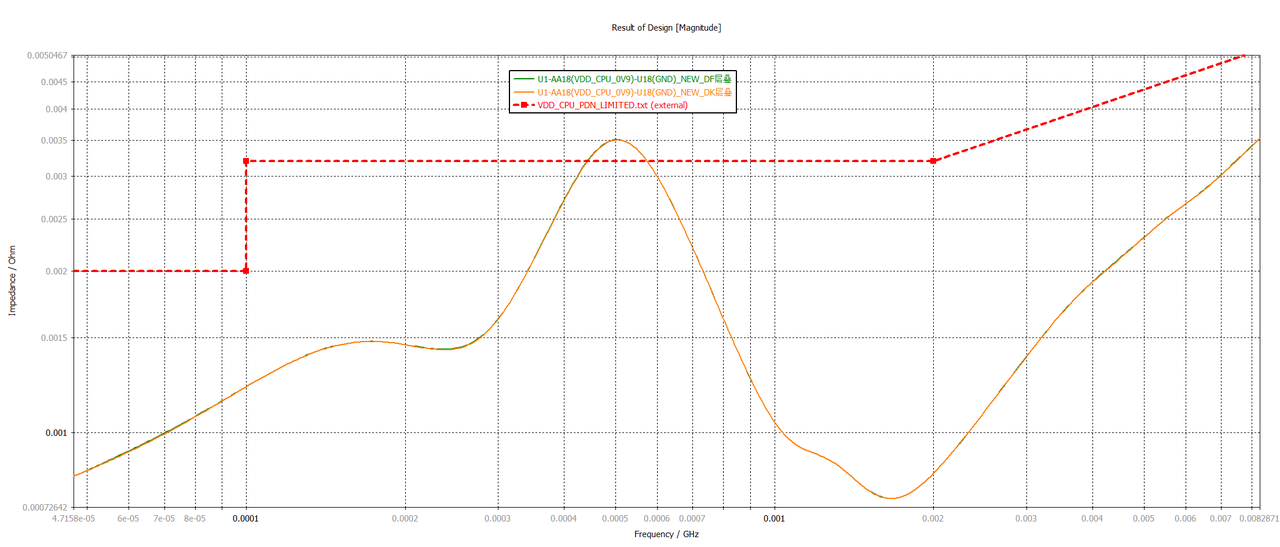

二,仿真结果如下所示:看起给之前的DF值的曲线差不多的。

一、Dk值影响PDN的物理机理

1,Dk是什么?这个小编我之前的文章中也是有讲解过的,不知道诸位道友们是否还有印象啊?

Dk(介电常数)是衡量材料在电场中储存电能能力的参数。它决定了电磁波在介质中的传播速度:Dk越大,信号传播速度越慢,波长越短。

2,Dk在PDN中作用于哪里?

在PDN结构中,Dk主要影响:

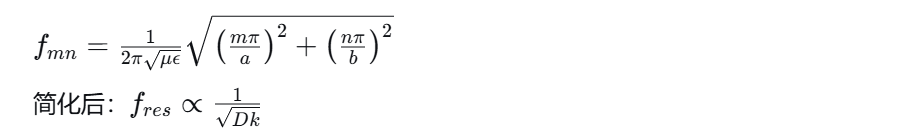

- 电源/地平面对(Power/Ground Plane Pair)的谐振频率: 对于一个尺寸为a×b的矩形电源/地平面对,其谐振频率可近似表示为:

-

这意味着:Dk增大,谐振频率降低;Dk减小,谐振频率升高。

-

传输线的电气长度: Dk决定了PCB上走线和过孔的等效电气长度,影响电源分配网络的相位响应。

-

Dk不影响的部分:

-

直流压降(IR Drop):完全由铜的电导率和几何尺寸决定

-

<10MHz的低频段:PDN阻抗主要由VRM输出阻抗、体电容和PCB走线的DCR主导

二、Dk准确性对PDN曲线的量化影响

1,不同频段的敏感度分析

|----------------|----------------|---------------|--------------------|

| 频段 | 主要影响因素 | Dk影响程度 | 工程意义 |

| DC - 1MHz | VRM、体电容、走线电阻 | 可忽略 (<1%) | Dk误差完全不影响 |

| 1MHz - 10MHz | MLCC电容、PCB寄生电感 | 轻微 (<3-5%) | 电容本身容值主导,平面谐振尚未出现 |

| 10MHz - 100MHz | PCB电源/地平面谐振 | 中度影响 (5-15%) | Dk决定谐振峰出现的频点位置 |

| >100MHz | 高阶平面谐振、封装寄生 | 显著影响 (10-20%) | Dk误差会导致谐振频点偏移几十MHz |

2,对PDN曲线的具体影响形式:

主要会出现两种情况:

场景A:仿真用的Dk偏大(设得比实际大)

-

表现:PDN曲线中的谐振峰整体向低频方向偏移。

-

风险:原本设计在100MHz的去耦方案,实际谐振可能出现在90MHz,导致去耦效率下降。如果偏移量太大,可能错过目标阻抗的峰值。

场景B:仿真用的Dk偏小(设得比实际小)

-

表现:PDN曲线中的谐振峰整体向高频方向偏移。

-

风险:同样会导致去耦电容布局与谐振点错位,可能低估某个频段的阻抗。

三,DK和DF值对PDN的影响:

|------|--------|--------|----------------|

| 参数 | 主要影响 | 表现形式 | 对设计的影响 |

| Dk误差 | 谐振频点位置 | 曲线整体平移 | 可能导致去耦电容与谐振点错位 |

| Df误差 | 谐振峰幅度 | 曲线高低变化 | 可能导致对噪声幅度的误判 |

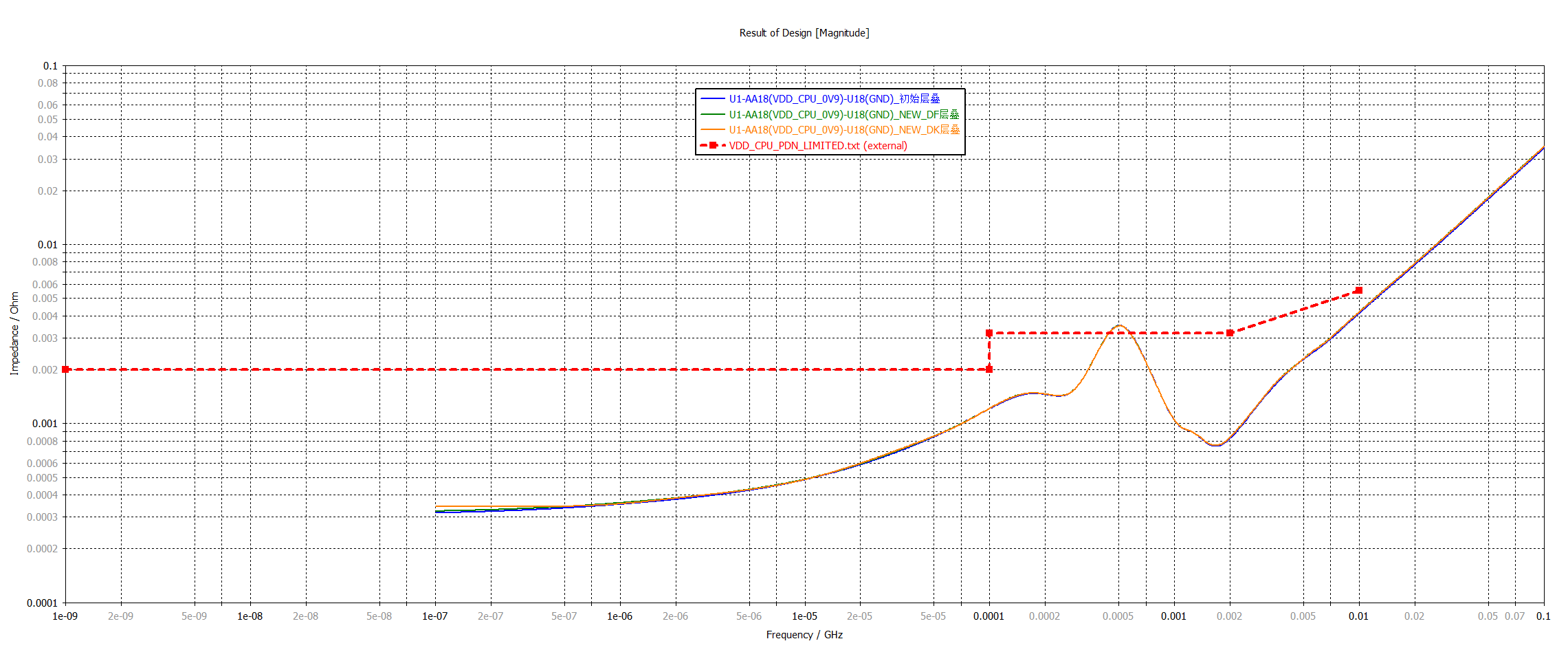

带入实际项目中去分析来看:DK和DF值对PDN的影响整体来看差的不多。

总的仿真结果放在一起看下:

四,最终总结:

所以说前期即使你没有拿到完整的层叠信息资料(DK,DF值不全),也是可以进行初步的电源网络的PDN仿真的,当然了若是想要得到精准的曲线图肯定是需要一份完整的单板的层叠信息的。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!