ubuntu 22.04 x86_64

1. 安装 Chisel 环境

1.1. 安装 java 开发环境

openjdk 可以选择 8,11,17 等三个版本,因为 sbt 倾向于这三个版本。

bash

sudo apt install openjdk-11-jdk git make gtkwave1.2. 安装 sbt

如果是普通用户,命令为:

bash

sudo apt-get update

sudo apt-get install apt-transport-https curl gnupg -yqq

echo "deb https://repo.scala-sbt.org/scalasbt/debian all main" | sudo tee /etc/apt/sources.list.d/sbt.list

echo "deb https://repo.scala-sbt.org/scalasbt/debian /" | sudo tee /etc/apt/sources.list.d/sbt_old.list

curl -sL "https://keyserver.ubuntu.com/pks/lookup?op=get&search=0x2EE0EA64E40A89B84B2DF73499E82A75642AC823" | sudo -H gpg --no-default-keyring --keyring gnupg-ring:/etc/apt/trusted.gpg.d/scalasbt-release.gpg --import

sudo chmod 644 /etc/apt/trusted.gpg.d/scalasbt-release.gpg

sudo apt-get update

sudo apt-get install sbt超级用户 root 的命令需要去掉 sudo:

bash

apt-get update

apt-get install apt-transport-https curl gnupg -yqq

echo "deb https://repo.scala-sbt.org/scalasbt/debian all main" | tee /etc/apt/sources.list.d/sbt.list

echo "deb https://repo.scala-sbt.org/scalasbt/debian /" | tee /etc/apt/sources.list.d/sbt_old.list

curl -sL "https://keyserver.ubuntu.com/pks/lookup?op=get&search=0x2EE0EA64E40A89B84B2DF73499E82A75642AC823" | gpg --no-default-keyring --keyring gnupg-ring:/etc/apt/trusted.gpg.d/scalasbt-release.gpg --import

chmod 644 /etc/apt/trusted.gpg.d/scalasbt-release.gpg

apt-get update

apt-get install sbt来源:

https://www.scala-sbt.org/1.x/docs/Installing-sbt-on-Linux.html1.3. 使用 sbt 运行一个 scala 程序

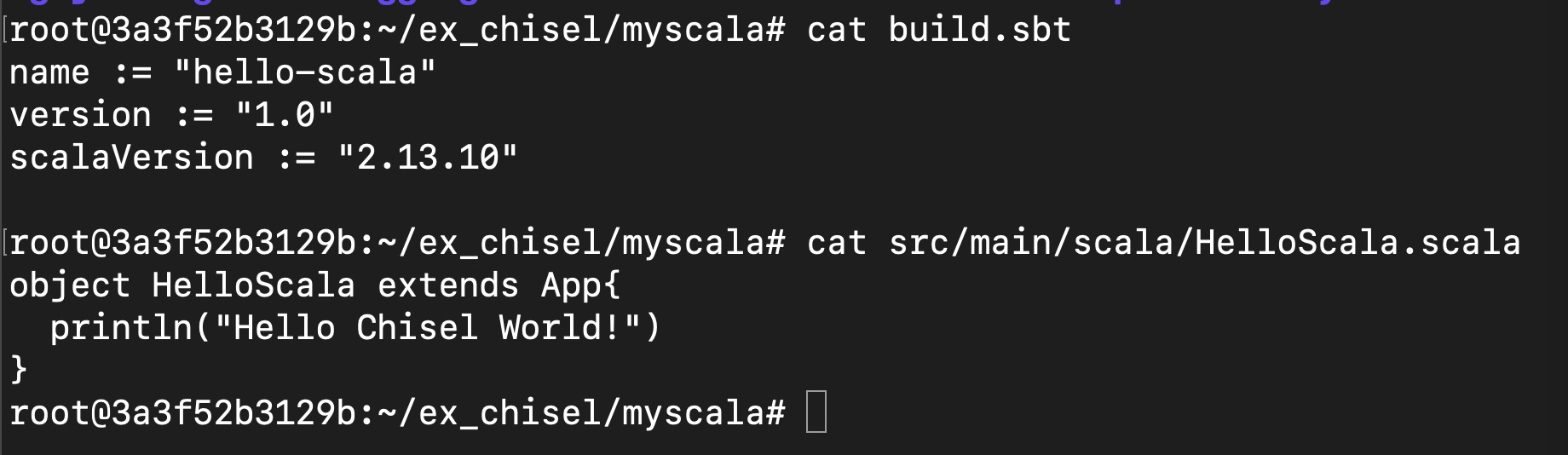

项目最初只存在两个文件:build.sbt 和 scala 源码文件:

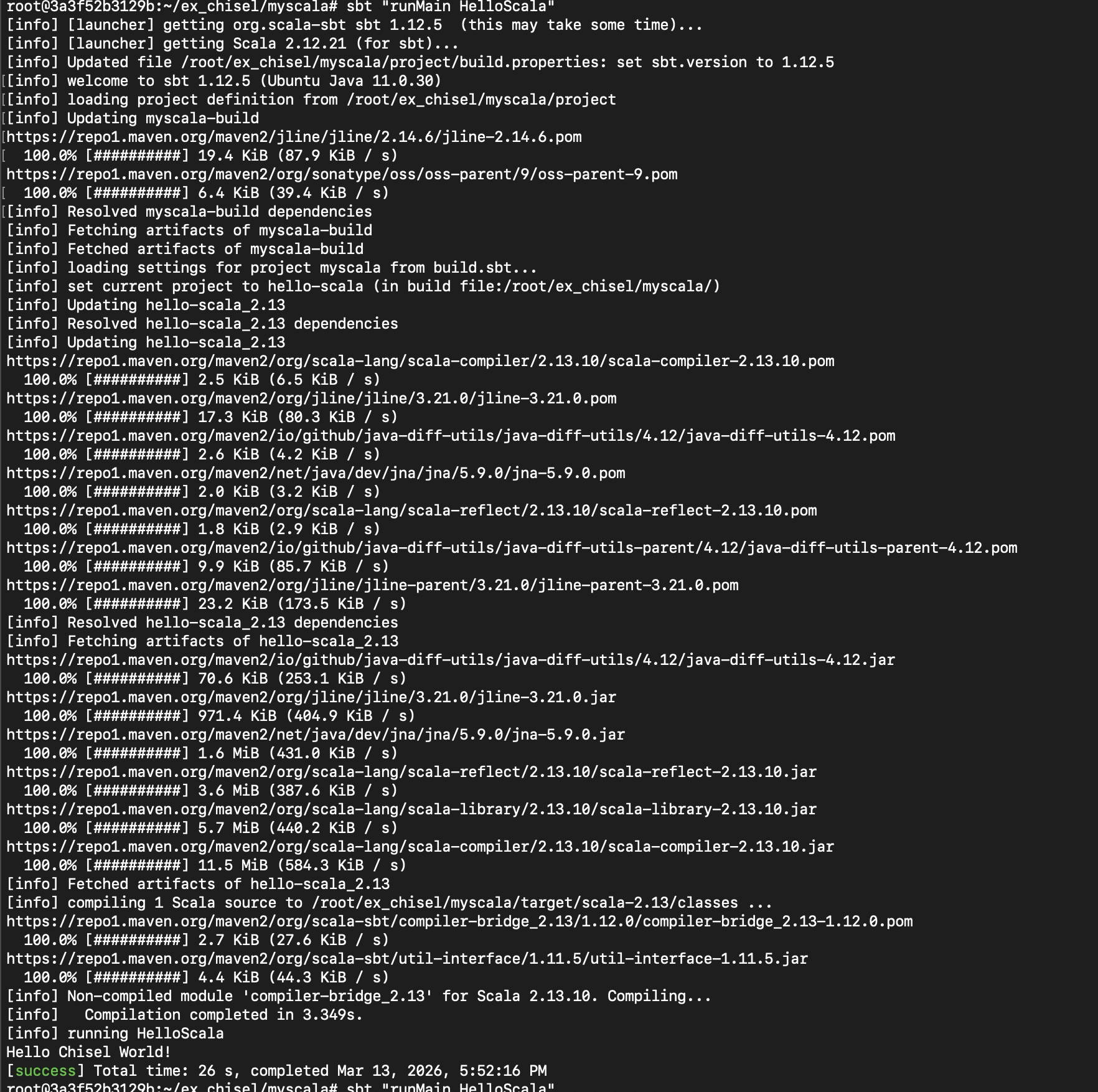

第一次运行的时候会下载一些java/scala 相关的组件:

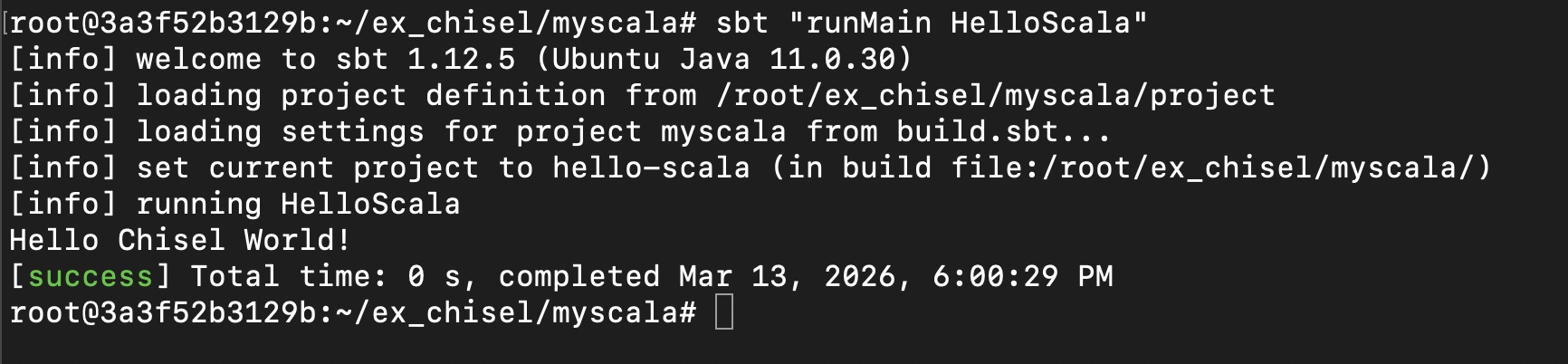

如果组件已经下载过了,那么会如下显示:

2. 实验第一个 chisel 项目

2.1. 生成 verilog 源码

下载项目:

bash

git clone https://github.com/schoeberl/chisel-examples.git编译:

bash

cd chisel-examples/hello-world/

make

lschisel 源文件名为 cat hello-world/src/main/scala/Hello.scala

java

/*

* This code is a minimal hardware described in Chisel.

*

* Blinking LED: the FPGA version of Hello World

*/

import chisel3._

/**

* The blinking LED component.

*/

class Hello extends Module {

val io = IO(new Bundle {

val led = Output(UInt(1.W))

})

val CNT_MAX = (50000000 / 2 - 1).U

val cntReg = RegInit(0.U(32.W))

val blkReg = RegInit(0.U(1.W))

cntReg := cntReg + 1.U

when(cntReg === CNT_MAX) {

cntReg := 0.U

blkReg := ~blkReg

}

io.led := blkReg

}

/**

* An object extending App to generate the Verilog code.

*/

object Hello extends App {

(new chisel3.stage.ChiselStage).emitVerilog(new Hello())

}会得到一个名字为 Hello.v的 verilog 项目:

内容为,

bash

module Hello(

input clock,

input reset,

output io_led

);

`ifdef RANDOMIZE_REG_INIT

reg [31:0] _RAND_0;

reg [31:0] _RAND_1;

`endif // RANDOMIZE_REG_INIT

reg [31:0] cntReg; // @[Hello.scala 19:23]

reg blkReg; // @[Hello.scala 20:23]

wire [31:0] _cntReg_T_1 = cntReg + 32'h1; // @[Hello.scala 22:20]

assign io_led = blkReg; // @[Hello.scala 27:10]

always @(posedge clock) begin

if (reset) begin // @[Hello.scala 19:23]

cntReg <= 32'h0; // @[Hello.scala 19:23]

end else if (cntReg == 32'h17d783f) begin // @[Hello.scala 23:28]

cntReg <= 32'h0; // @[Hello.scala 24:12]

end else begin

cntReg <= _cntReg_T_1; // @[Hello.scala 22:10]

end

if (reset) begin // @[Hello.scala 20:23]

blkReg <= 1'h0; // @[Hello.scala 20:23]

end else if (cntReg == 32'h17d783f) begin // @[Hello.scala 23:28]

blkReg <= ~blkReg; // @[Hello.scala 25:12]

end

end

// Register and memory initialization

`ifdef RANDOMIZE_GARBAGE_ASSIGN

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_INVALID_ASSIGN

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_REG_INIT

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_MEM_INIT

`define RANDOMIZE

`endif

`ifndef RANDOM

`define RANDOM $random

`endif

`ifdef RANDOMIZE_MEM_INIT

integer initvar;

`endif

`ifndef SYNTHESIS

`ifdef FIRRTL_BEFORE_INITIAL

`FIRRTL_BEFORE_INITIAL

`endif

initial begin

`ifdef RANDOMIZE

`ifdef INIT_RANDOM

`INIT_RANDOM

`endif

`ifndef VERILATOR

`ifdef RANDOMIZE_DELAY

#`RANDOMIZE_DELAY begin end

`else

#0.002 begin end

`endif

`endif

`ifdef RANDOMIZE_REG_INIT

_RAND_0 = {1{`RANDOM}};

cntReg = _RAND_0[31:0];

_RAND_1 = {1{`RANDOM}};

blkReg = _RAND_1[0:0];

`endif // RANDOMIZE_REG_INIT

`endif // RANDOMIZE

end // initial

`ifdef FIRRTL_AFTER_INITIAL

`FIRRTL_AFTER_INITIAL

`endif

`endif // SYNTHESIS

endmodule2.2. 加载进 FPGA 开发板

。。。