概念

关于差分信号,简单的说就是两根线同时传输信号,振幅相等,极性相反。

优点

1、抗干扰能力强。一般的噪声干扰施加到差分信号上,由于两根线的噪声基本一致,差值仍不变,不会影响到逻辑信号。

2、可以有效抑制电磁干扰EMI。两根线相距较近,极性相反,电磁场互相抵消,对周围的电磁干扰也很小。

布线要求

1、等长,等长的目的是为了保证在终端时信号的极性相反,减少共模分量。

差分信号是用一对互补、等幅反相 的信号传输信息,靠电压差 判断逻辑,核心优势是强抗共模干扰、低 EMI、高速稳定,是高速 / 高可靠传输的主流方案。

一、核心定义与原理

- 定义:用两根线(D+、D-)传输一个信号,D + 为原始信号,D - 为其反相(180° 相位差),振幅严格相等。

- 判断逻辑 :接收端不取单端对地电压,只看Vdiff = V(D+) − V(D−) :

- 逻辑 1:Vdiff > 0(如 D+=+2.5V,D−=−2.5V → Vdiff=+5V)

- 逻辑 0:Vdiff < 0(如 D+=−2.5V,D−=+2.5V → Vdiff=−5V)

- 抗干扰原理(共模抑制) :外界噪声 / 串扰会同时、同等 叠加在两根线上(共模噪声),相减后被抵消;有效信号因反相,差值被加倍放大。

二、关键参数

- 差模电压(Vdiff):两根线的电压差,承载有效信号(如 LVDS:±350mV)。

- 共模电压(VCM):两根线电压的平均值(VCM = (V (D+)+V (D−))/2),决定直流偏置(如 LVDS:1.2V)。

- 共模抑制比(CMRR):衡量差分放大器抑制共模噪声的能力,单位 dB,值越大抗干扰越强。

三、核心优势

- 超强抗共模干扰:外部 EMI、地弹、电源噪声等被大幅抑制,适合恶劣电磁环境。

- 低 EMI 辐射:两根线电流反向,磁场相互抵消,对外辐射远小于单端信号。

- 高速能力:差模摆幅小(数百 mV),压摆率要求低,可实现更高频率与带宽。

- 信号完整性好:减少对参考地的依赖,降低地弹与串扰影响,时序更稳定。

- 功耗更低:小摆幅 + 低阻抗,驱动功耗显著降低。

四、主要缺点

- 布线成本高:一个信号需两根线,占用更多 PCB 面积与引脚资源。

- 设计约束严 :差分对必须等长、等宽、紧密耦合、同层、阻抗匹配,否则会破坏差分特性、引入差模噪声。

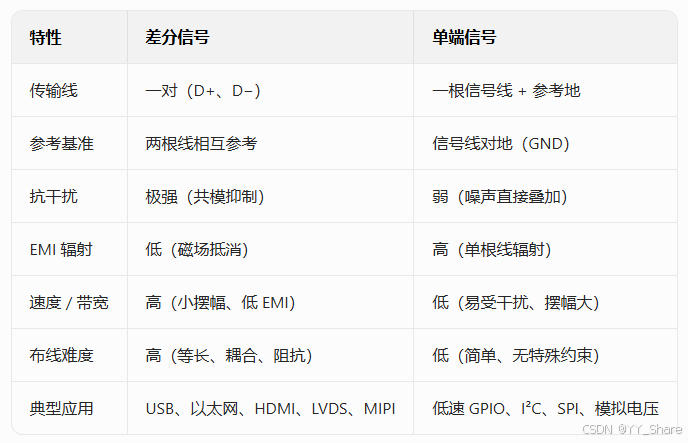

五、与单端信号对比

六、常见差分标准与应用

- LVDS(Low-Voltage Differential Signaling):差模 ±350mV,共模 1.2V;用于 LCD、摄像头、高速板间通信。

- USB 2.0/3.x:D+、D−差分对;高速数据传输,抗干扰强。

- 以太网(RJ45):差分双绞线(TX±、RX±);长距离、高速、抗干扰。

- HDMI/DP:多对差分线传输音视频;高带宽、低噪声。

- MIPI D-PHY/C-PHY:手机摄像头 / 屏幕;低功耗、高速、抗干扰。

- 音频平衡传输(XLR/TRS):专业音响,抑制环境噪声。

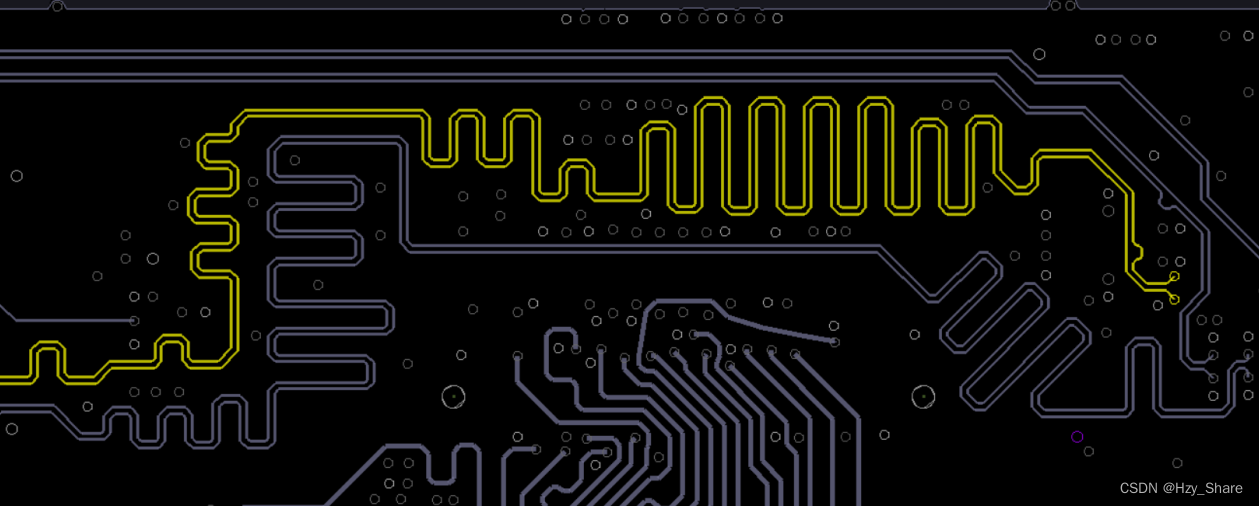

七、PCB 设计要点(关键)

- 等长匹配:两根线长度差 < 5mil(高速场景),保证信号同步、相位一致。

- 紧密耦合:平行、间距均匀(通常为线宽的 1--2 倍),增强共模抑制。

- 同层布线:避免跨层,减少阻抗不连续与寄生参数。

- 阻抗控制:按标准设计差分阻抗(如 90Ω/100Ω/120Ω),减少反射。

- 远离干扰源:远离时钟、电源、单端高速线,避免串扰。

- 完整参考平面:下方保持连续地 / 电源平面,提供稳定回流路径。