本文参考F. Wang and H. Wang, "A High-Power Broadband Multi-Primary DAT-Based Doherty Power Amplifier for mm-Wave 5G Applications ," in IEEE Journal of Solid-State Circuits, vol. 56, no. 6, pp. 1668-1681, June 2021, doi: 10.1109/JSSC.2021.3070800.

keywords: {Impedance;Modulation;Inverters;5G mobile communication;System-on-chip;Silicon;Peak to average power ratio;5G New Radio (NR);broadband;distributed active transformer (DAT);Doherty;efficiency enhancement;front-end module (FEM);linearity;millimeter-wave (mm-Wave) peak-to-average power ratio (PAPR);power amplifier (PA);power back-off (PBO)},

仅供学习使用

Doherty功放 **通过"有源负载调制"来提升功率回退时效率。**它通常由一个主放大器和一个辅助放大器组成。在低功率时,只有主放大器工作;当功率增大到一定程度,辅助放大器开启。通过设计输出网络,**辅助放大器的工作会主动改变主放大器看到的负载阻抗,使其在更宽的功率范围内都能接近最佳效率点工作,从而提升发射高峰均功率比信号平均效率。

多初级DAT 全称是多初级分布式有源变压器,是一种用于片上功率合成的变压器结构。**它通过独特的绕组布局(如论文中的六边形结构),将多个放大器单元的输出功率高效、低损耗地合并起来,以实现更高的总输出功率。多个初级绕组之间的连接实现了混合的串并联功率合成,在合成大量功率单元时能保持较低的损耗和良好的端口间对称性。

硅基毫米波功率放大器(PA)需要具有高功率和高峰值/回退效率,以高效放大多Gb/s的5G NR信号。本文提出了一种采用多初级分布式有源变压器(DAT)实现功率合成的全集成高功率宽带线性Doherty PA。

引入了一种基于变压器的阻抗逆变器用于有源负载调制,以及一种多初级DAT结构用于混合串并联功率合成。在此基础上,提出了一种具有更多设计自由度的基于变压器的Doherty合成器,以及一种基于多初级DAT的DohertyPA,用于同时实现有源负载调制和低损耗功率合成。电磁仿真结果表明,所提出的基于DAT的Doherty输出网络在所有主辅PA端口间实现了非常对称和平衡的负载阻抗。

I. 引言

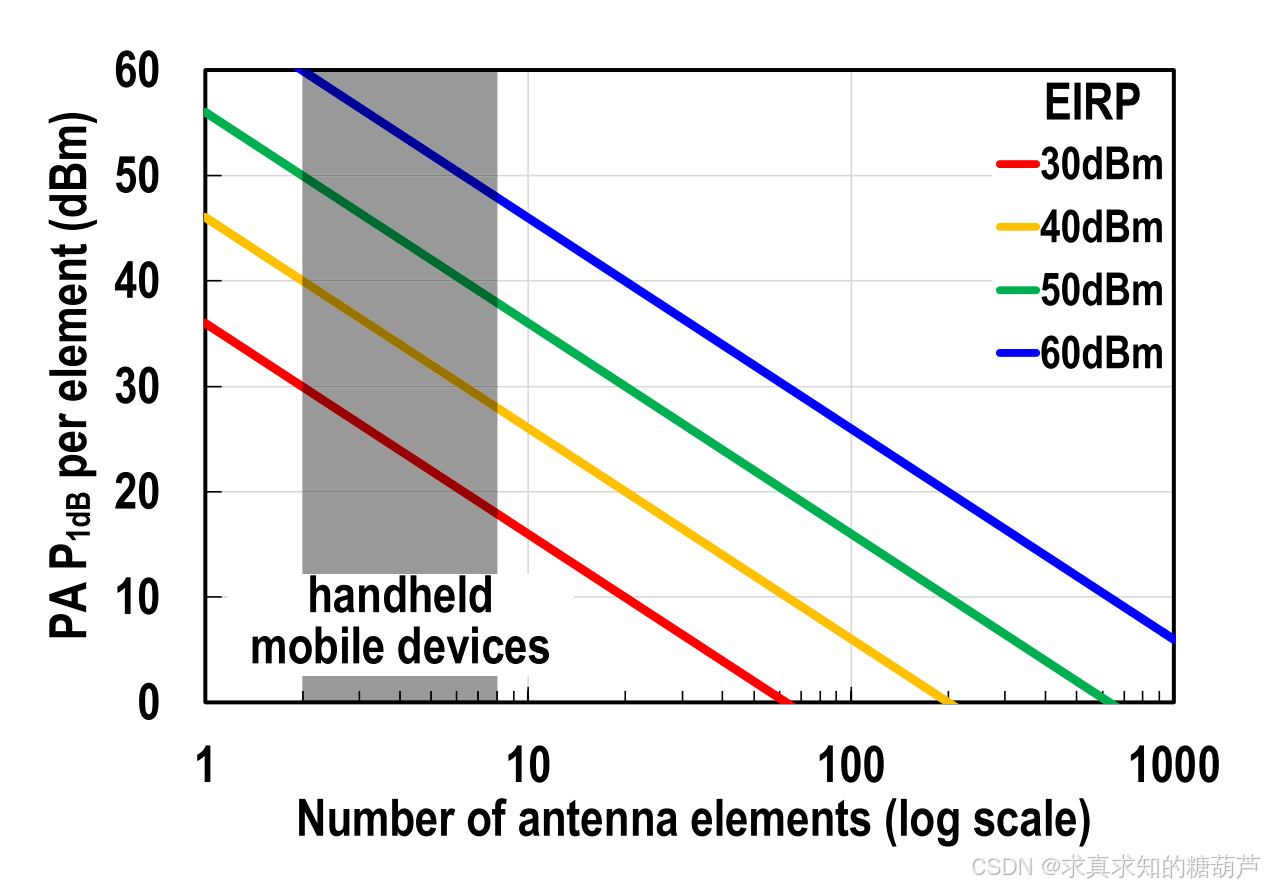

全球范围内对多Gb/s数据速率的持续需求推动了毫米波频段5G新空口规范的快速发展和标准化[1]-[3]。因此,人们对高性能且紧凑的毫米波5G前端模块 (FEM)的兴趣激增,以实现大规模多输入多输出(MIMO)技术 。对于毫米波5G系统,需要高有效全向辐射功率 来补偿较长链路距离上的路径损耗。虽然相控阵架构将在毫米波5G系统中无处不在,但在固定的EIRP下,每个单元的PoutP_{\text{out}}Pout和阵列规模之间存在权衡,如图1所示[4]-[10]。小型或中型阵列需要每个单元具有高PoutP_{\text{out}}Pout,而大型阵列可以放宽对每个单元PoutP_{\text{out}}Pout的要求,但会增加设计复杂性、阵列尺寸和成本。特别是对于用户设备,有限的尺寸通常限制了可行天线单元的数量(例如2x2) ,从而要求每个单元具有更高的PoutP_{\text{out}}Pout[1]。对于基站或基础设施,尽管有些应用借助高天线增益仅需适中的每单元PoutP_{\text{out}}Pout,但高PoutP_{\text{out}}Pout能力可能允许灵活的阵列操作,例如阵列划分和具有并发多流毫米波链路的子阵列[5],[6]。

图1. 每个PA单元的PoutP_{\text{out}}Pout与阵列规模之间的权衡。假设每个单元增益=5 dB,前端损耗=2 dB,信号PAPR=9 dB。

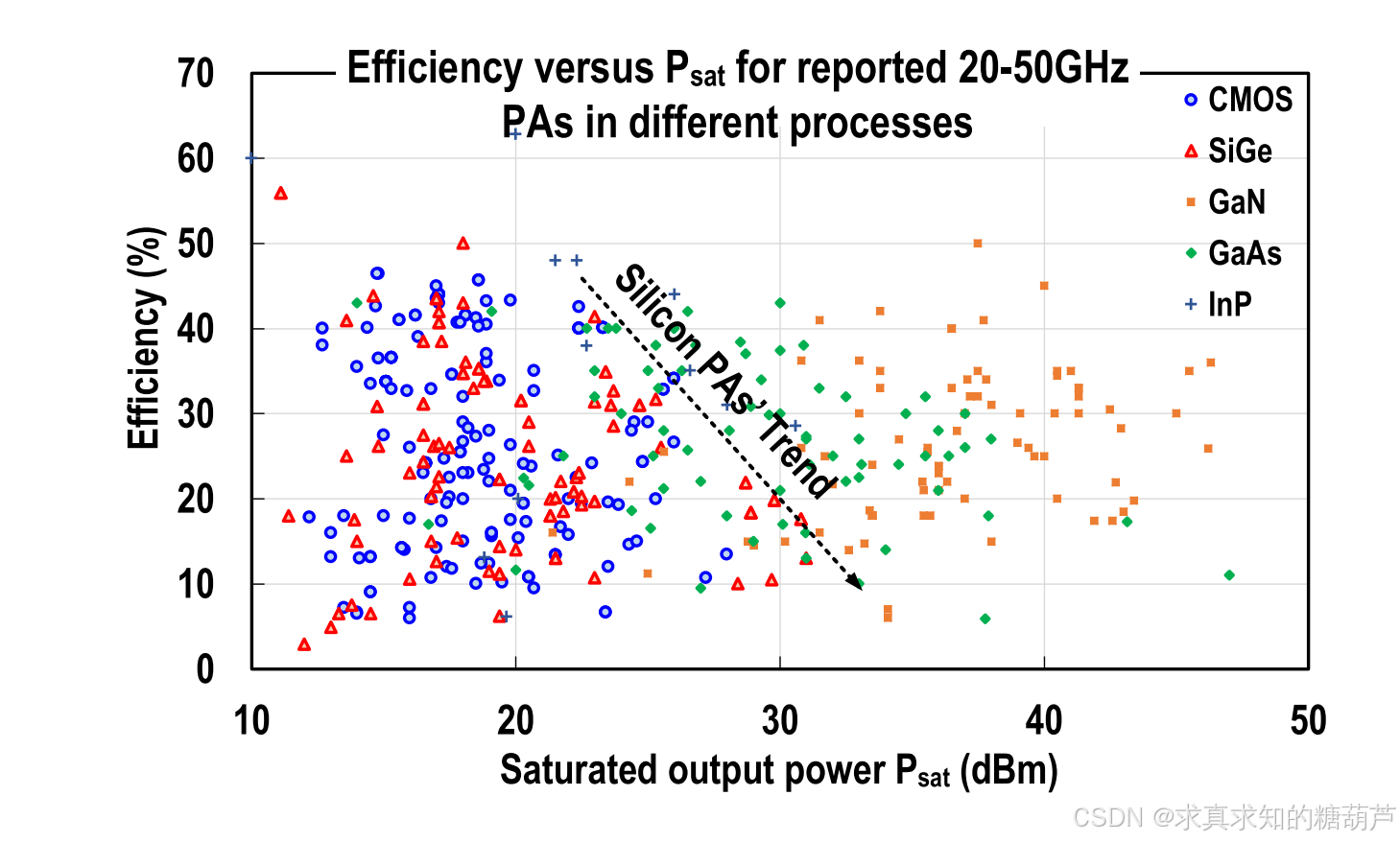

图2. 已报道的20-50 GHz PA的效率与输出功率比较。

硅平台具有大批量低成本和与其他模块高集成度的优势。然而,与III-V族化合物工艺相比,硅基毫米波功率放大器(PA)通常因器件击穿电压较低而受到PoutP_{\text{out}}Pout和效率的限制[11]。

如图2所示,低功率和中功率硅基毫米波PA的效率性能已显著提升[14]-[26]。相反,高功率硅基毫米波PA通常由于有损的功率合成而导致效率非常有限 。在毫米波频段产生高PoutP_{\text{out}}Pout需要在低击穿硅工艺中实现高效率PA和精细的功率合成。常见的功率合成技术包括空间功率合成[27],[28]、器件堆叠[29]-[31]、片上功率合成[32]-[40]等 。我们特别关注采用无源网络的片上功率合成,而其他技术(例如器件堆叠)可作为正交技术进一步增加PoutP_{\text{out}}Pout。已展示了多种片上功率合成技术,如威尔金森功率合成[32],[33]和零度功率合成[34] 。然而,许多已报道的高功率硅基毫米波PA常常由于无源效率低下和不同端口间阻抗不平衡而导致效率和线性度下降。此外,具有高峰均功率比(PAPR)的高速高频谱效率调制方案,例如高阶QAM、正交频分复用(OFDM)和载波聚合(CA),在5G NR信号中被广泛使用[1]。因此,PA通常需要在功率回退(PBO)模式下工作以适应高PAPR并提供足够的线性度。这使得PA的峰值效率和PBO效率对于电池寿命和热管理都至关重要。在已报道的效率提升技术[41]-[69]中,DohertyPA是"射频入-射频出"放大器,具有潜在的宽调制带宽和低基带开销。然而,现有的硅基毫米波DohertyPA通常由于片上Doherty输出网络而表现出效率和PoutP_{\text{out}}Pout下降[50]-[68]。此外,在具有挑战性的片上Doherty输出网络中增加高功率合成功能将使设计复杂化。因此,同时具有高功率、高峰值和PBO效率以及高线性度的硅基毫米波PA解决方案仍然难以实现。为了解决这些挑战,我们引入了一种采用多初级分布式有源变压器(DAT)功率合成的全集成高功率宽带线性DohertyPA,以高效放大多Gb/s的5G NR信号[69]。本文组织如下:回顾了Doherty有源负载调制和阻抗逆变器,并介绍了基于变压器的阻抗逆变器和提出的基于多初级DAT的DohertyPA。

II. 基于多初级DAT的DohertyPA

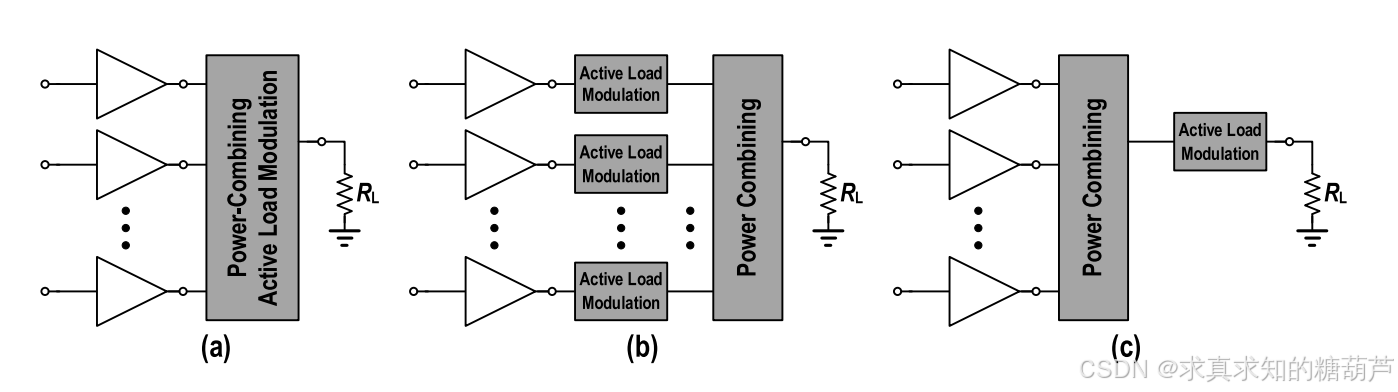

为了在硅基上实现高功率DohertyPA,需要低损耗的片上功率合成和有效的负载调制。为了避免过度的损耗和面积开销,非常希望在功率合成网络本身内实现Doherty有源负载调制[见图3(a)],而不是级联单独的网络[见图3(b)和©]。我们特别关注DAT风格的片上变压器基功率合成,因为它具有紧凑的外形尺寸,并且其效率对功率增强比(PER)的依赖性较弱[35]-[39]。

图3. 不同设计策略:(a) 同时主动负载调制与功率合成,(b) 先主动负载调制后功率合成,(c)(c)(c) 先功率合成后主动负载调制。

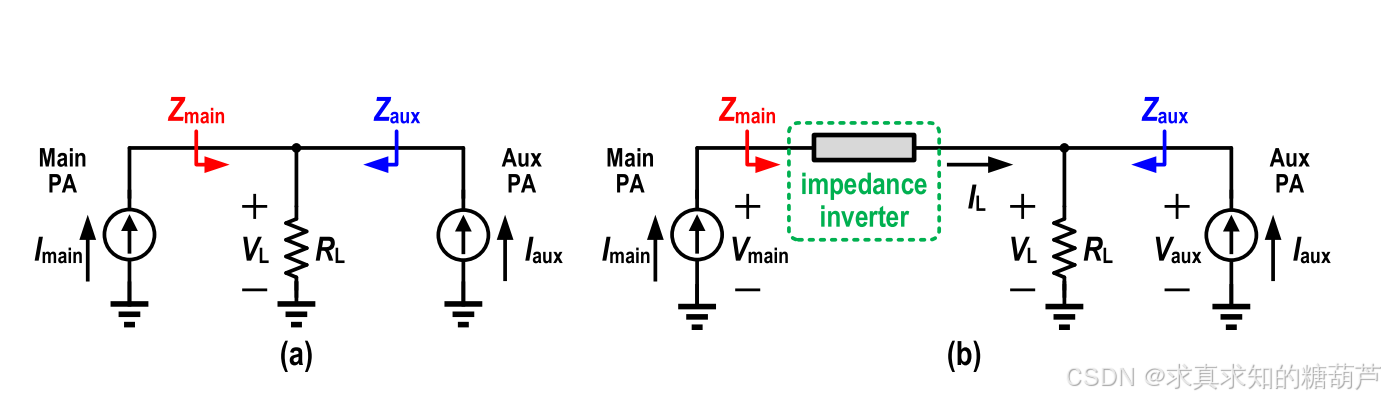

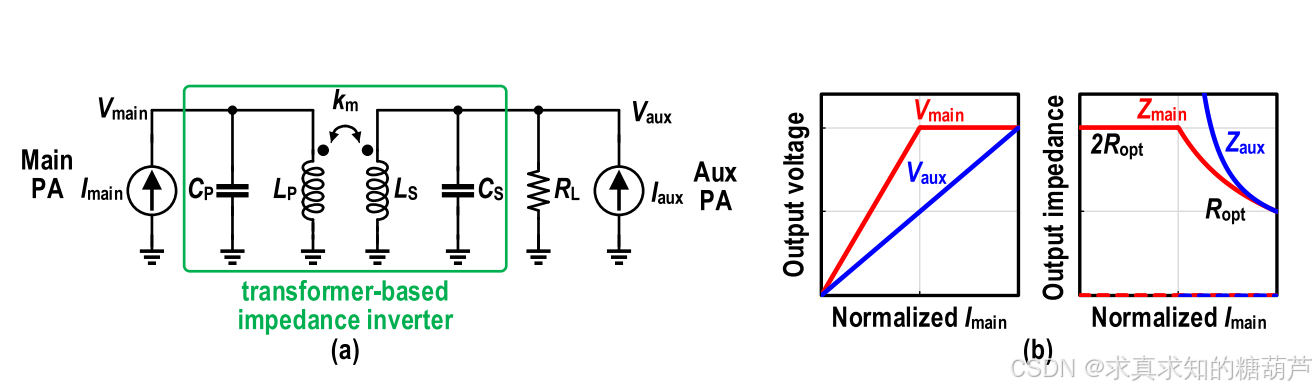

A. 有源负载调制与阻抗逆变网络

有源负载调制,即通过在其他端口施加信号来调制一个端口的阻抗,对于DohertyPA至关重要[41],[50]。其概念如图4(a)所示,其中主PA和辅助PA被建模为电流源。如果辅助PA设置为提供零电流,则主PA看到的负载阻抗为RLR_{L}RL。如果主PA和辅助PA分别提供ImainI_{\text{main}}Imain和IauxI_{\text{aux}}Iaux的电流,则两个电流都将流入负载,使得负载两端的电压VLV_{L}VL为RL(Imain+Iaux)R_{L}(I_{\text{main}}+I_{\text{aux}})RL(Imain+Iaux)。因此,主PA和辅助PA看到的等效负载阻抗分别为ZmainZ_{\text{main}}Zmain和ZauxZ_{\text{aux}}Zaux:

图4. (a) 有源负载调制概念。(b) 双向并行DohertyPA。

Zmain=RL(1+IauxImain),Zaux=RL(1+ImainIaux).(1) Z_{\text{main}}=R_{L}\left(1+\frac{I_{\text{aux}}}{I_{\text{main}}}\right),\quad Z_{\text{aux}}=R_{L}\left(1+\frac{I_{\text{main}}}{I_{\text{aux}}}\right).\quad(1) Zmain=RL(1+ImainIaux),Zaux=RL(1+IauxImain).(1)

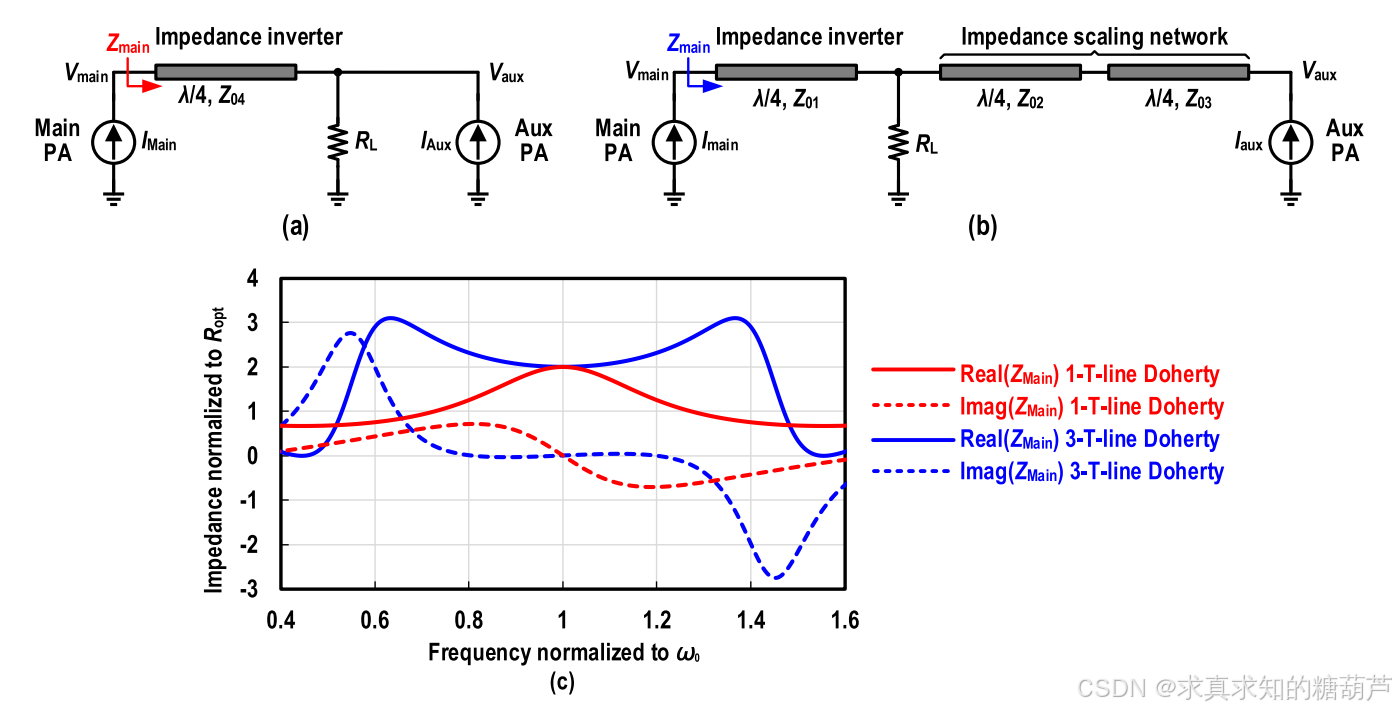

这本质上表明,一个PA的有效负载阻抗可以由另一个PA调制 。当输入驱动电平从最大值回退到6-dB PBO时(IauxI_{\text{aux}}Iaux从Iaux=ImainI_{\text{aux}}=I_{\text{main}}Iaux=Imain减少到Iaux=0I_{\text{aux}}=0Iaux=0),ZmainZ_{\text{main}}Zmain从2RL2R_{L}2RL下降到RLR_{L}RL。然而,这并非主PA保持恒定输出电压所需的"理想"负载变化,因此实际上负载调制需要进行"反转"。如图4(b)所示,使用阻抗逆变网络可以为主PA相对于辅助PA输出电流提供所需的负载调制。因此,阻抗逆变器是Doherty有源负载调制及其可实现的PBO效率增强的关键元件[50]。通常,一个二端口阻抗逆变器的传输或ABCD矩阵为:

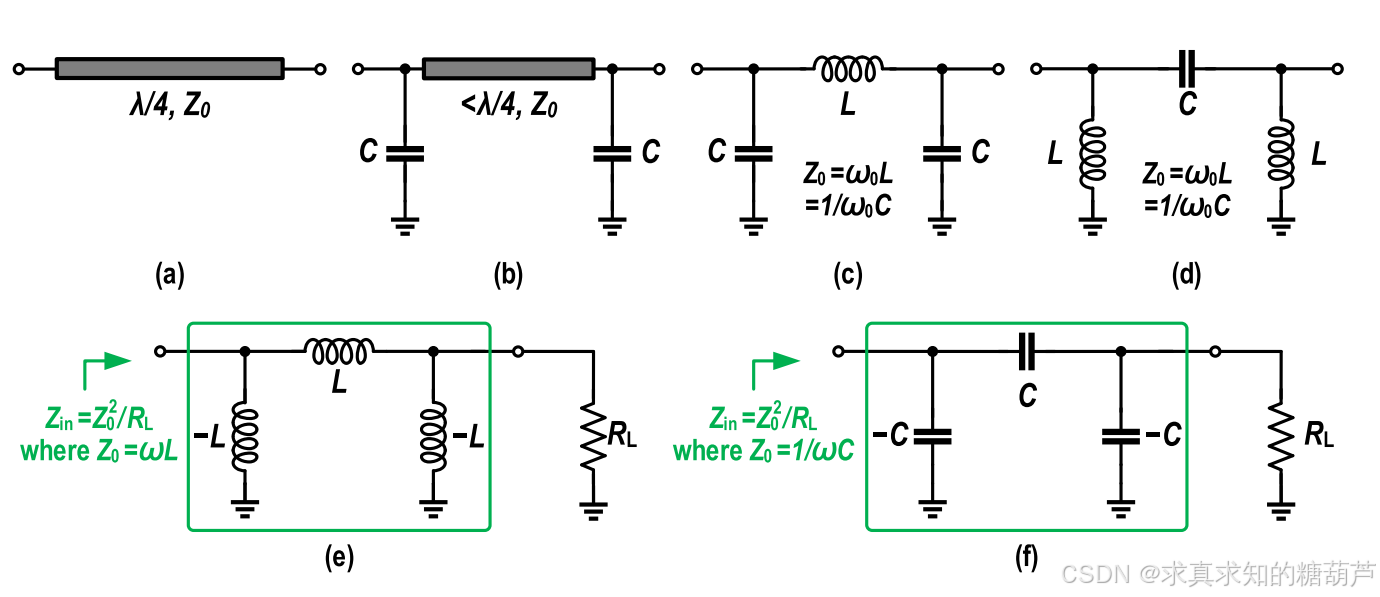

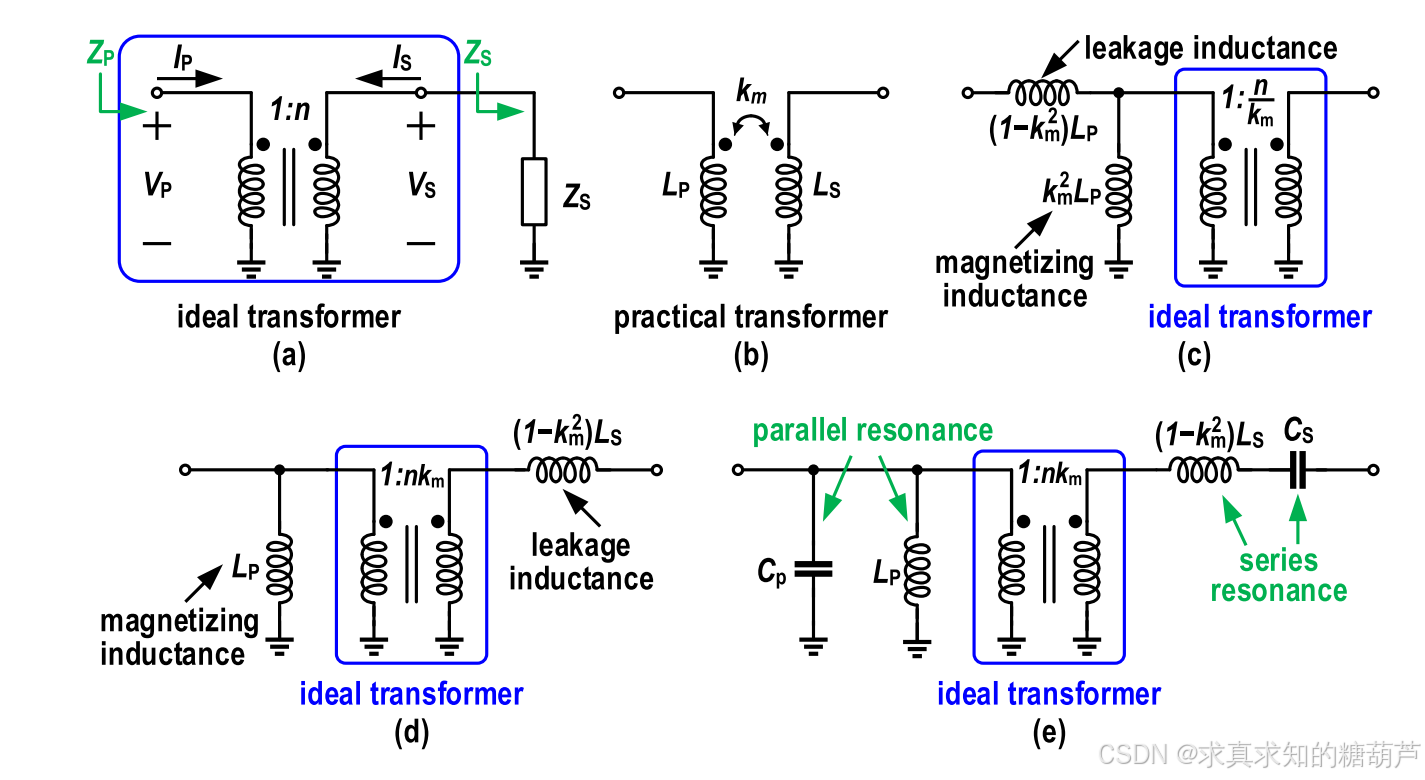

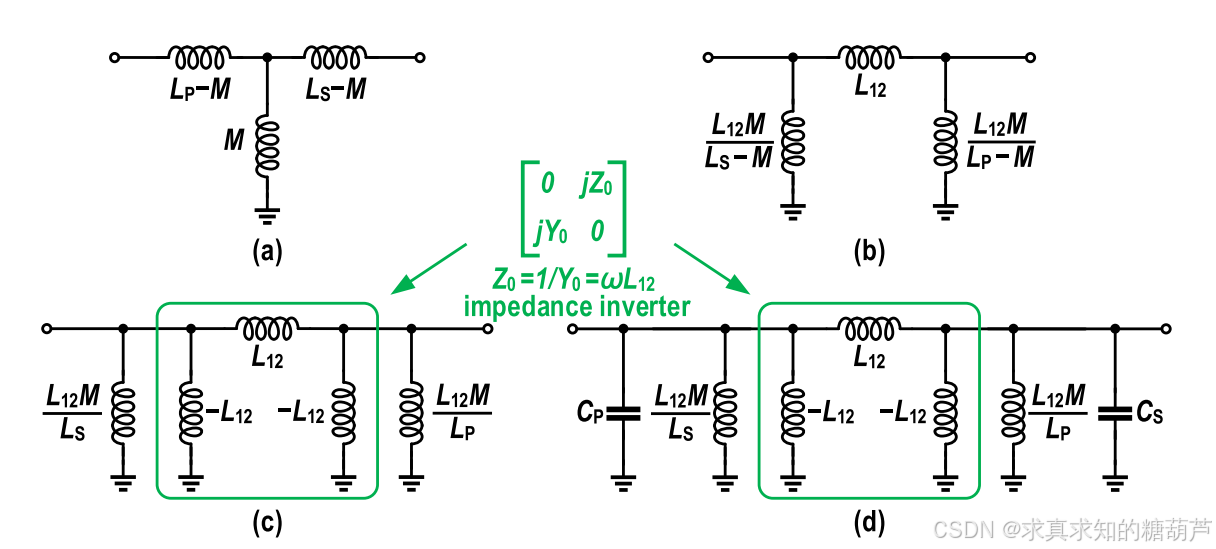

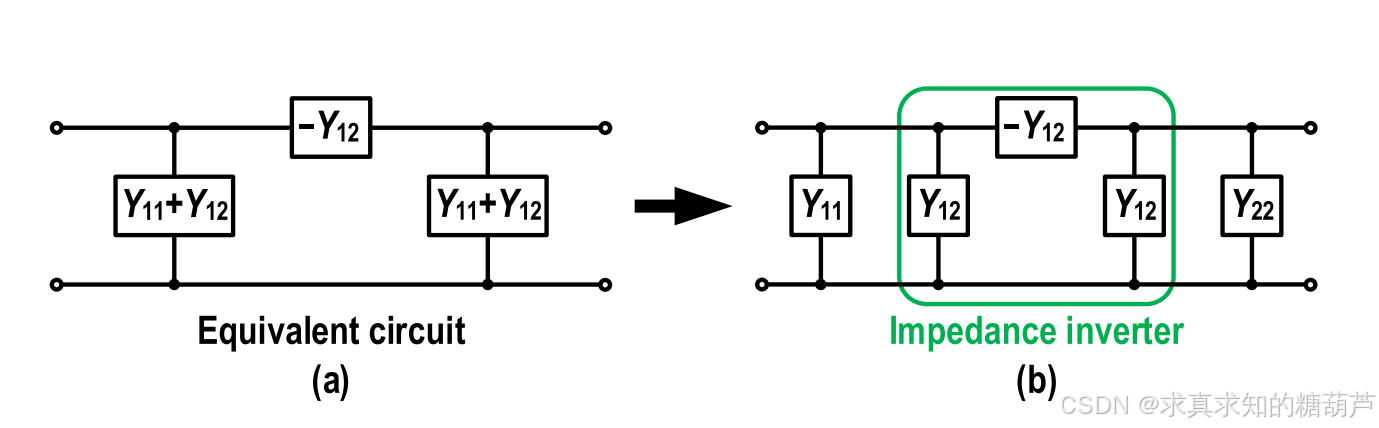

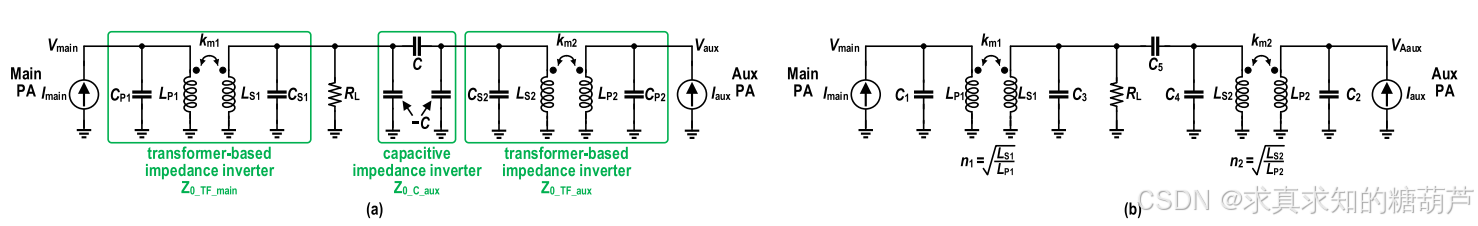

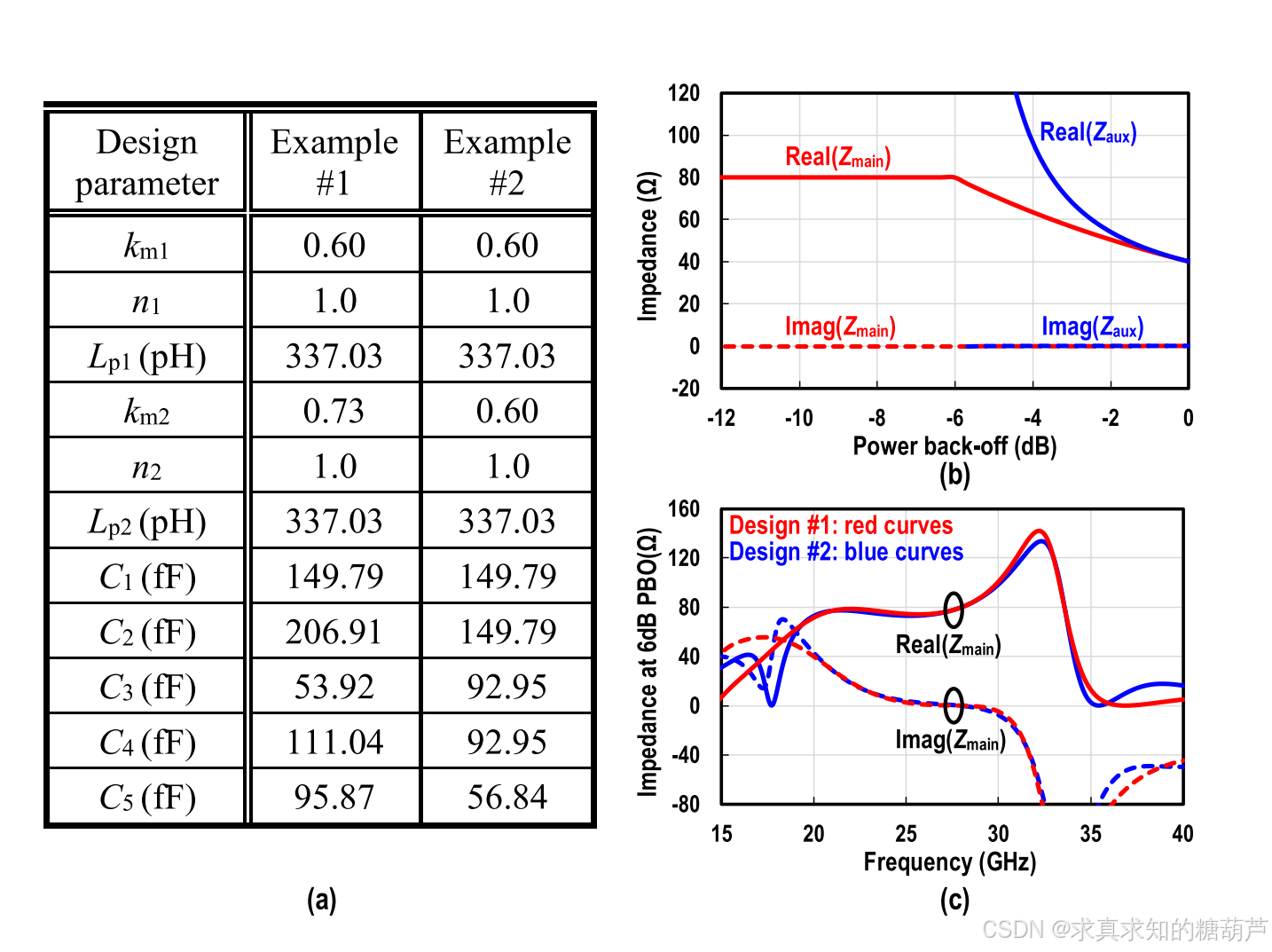

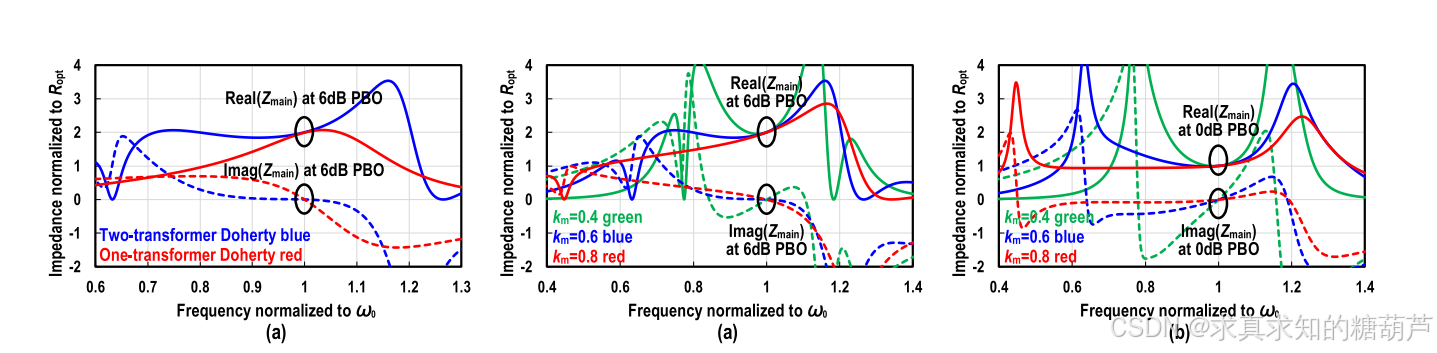

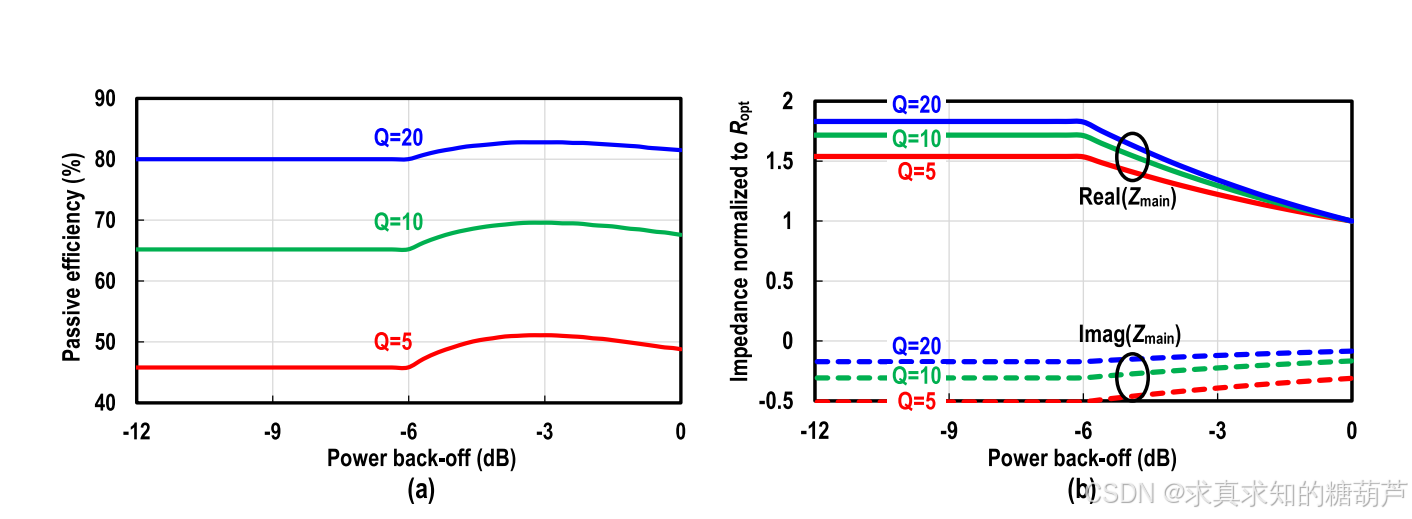

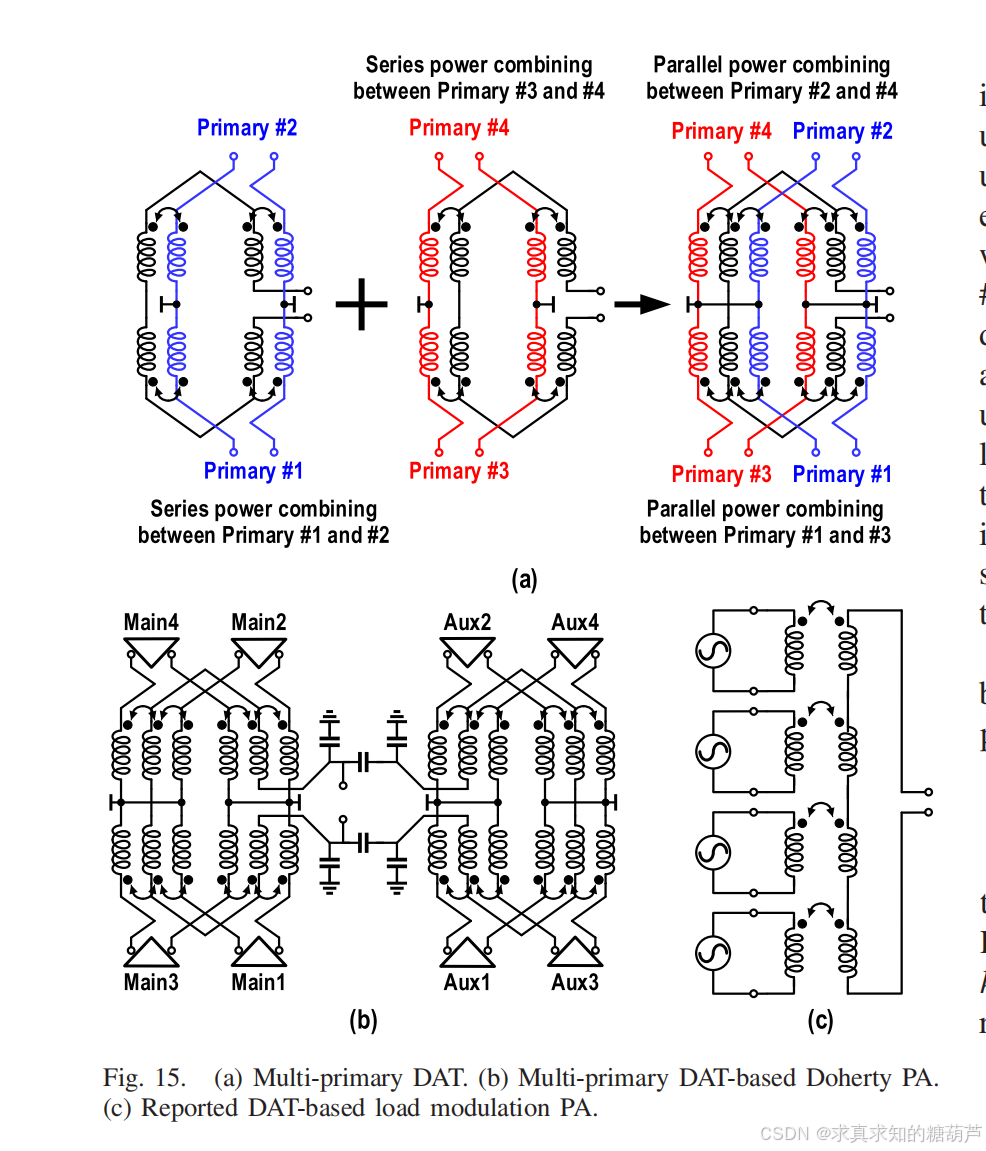

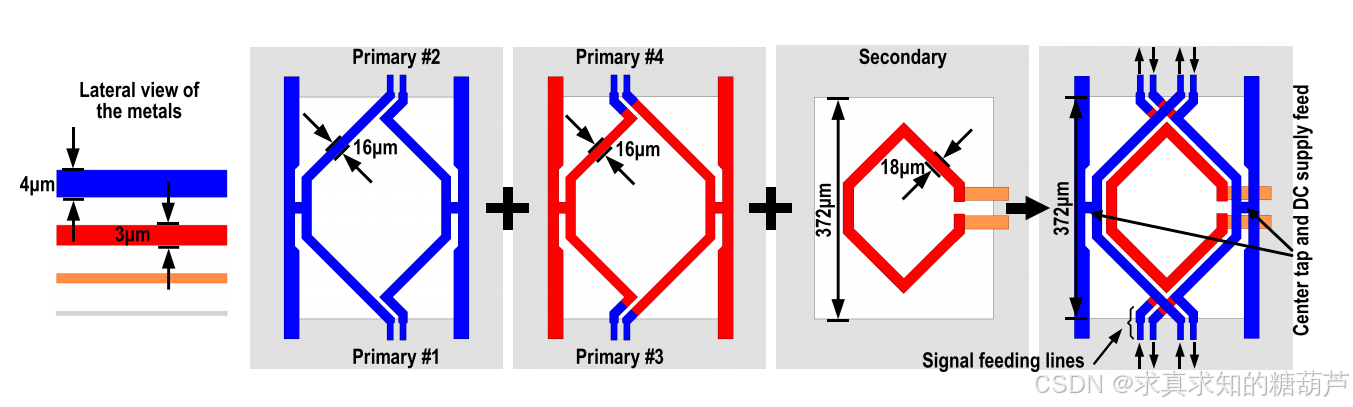

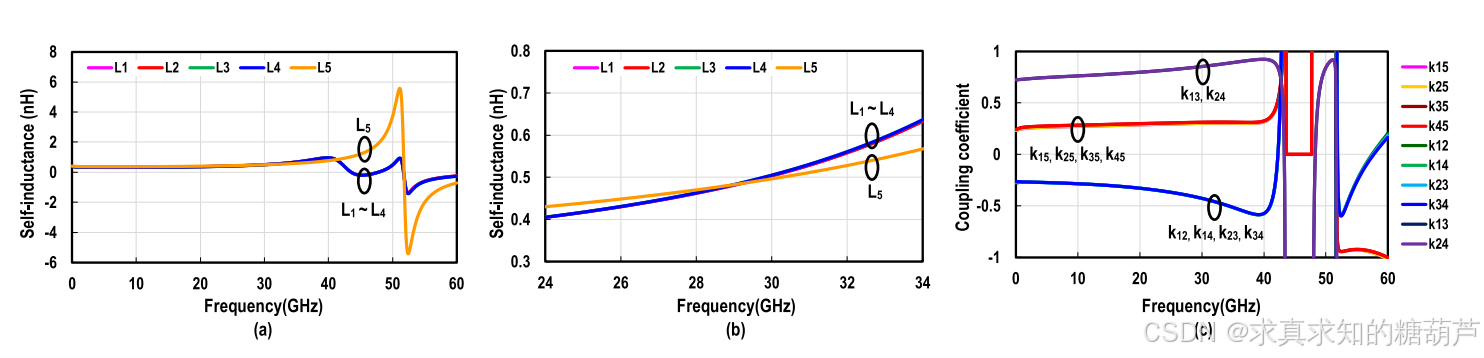

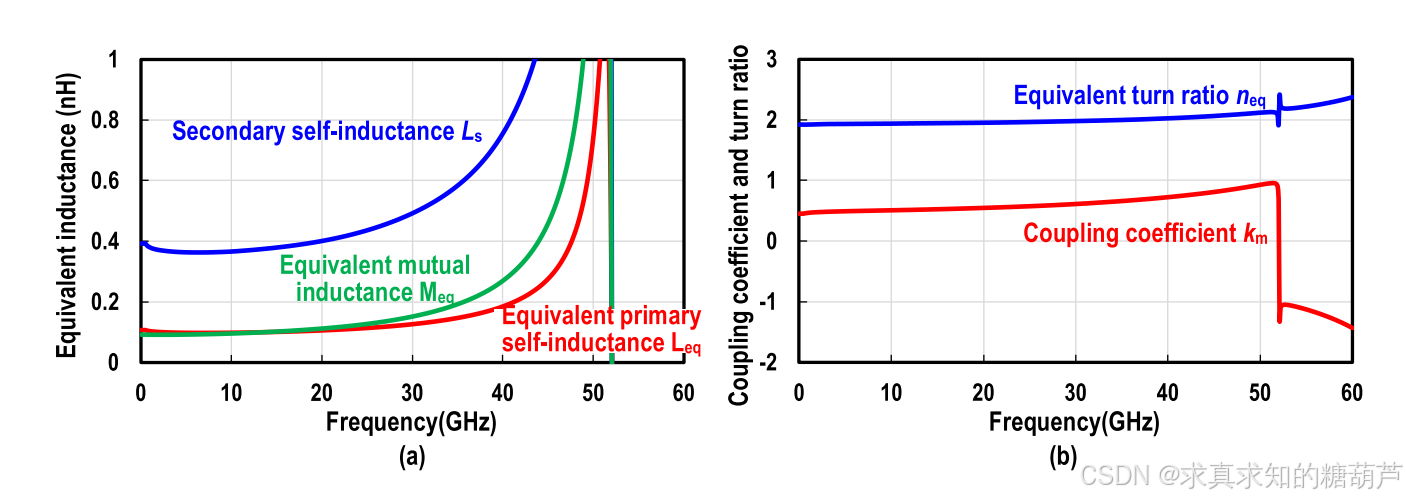

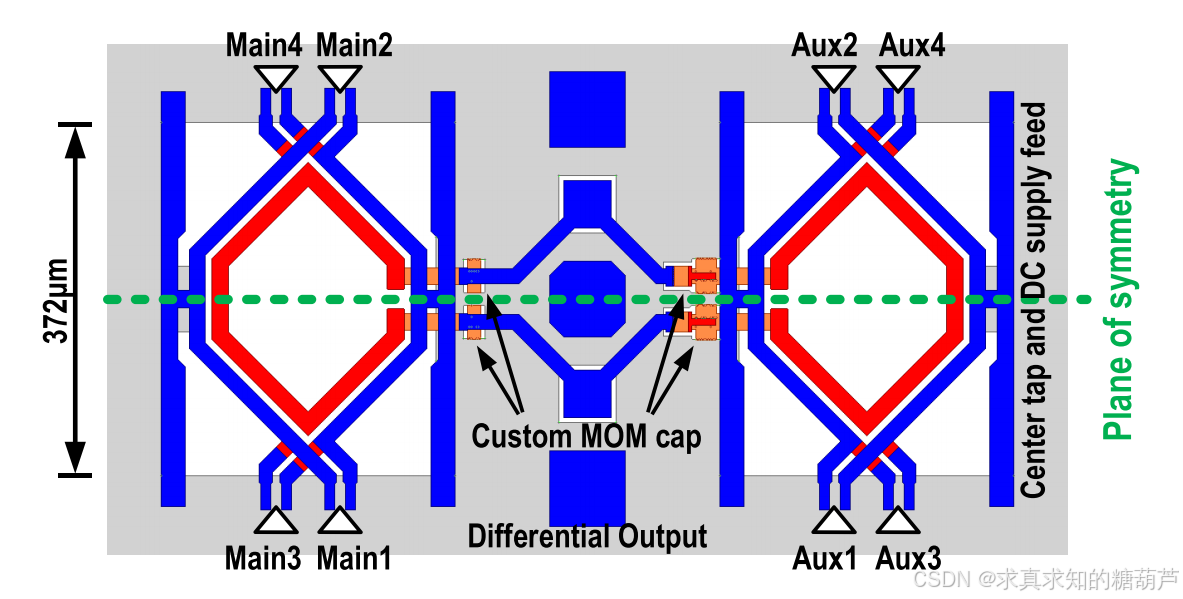

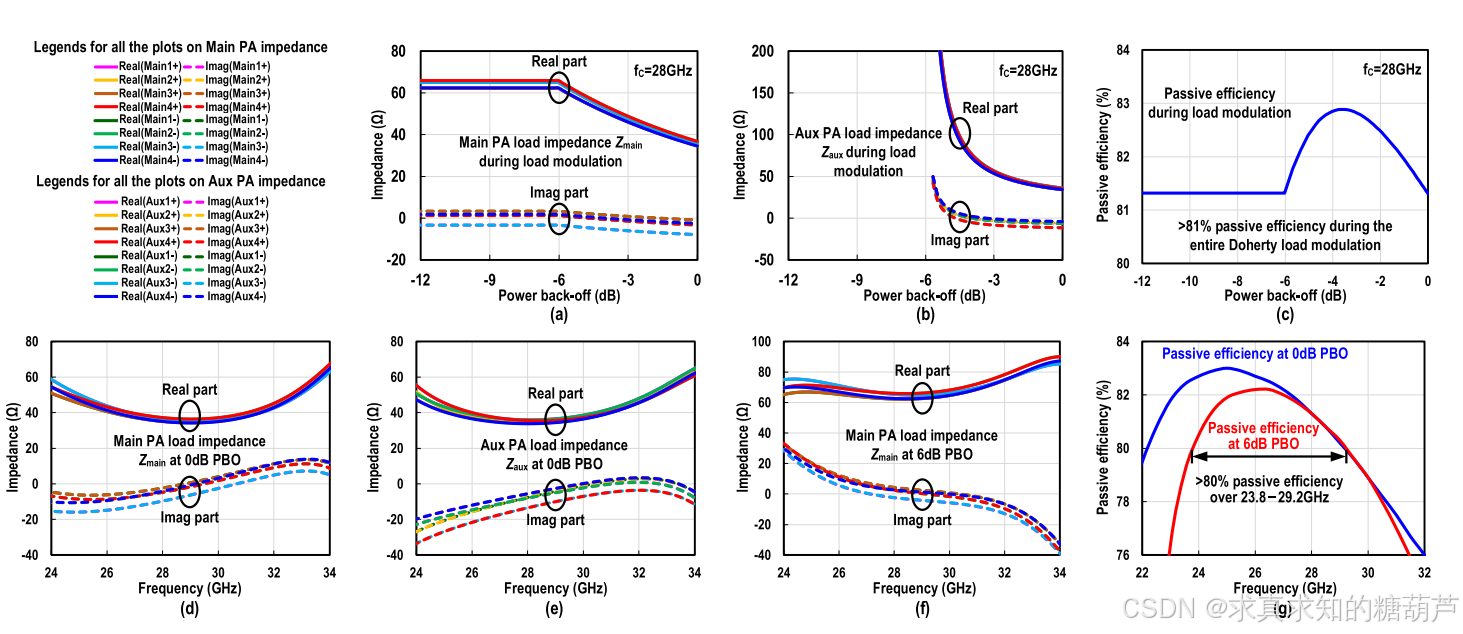

0jZ0jY00\](2) \\begin{bmatrix} 0 \& jZ_{0}\\\\ jY_{0} \& 0\\end{bmatrix}\\qquad(2) \[0jY0jZ00\](2) 其中Z0=1/Y0Z_{0}=1/Y_{0}Z0=1/Y0是特性阻抗。其基本实现包括λ/4\\lambda/4λ/4传输线(T-line)及其π\\piπ网络集总元件近似\[50\]--\[68\],如图5(a)--(d)所示。  图5. 无源阻抗逆变器示例:(a) λ/4\\lambda/4λ/4 传输线,(b) 容性加载传输线(\<λ/4\<\\lambda/4\<λ/4),© CLCπCLC\\piCLCπ网络,(d) LCLπLCL\\piLCLπ网络,(e) 感性阻抗逆变器,(f) 容性阻抗逆变器。 图5(e)和(f)中的电感和电容阻抗逆变网络值得进一步讨论。网络的输入阻抗可推导为Zin=Z02/RLZ_{\\text{in}}=Z_{0}\^{2}/R_{L}Zin=Z02/RL,其中对于电感阻抗逆变器Z0=ωLZ_{0}=\\omega LZ0=ωL,对于电容阻抗逆变器Z0=1/ωCZ_{0}=1/\\omega CZ0=1/ωC。因此,这些网络在无限带宽上执行阻抗逆变功能,但具有频率相关的特性阻抗Z0Z_{0}Z0\[71\]。然而,所需的负电感和负电容无法通过无源非互易网络实现,因此无法直接实现。需要精心设计网络拓扑以吸收这些负元件。 ### B. 理想变压器与实际变压器 变压器在射频和毫米波电路中有着广泛而重要的应用\[72\]。对于一个理想的1:n变压器(完美磁耦合且无损)\[见图6(a)\],电压和电流关系与匝数比nnn相关: n=VSVP=IPIS=LSLP(3) n=\\frac{V_{S}}{V_{P}}=\\frac{I_{P}}{I_{S}}=\\sqrt{\\frac{L_{S}}{L_{P}}}\\qquad(3) n=VPVS=ISIP=LPLS (3) 其中VPV_{P}VP, VSV_{S}VS 和 IPI_{P}IP, ISI_{S}IS定义于图6(a)中,LPL_{P}LP和LSL_{S}LS分别是初级和次级绕组的自感。因此,其阻抗变换特性为: ZP=VPIP=VS/n−nIS=1n2VS−IS=1n2ZS.(4) Z_{P}=\\frac{V_{P}}{I_{P}}=\\frac{V_{S}/n}{-nI_{S}}=\\frac{1}{n\^{2}}\\frac{V_{S}}{-I_{S}}=\\frac{1}{n\^{2}}Z_{S}.\\qquad(4) ZP=IPVP=−nISVS/n=n21−ISVS=n21ZS.(4) 本质上,初级看到的阻抗ZPZ_{P}ZP相对于次级负载阻抗ZSZ_{S}ZS按照常数1/n21/n\^{2}1/n2进行缩放。 物理变压器通常采用绕组间金属走线构成\[72\]\[见图6(b)\]。磁耦合通过耦合系数量化: km=MLPLS(5) k_{m}=\\frac{M}{\\sqrt{L_{P}L_{S}}}\\qquad(5) km=LPLS M(5) 其中M是初级和次级绕组之间的互感;其包含漏感/磁化电感和一个理想变压器的等效电路如图6©和(d)所示。漏感和磁化电感在初级和次级之间的分配是任意的\[72\]。漏感会导致阻抗缩放行为的偏差。在实际设计中需要高耦合度以确保其作为阻抗缩放网络的功能。可以添加串联电容C1C_{1}C1和并联电容C2C_{2}C2,分别与漏感和磁化电感形成串联和并联谐振。这也在谐振频率处形成了一个基于变压器的阻抗缩放网络,如图6(e)所示。  图6. (a) 理想变压器。(b) 实际变压器。© 等效电路。(d) 等效电路。(e) 基于变压器的阻抗缩放网络。 ### C. 基于变压器的阻抗逆变器 尽管通常实践将变压器用作阻抗缩放网络,但物理变压器实际上可以被设计用作阻抗逆变器而不是阻抗缩放网络\[69\],\[70\]。设计步骤如下所示。首先,物理变压器可以建模为一个T网络\[72\],该网络使用三个电感来模拟绕组之间的互感,如图7(a)所示。然后,这个T网络可以通过T-π(Y-Δ)变换转换为等效的π网络,如图7(b)所示,其中串联电感为:  图7. (a) T网络模型。(b) 等效Π\\PiΠ网络。© 并联电感分开的等效Π\\PiΠ网络。(d) 基于变压器的阻抗逆变器。 L12=LPLS−M2M=(1km−km)nLP.(6) L_{12}=\\frac{L_{P}L_{S}-M\^{2}}{M}=\\left(\\frac{1}{k_{m}}-k_{m}\\right) nL_{P}.\\qquad(6) L12=MLPLS−M2=(km1−km)nLP.(6) 接下来,图7(b)中的并联电感可以分解为: L12MLS−M=L12MLS∣∣(−L12)=(1−km2)LP∣∣(−L12)L12MLP−M=L12MLP∣∣(−L12)=(1−km2)LS∣∣(−L12).(8) \\begin{align\*}\\frac{L_{12}M}{L_{S}-M}\&=\\frac{L_{12}M}{L_{S}}\|\|(-L_{12})=(1-k_{m}\^{2})L_{P}\|\|(-L_{12})\\\\\\frac{L_{12}M}{L_{P}-M}\&=\\frac{L_{12}M}{L_{P}}\|\|(-L_{12})=(1-k_{m}\^{2})L_{S}\|\|(-L_{12}).\\end{align\*}\\qquad(8) LS−ML12MLP−ML12M=LSL12M∣∣(−L12)=(1−km2)LP∣∣(−L12)=LPL12M∣∣(−L12)=(1−km2)LS∣∣(−L12).(8) 因此,这个等效网络可以重画为图7©,这是一个带有两个剩余并联电感L12M/LSL_{12}M/L_{S}L12M/LS和L12M/LPL_{12}M/L_{P}L12M/LP的感性阻抗逆变器\[见图5(e)\]。此感性阻抗逆变器要求0\<∣L12∣\<∞0\<\|L_{12}\|\<\\infty0\<∣L12∣\<∞,即0\<∣km∣\<10\<\|k_{m}\|\<10\<∣km∣\<1,这对于物理变压器总是成立的。对于∣km∣=1\|k_{m}\|=1∣km∣=1的极端情况,即L12=0L_{12}=0L12=0,它变成如图6(a)所示的阻抗缩放网络;对于km=0k_{m}=0km=0的极端情况,即L12=∞L_{12}=\\inftyL12=∞,(7)和(8)变成两个不耦合的电感LPL_{P}LP和LSL_{S}LS,此网络也无法执行阻抗逆变功能。图7©中的这两个并联电感可以通过添加两个并联电容CPC_{P}CP和CSC_{S}CS来谐振掉,其值由下式给出: CP=LSω02L12M=1ω02(1−km2)LP(9) \\begin{align\*} C_{P}\&=\\frac{L_{S}}{\\omega_{0}\^{2}L_{12}M}=\\frac{1}{\\omega_{0}\^{2}(1-k_{m}\^{2})L_{P}}\\\\\\end{align\*}\\qquad(9) CP=ω02L12MLS=ω02(1−km2)LP1(9) CS=LPω02L12M=1ω02(1−km2)LS(10) \\begin{align\*} C_{S}\&=\\frac{L_{P}}{\\omega_{0}\^{2}L_{12}M}=\\frac{1}{\\omega_{0}\^{2}(1-k_{m}\^{2})L_{S}}\\end{align\*}\\qquad(10) CS=ω02L12MLP=ω02(1−km2)LS1(10) 其中ω0\\omega_{0}ω0是工作频率。最终,这导出了一个基于变压器的阻抗逆变器,如图7(d)所示。其特性阻抗为: Z0_TF=∣ω0L12∣=ω01−km2∣km∣nLP.(11) Z_{0\\_TF}=\|\\omega_{0}L_{12}\|=\\omega_{0}\\frac{1-k_{m}\^{2}}{\|k_{m}\|}nL_{P}.\\qquad(11) Z0_TF=∣ω0L12∣=ω0∣km∣1−km2nLP.(11) 一种更通用的阻抗逆变器设计方法介绍如下。对于一个通用的无损二端口网络,Y12=Y21Y_{12}=Y_{21}Y12=Y21,此网络可建模为图8(a)中的等效电路\[74\]。该等效电路可以进一步重画,如图8(b)所示,其中可以清晰地观察到一个特性阻抗为Z0=1/Y0=∣1/Y12∣Z_{0}=1/Y_{0}=\|1/Y_{12}\|Z0=1/Y0=∣1/Y12∣的阻抗逆变器。因此,如果两个残余并联元件Y11Y_{11}Y11和Y22Y_{22}Y22被谐振掉或被其他网络吸收,此网络可以作为一个阻抗逆变器。显然,图5(e)和(f)中的网络是图8(b)中通用网络的两个例子。  图8. (a) 和 (b) 通用无损二端口网络的等效电路。 ### D. 基于变压器的Doherty合成器 基于此分析,可以构建一个示例性和概念性的"单变压器"Doherty功率放大器(PA),如图9(a)所示。  图9. (a) 单变压器DohertyPA。(b) 原理图级仿真结果。  图10. (a) 单传输线DohertyPA。(b) 三传输线DohertyPA。© 在6-dB PBO下主PA负载阻抗ZmainZ_{\\text{main}}Zmain的比较。 图9(b)中的原理图仿真证明了这个概念性的"单变压器"网络确实实现了所需的有源负载调制。阻抗逆变器中的变压器为实现基于多端口变压器的功率合成(例如DAT)开辟了可能性。 此外,在基于传输线的Doherty合成器的辅助PA路径中可以加入一个阻抗缩放网络,如图10(a)和(b)所示\[59\]。这导致了更宽带的负载调制和主PA的阻性负载更大,如图10©所示。如图11(a)所示,为了在主路和辅路中均实现功率合成并拓宽载波带宽,一个包含一个基于变压器的阻抗逆变器和一个容性阻抗逆变器的等效阻抗缩放网络被插入到基于变压器的Doherty合成器的辅助路径中。容性阻抗逆变器中的两个负电容−C1-C_{1}−C1可以被两个并联的实际电容(CS1C_{S1}CS1和CS2C_{S2}CS2)吸收。电容CP1C_{P1}CP1和CP2C_{P2}CP2用于吸收PA器件输出电容。 对于所提出的双变压器Doherty合成器\[见图11(a)\],可以推导出所有参数的封闭形式设计方程。将展示一个对称DohertyPA设计作为示例。假设PA的最佳负载阻抗和器件输出电容分别为RoptR_{opt}Ropt和CdevC_{dev}Cdev。两个变压器的匝数比、磁耦合系数和初级自感分别表示为:主PA路径中的变压器TF1的参数为km1k_{m1}km1、n1n_{1}n1和LP1L_{P1}LP1,辅助PA路径中的变压器TF2的参数为km2k_{m2}km2、n2n_{2}n2和LP2L_{P2}LP2。基于变压器的阻抗逆变器和容性阻抗逆变器的特性阻抗分别表示为Z0_TF_mainZ_{0\\_TF\\_main}Z0_TF_main、Z0_TF_auxZ_{0\\_TF\\_aux}Z0_TF_aux和Z0_C_auxZ_{0\\_C\\_aux}Z0_C_aux。对于Doherty操作,在6-dB PBO时,主PA的负载阻抗给出为 Z0_TF_main2/RL=2Ropt(12)Z_{0\\_TF\\_main}\^{2}/R_{L}=2R_{opt}\\qquad(12)Z0_TF_main2/RL=2Ropt(12) 其中 Z0_TF_main=ω01−km12km1n1LP1.(13)Z_{0\\_TF\\_main}=\\omega_{0}\\frac{1-k_{m1}\^{2}}{k_{m1}}n_{1}L_{P1}.\\qquad(13)Z0_TF_main=ω0km11−km12n1LP1.(13)  图11. (a) 提出的双变压器DohertyPA。(b) 对称双变压器DohertyPA。 表I. 双变压器Doherty合成器设计参数。 | 设计参数 | 提出的双变压器Doherty合成器 | 已报道的双变压器Doherty合成器\[61\] | |:-------------|:-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|:--------------------------------------------------------------------------------------------------------------------------------------------------------------------| | km1k_{m1}km1 | km1k_{m1}km1 (设计自由度) | km1k_{m1}km1 (设计自由度) | | n1n_{1}n1 | n1n_{1}n1 (设计自由度) | n1n_{1}n1 (设计自由度) | | Lp1L_{p1}Lp1 | km12RoptRLω0n1(1−km12)\\frac{k_{m1}\\sqrt{2R_{opt}R_{L}}}{\\omega_{0}n_{1}(1-k_{m1}\^{2})}ω0n1(1−km12)km12RoptRL | km12RoptRLω0n1(1−km12)\\frac{k_{m1}\\sqrt{2R_{opt}R_{L}}}{\\omega_{0}n_{1}(1-k_{m1}\^{2})}ω0n1(1−km12)km12RoptRL | | km2k_{m2}km2 | km2k_{m2}km2 (设计自由度) | n22Ropt/8RL+1−n22Ropt/8RL\\sqrt{n_{2}\^{2}R_{opt}/8R_{L}+1}-\\sqrt{n_{2}\^{2}R_{opt}/8R_{L}}n22Ropt/8RL+1 −n22Ropt/8RL | | n2n_{2}n2 | n2n_{2}n2 (设计自由度) | n2n_{2}n2 (设计自由度) | | Lp2L_{p2}Lp2 | Lp2L_{p2}Lp2 (设计自由度) | n1km12RoptRLω0n22(1−km12)\\frac{n_{1}k_{m1}\\sqrt{2R_{opt}R_{L}}}{\\omega_{0}n_{2}\^{2}(1-k_{m1}\^{2})}ω0n22(1−km12)n1km12RoptRL | | C1C_{1}C1 | n1ω0km12RoptRL\\frac{n_{1}}{\\omega_{0}k_{m1}\\sqrt{2R_{opt}R_{L}}}ω0km12RoptRL n1 | n1ω0km12RoptRL\\frac{n_{1}}{\\omega_{0}k_{m1}\\sqrt{2R_{opt}R_{L}}}ω0km12RoptRL n1 | | C2C_{2}C2 | 1ω02(1−km22)LP2\\frac{1}{\\omega_{0}\^{2}(1-k_{m2}\^{2})L_{P2}}ω02(1−km22)LP21 | n22(1−km12)ω0n1km1(1−km22)2RoptRL\\frac{n_{2}\^{2}(1-k_{m1}\^{2})}{\\omega_{0}n_{1}k_{m1}(1-k_{m2}\^{2})\\sqrt{2R_{opt}R_{L}}}ω0n1km1(1−km22)2RoptRL n22(1−km12) | | C3C_{3}C3 | 1ω0n1km12RoptRL−km2ω02(1−km22)n2LP2Ropt2RL\\frac{1}{\\omega_{0}n_{1}k_{m1}\\sqrt{2R_{opt}R_{L}}}-\\frac{k_{m2}}{\\omega_{0}\^{2}(1-k_{m2}\^{2})n_{2}L_{P2}}\\sqrt{\\frac{R_{opt}}{2R_{L}}}ω0n1km12RoptRL 1−ω02(1−km22)n2LP2km22RLRopt | km1ω0n12RoptRL\\frac{k_{m1}}{\\omega_{0}n_{1}\\sqrt{2R_{opt}R_{L}}}ω0n12RoptRL km1 | | C4C_{4}C4 | 1ω02(1−km22)n22LP2−km2ω02(1−km22)n2LP2Ropt2RL\\frac{1}{\\omega_{0}\^{2}(1-k_{m2}\^{2})n_{2}\^{2}L_{P2}}-\\frac{k_{m2}}{\\omega_{0}\^{2}(1-k_{m2}\^{2})n_{2}L_{P2}}\\sqrt{\\frac{R_{opt}}{2R_{L}}}ω02(1−km22)n22LP21−ω02(1−km22)n2LP2km22RLRopt | km22(1−km12)ω0n1km1(1−km22)2RoptRL\\frac{k_{m2}\^{2}(1-k_{m1}\^{2})}{\\omega_{0}n_{1}k_{m1}(1-k_{m2}\^{2})\\sqrt{2R_{opt}R_{L}}}ω0n1km1(1−km22)2RoptRL km22(1−km12) | | C5C_{5}C5 | km2ω02(1−km22)n2LP2Ropt2RL\\frac{k_{m2}}{\\omega_{0}\^{2}(1-k_{m2}\^{2})n_{2}L_{P2}}\\sqrt{\\frac{R_{opt}}{2R_{L}}}ω02(1−km22)n2LP2km22RLRopt | 1−km12ω0n1km12RoptRL\\frac{1-k_{m1}\^{2}}{\\omega_{0}n_{1}k_{m1}\\sqrt{2R_{opt}R_{L}}}ω0n1km12RoptRL 1−km12 | 在0-dB PBO时,辅助PA的负载阻抗给出为 2RL⋅Z0_TF_aux2/Z0_C_aux2=Ropt(14)2R_{L}\\cdot Z_{0\\_TF\\_aux}\^{2}/Z_{0\\_C\\_aux}\^{2}=R_{opt}\\qquad(14)2RL⋅Z0_TF_aux2/Z0_C_aux2=Ropt(14) 其中 Z0_TF_aux=ω01−km22km2n2LP2(15)Z_{0\\_TF\\_aux}=\\omega_{0}\\frac{1-k_{m2}\^{2}}{k_{m2}}n_{2}L_{P2}\\qquad(15)Z0_TF_aux=ω0km21−km22n2LP2(15) 且 Z0_C_aux=1ω0C.(16)Z_{0\\_C\\_aux}=\\frac{1}{\\omega_{0}C}.\\qquad(16)Z0_C_aux=ω0C1.(16) 由(12)和(13)式,可以推导出变压器TF1的初级自感Lp1L_{p1}Lp1为 LP1=km1Z0_TF_mainω0n1(1−km12)=km12RoptRLω0n1(1−km12).(17)L_{P1}=\\frac{k_{m1}Z_{0\\_TF\\_main}}{\\omega_{0}n_{1}(1-k_{m1}\^{2})}=\\frac{k_{m1}\\sqrt{2R_{opt}R_{L}}}{\\omega_{0}n_{1}(1-k_{m1}\^{2})}.\\qquad(17)LP1=ω0n1(1−km12)km1Z0_TF_main=ω0n1(1−km12)km12RoptRL .(17) 表(a). 设计参数。 | 设计参数 | 示例 #1 | 示例 #2 | |:------------------|:-------|:-------| | km1k_{m1}km1 | 0.60 | 0.60 | | n1n_{1}n1 | 1.0 | 1.0 | | Lp1L_{p1}Lp1 (pH) | 337.03 | 337.03 | | km2k_{m2}km2 | 0.73 | 0.60 | | n2n_{2}n2 | 1.0 | 1.0 | | Lp2L_{p2}Lp2 (pH) | 337.03 | 337.03 | | C1C_{1}C1 (fF) | 149.79 | 149.79 | | C2C_{2}C2 (fF) | 206.91 | 149.79 | | C3C_{3}C3 (fF) | 53.92 | 92.95 | | C4C_{4}C4 (fF) | 111.04 | 92.95 | | C5C_{5}C5 (fF) | 95.87 | 56.84 | 类似于(9)和(10)式,电容CP1C_{P1}CP1、CS1C_{S1}CS1和CP2C_{P2}CP2、CS2C_{S2}CS2可以计算为 CP1=1ω02(1−km12)LP1=n1ω0km12RoptRL(18)C_{P1}=\\frac{1}{\\omega_{0}\^{2}(1-k_{m1}\^{2})L_{P1}}=\\frac{n_{1}}{\\omega_{0}k_{m1}\\sqrt{2R_{opt}R_{L}}}\\qquad(18)CP1=ω02(1−km12)LP11=ω0km12RoptRL n1(18) CS1=1ω02(1−km12)n12LP1=1ω0n1km12RoptRL(19)C_{S1}=\\frac{1}{\\omega_{0}\^{2}(1-k_{m1}\^{2})n_{1}\^{2}L_{P1}}=\\frac{1}{\\omega_{0}n_{1}k_{m1}\\sqrt{2R_{opt}R_{L}}}\\qquad(19)CS1=ω02(1−km12)n12LP11=ω0n1km12RoptRL 1(19) 以及 CP2=1ω02(1−km22)LP2(20)C_{P2}=\\frac{1}{\\omega_{0}\^{2}(1-k_{m2}\^{2})L_{P2}}\\qquad(20)CP2=ω02(1−km22)LP21(20) CS2=1ω02(1−km22)n22LP2.(21)C_{S2}=\\frac{1}{\\omega_{0}\^{2}(1-k_{m2}\^{2})n_{2}\^{2}L_{P2}}.\\qquad(21)CS2=ω02(1−km22)n22LP21.(21) 由(14)-(16)式,电容C可以计算为 C=1ω0Z0_TF_auxRopt2RL=km2ω02(1−km22)n2LP2Ropt2RL.(22)C=\\frac{1}{\\omega_{0}Z_{0\\_TF\\_aux}}\\sqrt{\\frac{R_{opt}}{2R_{L}}}=\\frac{k_{m2}}{\\omega_{0}\^{2}(1-k_{m2}\^{2})n_{2}L_{P2}}\\sqrt{\\frac{R_{opt}}{2R_{L}}}.\\qquad(22)C=ω0Z0_TF_aux12RLRopt =ω02(1−km22)n2LP2km22RLRopt .(22) 所提出的双变压器Doherty合成器可以重画为图11(b)所示,对应的设计参数如表I所示。只要满足 Z0_TF_aux=ω01−km22km2n2LP2≥n1km1Ropt(23)Z_{0\\_TF\\_aux}=\\omega_{0}\\frac{1-k_{m2}\^{2}}{k_{m2}}n_{2}L_{P2}\\geq n_{1}k_{m1}R_{opt}\\qquad(23)Z0_TF_aux=ω0km21−km22n2LP2≥n1km1Ropt(23) 和 n2km2≤2RL/Ropt(24)n_{2}k_{m2}\\leq\\sqrt{2R_{L}/R_{opt}}\\qquad(24)n2km2≤2RL/Ropt (24) 就可以分别确保C3≥0C_{3}\\geq 0C3≥0和C4≥0C_{4}\\geq 0C4≥0,这在实践中很容易实现。总之,对于给定的负载牵引阻抗RoptR_{opt}Ropt,以及km1k_{m1}km1、n1n_{1}n1、km2k_{m2}km2、n2n_{2}n2和Lp2L_{p2}Lp2,所引入的双变压器Doherty合成器中所有设计参数均可计算,如表I所示。 表I中还添加了文献\[60\]中报道的双变压器Doherty合成器方法的设计空间以进行比较。\[60\]中的方法是从λ/4\\lambda/4λ/4传输线的集总近似推导出来的,两个变压器的励磁电感均源自辅助路径LCLπLCL\\piLCLπ网络中的相同并联电感,这限制了变压器的设计自由度。相比之下,引入的方法直接基于变压器阻抗逆变器的概念推导,主路和辅助路的变压器分别仅由(12)和(14)式决定。两种方法在主路变压器上具有相同的设计自由度,但引入的方法在辅助路径变压器上多了两个设计自由度,即km2k_{m2}km2和Lp2L_{p2}Lp2。 \[60\]中方法的设计空间是所引入方法设计空间的真子集。因此,所引入的方法是用于双变压器Doherty合成器设计的更通用的方法。  图12. 双变压器Doherty合成器示例#1和#2。(a) 设计参数。(b) 负载调制。© 6-dB PBO时主PA的阻抗。 为了说明差异,以设计目标Ropt=40ΩR_{opt}=40\\OmegaRopt=40Ω、fC=28f_{C}=28fC=28 GHz、n1=n2=1n_{1}=n_{2}=1n1=n2=1和km1=0.6k_{m1}=0.6km1=0.6为例。\[60\]中的方法只有图12(a)中所示的示例#1这一个解,而所引入的方法有无限多个解,其中就包括示例#1和#2。示例#1和#2都实现了理想的Doherty负载调制,如图12(b)所示,它们在6-dB PBO下的主PA负载阻抗随频率的变化如图12©所示。  图13. (a) 单变压器(km=0.6k_{m}=0.6km=0.6)和双变压器(km1=km2=0.6k_{m1}=k_{m2}=0.6km1=km2=0.6)Doherty合成器在6-dB PBO下ZmainZ_{\\text{main}}Zmain的比较;双变压器Doherty在(b)6-dB PBO和©0-dB PBO下ZmainZ_{\\text{main}}Zmain随不同kmk_{m}km的变化。 主PA负载阻抗ZmainZ_{main}Zmain在6-dB PBO下的频率响应对于宽带负载调制和效率提升至关重要\[50\]。如图13(a)所示,与单变压器Doherty合成器相比,双变压器Doherty合成器具有更宽的工作带宽,其ZmainZ_{main}Zmain在更大带宽上变化更小。此外,其ZmainZ_{main}Zmain在频带边缘处更高,这有助于拓宽效率带宽。变压器的耦合系数kmk_{m}km以不同的趋势影响ZmainZ_{main}Zmain在6-dB和0-dB PBO下的带宽。当kmk_{m}km从0.4增加到0.8时,ZmainZ_{main}Zmain在6-dB PBO的带宽先增加后减少\[见图13(b)\],而ZmainZ_{main}Zmain在0-dB PBO的带宽则从0.4增加到0.8\[见图13(b)\]。变压器的损耗(品质因数)影响Doherty合成器的整体无源效率和有源负载调制的有效性,如图14(a)和(b)所示,其中假设初级绕组和次级绕组具有相同的品质因数。变压器的损耗越低,有源负载调制越有效,其中ZmainZ_{main}Zmain在6-dB PBO与在0-dB PBO的比值更接近理想情况2,并且ZmainZ_{main}Zmain更呈阻性。  图14. 变压器品质因数对双变压器DohertyPA的(a)无源效率和(b)有源负载调制的影响。 ### E. 基于多初级 DAT 的Doherty合路器 为实现高功率的片上功率合成,我们引入了一个六边形多初级DAT合路器网络,以实现混合串并联的多路功率合成\[见图15(a)\]。它将两个DAT网络合并在一起,以进一步增强功率合成能力。它在初级绕组#1与#2之间以及#3与#4之间实现了串联功率合成;同时,在初级绕组#1与#3之间以及#2与#4之间实现了并联功率合成。  图15. (a) 多初级DAT。(b) 基于多初级DAT的DohertyPA。© 已报道的基于DAT的负载调制PA。 将图11中的变压器替换为多初级DAT后,基于变压器的Doherty合路器最终被拓展为主路和辅路均采用所提出的多初级DAT构型\[见图15(b)\]。它同时实现了低损耗功率合成和所需的Doherty有源负载调制。四个差分主PA(Main1-Main4)和四个差分辅助PA(Aux1-Aux4)分别以DAT方式通过串/并联功率合成进行合并。 值得一提的是,已报道的基于DAT的负载调制网络\[75\]--\[77\]属于电压模式串联Doherty合路器\[见图15©\]。它要求PA支路在关断时具有低输出阻抗,以实现所需的Doherty有源负载调制和效率提升。因此,它通常采用电压模式PA或在PA输出端使用并联开关\[75\]来实现,这在毫米波频段具有挑战性。相比之下,我们所提出的基于多初级DAT的DohertyPA属于电流模式Doherty,它采用常见的线性模拟PA,因此可以在毫米波频段工作。  图16. 引入多原发性DAT的三维电子显微镜模型 所提出的多初级DAT的布局如图16所示,其中多初级绕组使用顶层和第二层金属实现,次级绕组使用第二层金属。初级和次级绕组像经典DAT\[35\]中那样边缘耦合,而初级绕组本身则是宽边耦合(初级#1和#3之间以及初级#2和#4之间)。与已报道的使用方形或八角形结构的DAT设计\[35\]-\[39\]不同,本设计采用了独特的六边形结构。这种独特的结构最大限度地减少了连接不同PA功率单元输出的馈线重叠和长度,从而避免了馈线或互连引线引起的额外损耗和电感\[35\]。它同时简化了直流供电馈入以及与PA功率单元的布局集成,因为四个差分功率单元仅放置在两侧。 一个多初级DAT(nwn_{w}nw个初级绕组和一个次级绕组)可以使用阻抗矩阵\[ZZZ\]进行建模,该矩阵关联端口电压和电流: \[V\]=\[Z\]\[I\].(25)\[V\]=\[Z\]\[I\].\\qquad(25)\[V\]=\[Z\]\[I\].(25) 将初级绕组#1到# nwn_{w}nw 记作绕组#1到# nwn_{w}nw,次级绕组记作绕组# (nw+1)(n_{w}+1)(nw+1)。对于一个具有耦合系数 kijk_{ij}kij(在第iii个和第jjj个绕组之间)的低损耗 nwn_{w}nw 初级DAT,其第 iii 个绕组的电压-电流关系为: Vi=jωLiIi+∑j=1,j≠inw+1(MijIj)(26)V_i=j\\omega L_iI_i+\\sum_{j=1,j\\neq i}\^{n_w+1}\\left(M_{ij}I_j\\right)\\qquad(26)Vi=jωLiIi+j=1,j=i∑nw+1(MijIj)(26)  图17. 多初级DAT的3-D电磁仿真结果。(a) 自感。(b) 自感的放大视图。© 耦合系数。 其中 LiL_{i}Li 是第 iii 个绕组的自感,Mij=Mji=kij(LiLj)1/2M_{ij}=M_{ji}=k_{ij}(L_{i}L_{j})\^{1/2}Mij=Mji=kij(LiLj)1/2 是第 iii 个和第 jjj 个绕组之间的互感,1≤i1\\leq i1≤i, j≤(nw+1)j\\leq(n_{w}+1)j≤(nw+1)。图17展示了所引入的多初级DAT的自感和耦合系数的3-D电磁仿真结果。所有初级绕组的自感非常对称,初级和次级绕组之间以及初级绕组之间的耦合系数也非常对称。在 nwn_{w}nw 个初级绕组上施加平衡的端口电流激励时,它们的端口电压将相同。通过将 nwn_{w}nw 个初级绕组叠合在一起(本设计中 nw=4n_{w}=4nw=4),可以为多初级DAT获得一个等效的双端口变压器,其设计参数 LP,eqL_{P,\\text{eq}}LP,eq、km,eqk_{m,\\text{eq}}km,eq 和 neqn_{\\text{eq}}neq 可以计算得出,如表I所示,等效负载牵引阻抗 Ropt,eq=Ropt/nwR_{\\text{opt},\\text{eq}}=R_{\\text{opt}}/n_{w}Ropt,eq=Ropt/nw。等效双端口变压器的参数如图18所示。  图18. 多初级DAT的等效双端口变压器参数。  图19. 基于多初级DAT的Doherty组合器三维电磁模型 所提出的基于多初级DAT的Doherty合路器的布局如图19所示,其中使用了定制的MOM(金属-氧化物-金属)电容,与设计工具包中的MIM(金属-绝缘体-金属)电容相比具有更高的品质因数。差分输出相对于对称平面对称性良好,其不平衡性非常小或可忽略不计。  图20. 基于多初级DAT的Doherty合路器的3-D电磁仿真结果。在28 GHz下随功率回退的性能:(a) ZmainZ_{\\text{main}}Zmain,(b) ZauxZ_{\\text{aux}}Zaux,和 © 无源效率。随频率变化的性能:(d) 0-dB PBO时的 ZmainZ_{\\text{main}}Zmain,(e) 0-dB PBO时的 ZauxZ_{\\text{aux}}Zaux,(f) 6-dB PBO时的 ZmainZ_{\\text{main}}Zmain,和 (g) 0-dB 和 6-dB PBO时的无源效率。 在理想对称DohertyPA操作下,所提出的基于多初级DAT的Doherty合路器的3-D电磁仿真结果如图20所示。图20(a)和(b)在28 GHz的仿真结果验证了所提出的网络实现了卓越的Doherty有源负载调制。此外,所有八个主/辅助差分PA的所有单端复阻抗在所有功率电平下都保持了良好的平衡与对称。这非常有利于PA的整体输出功率和线性度,而在传统的采用大规模功率合成的高功率PA中,不平衡或不对称的负载阻抗会导致PA在较低的功率电平下压缩\[36\], \[39\]。所提出的网络实现了大规模多路功率合成和所需的Doherty有源负载调制,在28 GHz下总无源效率\>81%(损耗\<1-dB)\[见图20©\]。仿真还表明,所提出的网络在24-34 GHz频带内,在0-dB PBO(峰值 PoutP_{\\text{out}}Pout)\[见图20(d)和(e)\]和6-dB PBO \[见图20(f)\]下,对所有16个主/辅助端口均支持宽带对称操作。在整个Doherty负载调制过程中,在23.8-29.2 GHz频率范围内,0-dB和6-dB PBO下均保持了\>80%的总无源效率(损耗\<1-dB)\[见图20(g)\]。总之,所提出的基于多初级DAT的Doherty合路器同时实现了宽带卓越的Doherty有源负载调制和低损耗功率合成。