目录

1.基本概念

- ARM概念:①ARM公司(负责设计内核)②ARM(Advanced RISC Machine )系列处理器内核

- CPU内核

- CISI: Complex Instruction Set Computer 复杂指令集计算机 (如x86架构CPU)

- **优点:**功能完善

- **缺点:**芯片面积大、加工成本高、实现复杂、体积大、功耗大(二八效应:80%情况下只用到了20%功能)

- RISC: Reduced Instruction Set Computer 精简指令集计算机

- **优点:**芯片面积小、加工成本低、实现简单、体积小、功耗小,大量使用寄存器(大多数数据操作都在寄存器中完成),指令执行速度更快;

- **应用场景:**手机、平板、单片机、嵌入式设备

- CISI: Complex Instruction Set Computer 复杂指令集计算机 (如x86架构CPU)

- ARM系列处理器内核发展历程

|---------------|----------|-------------------------------------------------------------------|

| ARM | ------> | Cortex |

| ARM1 ~ ARM11 | ------> | A:Application 应用级-跑系统(安卓 / Linux) (如imx6ull 是Cortex-A7内核,32位) |

| ARM1 ~ ARM11 | ------> | R:real time 实时性领域- 汽车电子、航空航天 |

| ARM1 ~ ARM11 | ------> | M: Micro 微控制器-MCU 单片机领域(如STM32) |

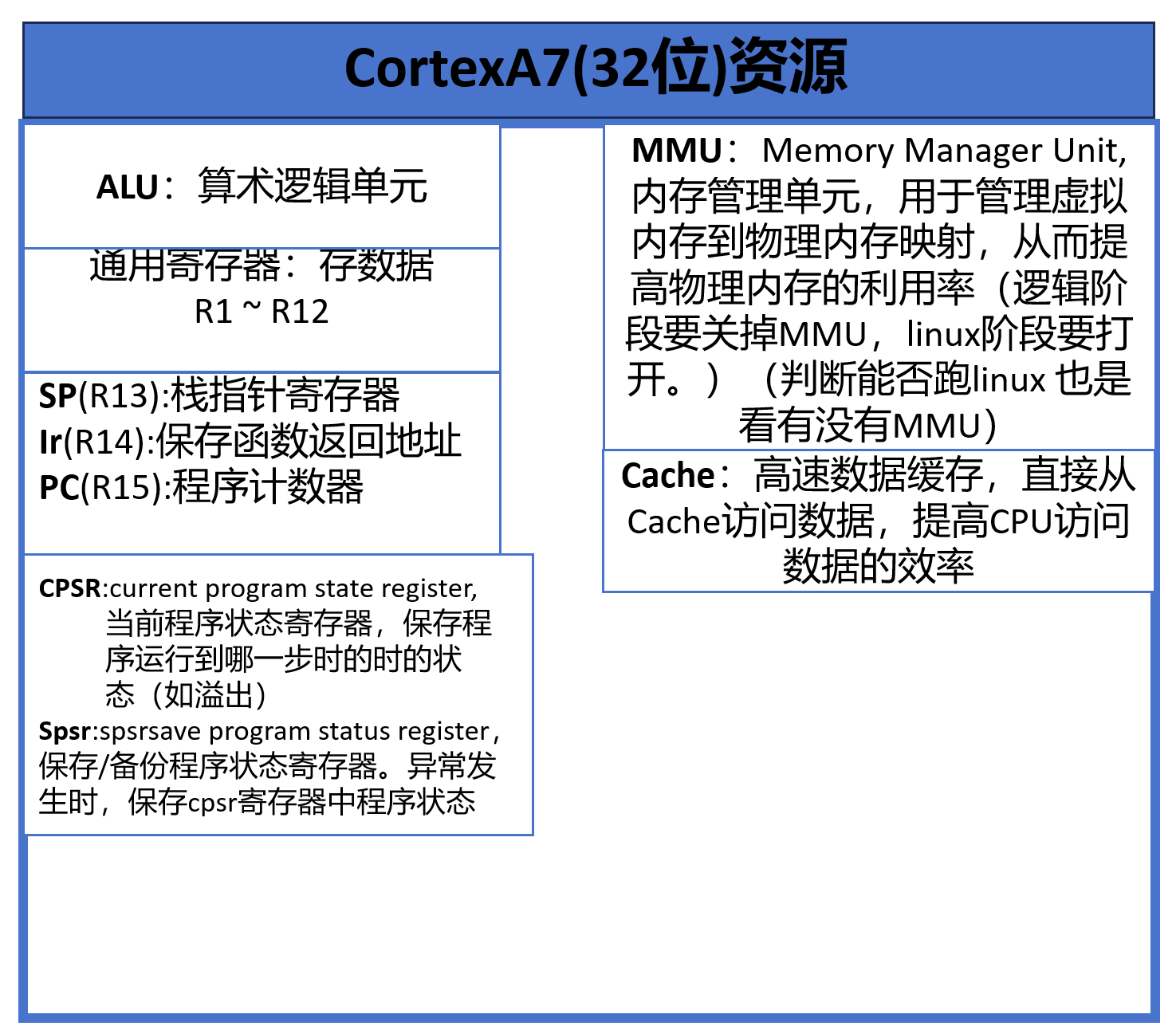

- **CortexA7(32位)**资源

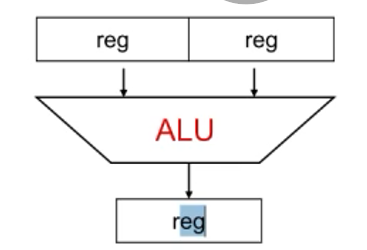

- ALU : Arithmetic Logical Unit,算术逻辑单元

- PC寄存器:program counter ,程序计数器,本质上是一个指针,指向当前代码正在执行指令的下一条指令

- 三级流水线结构 (同时做三件事,提速)

- PC :取指令

- 译码器:解释

- kernel:执行指令

- Lr寄存器 :Linked register,链接寄存器,保存函数返回地址(函数调用完跳回哪里)

- sp寄存器:stack pointer,栈指针寄存器,管理栈区,永远指向栈顶

- Cache:高速数据缓存,直接从Cache访问数据,提高CPU访问数据的效率

- icache: instruction cache,指令缓存, 存指令(加速取代码)

- dcache: data cache,数据缓存,存数据(加速读数据)

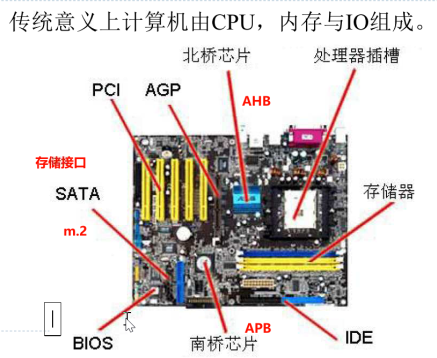

- 计算机架构

- 冯.诺依曼架构:数据和指令存放在同一片内存空间

- 哈佛架构 :指令、数据分开存储(速度更快,ARM / 单片机常用)

- 裸机开发黄金规则:必须要关闭MMU(裸机阶段使用物理内存,用不到虚拟内存),打开icache,关闭dcache

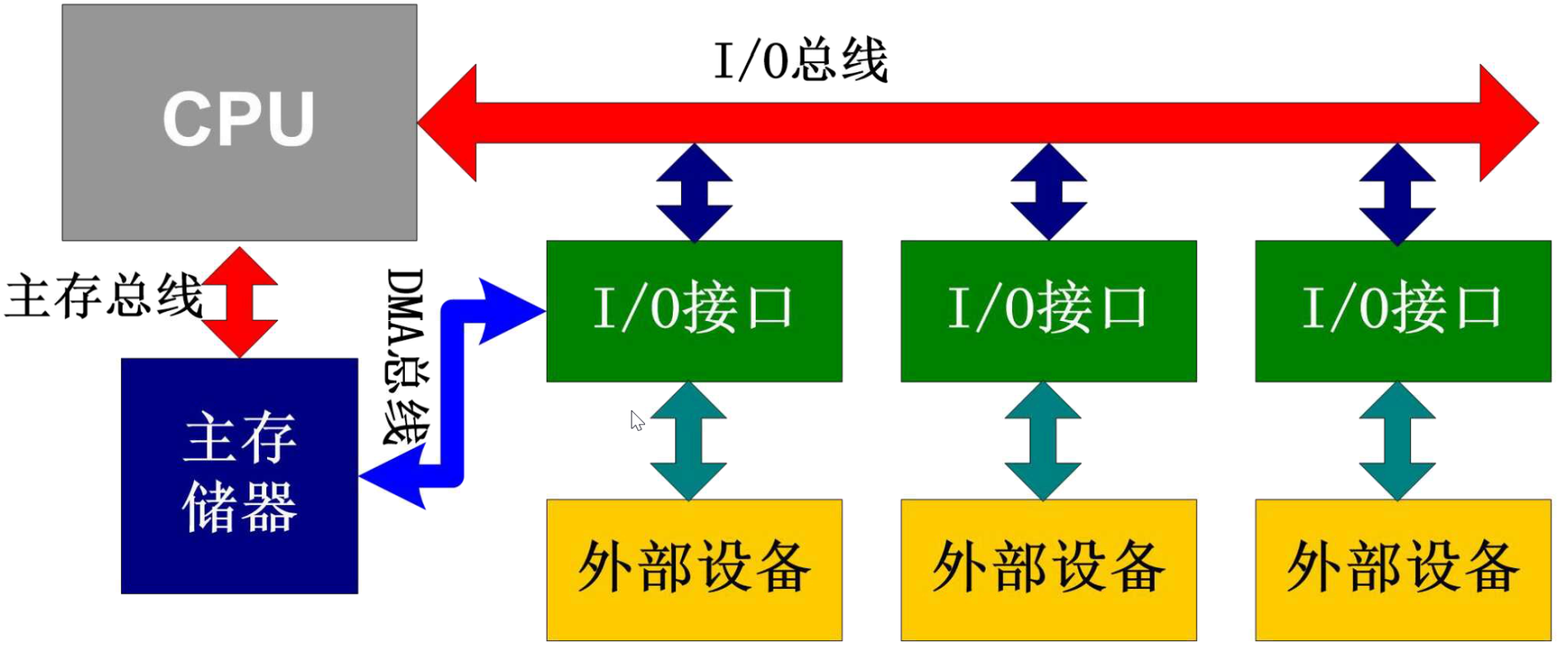

- 总线通信 (芯片内部 "高速公路"):

- 单总线通信:通过一根线/一组线和外设通信,同一时间只能和一个设备通信(排队)

- 双总线通信:

- AHB总线:advanced high bus,先进高速总线,连接高速外设(USB、网卡、RAM、北桥芯片)(跑得快)

- APB总线:先进外设总线(GPIO、UART、蓝桥芯片)(慢但够用)

- SATA:古老的硬盘接口

- 启动相关

- BIOS:引导Windows系统启动,把操作系统从flash搬运到内存

- bootloder:引导Linux系统启动的程序

-

SOC概念:System on Chip,r简称Soc,也即片上系统。

-

典型的SOC处理器

- 8051

- DSP:用于浮点运算

- MIPS

- PPC:上世纪90年代使用的

- ARM:嵌入式用得最多(付费)

- RISC-V:和ARM类似,但免费开源

-

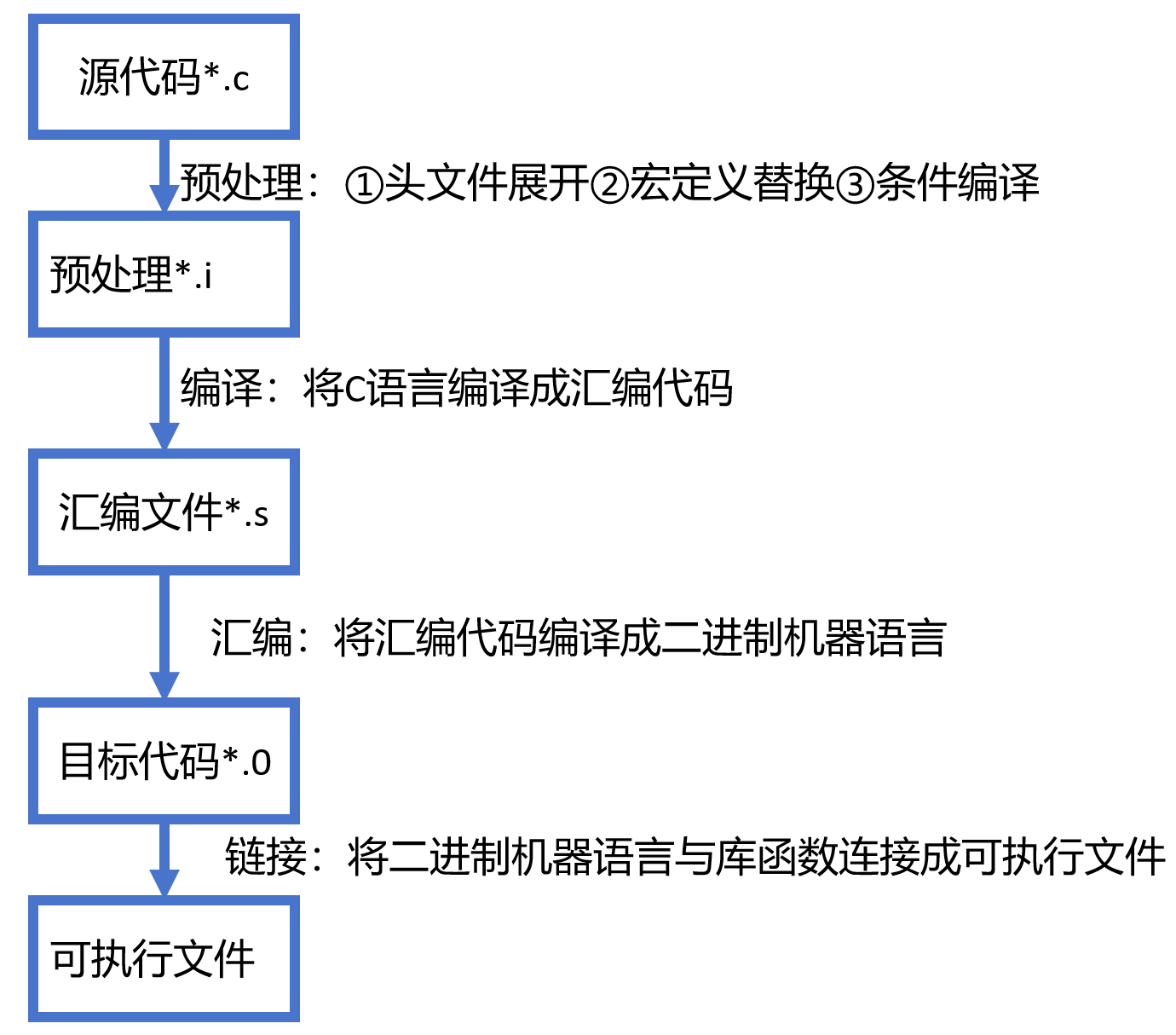

编译4流程:预处理(Pre-Processing),编译(Compliling),汇编(Assembling),链接(Linking)

-

开发ARM程序常用的集成开发环境

- 编译器

- gcc 用于x86架构

- arm-linux-gnueabihf-gcc 用于arm架构,交叉编译 ARM 程序 (uname -a 查看处理器架构)

- keil4:用于仿真,学习内核(S3C2440仿真模拟ARM920T)

- 编译器

-

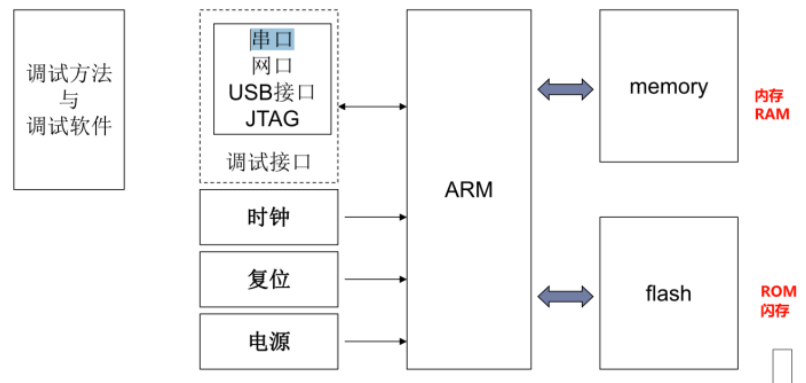

ARM最小系统 :

- 概念:使系统能够正常工作的最少器件构成的系统

- 图示 :

-

三总线结构:

- ARM数据类型 (32 位架构标准)

- ARM 约定:

Byte : 8 bits

Halfword :16 bits (2 byte)

Word :32 bits (4 byte)

Doubleword :64-bits(8byte)(Cortex-A处理器)

- ARM 约定:

- ARM指令类型

- 大部分ARM core 提供:

- ARM指令集(32-bit)

- Thumb指令集(16-bit)(压缩指令,省空间)

- Cortex-A处理器

- 16位和32位Thumb-2指令集:混合 16/32 位(现代 ARM 用)

- 16位和32位ThumbEE指令集

- Jazelle cores 支持 Java bytecode

- 大部分ARM core 提供:

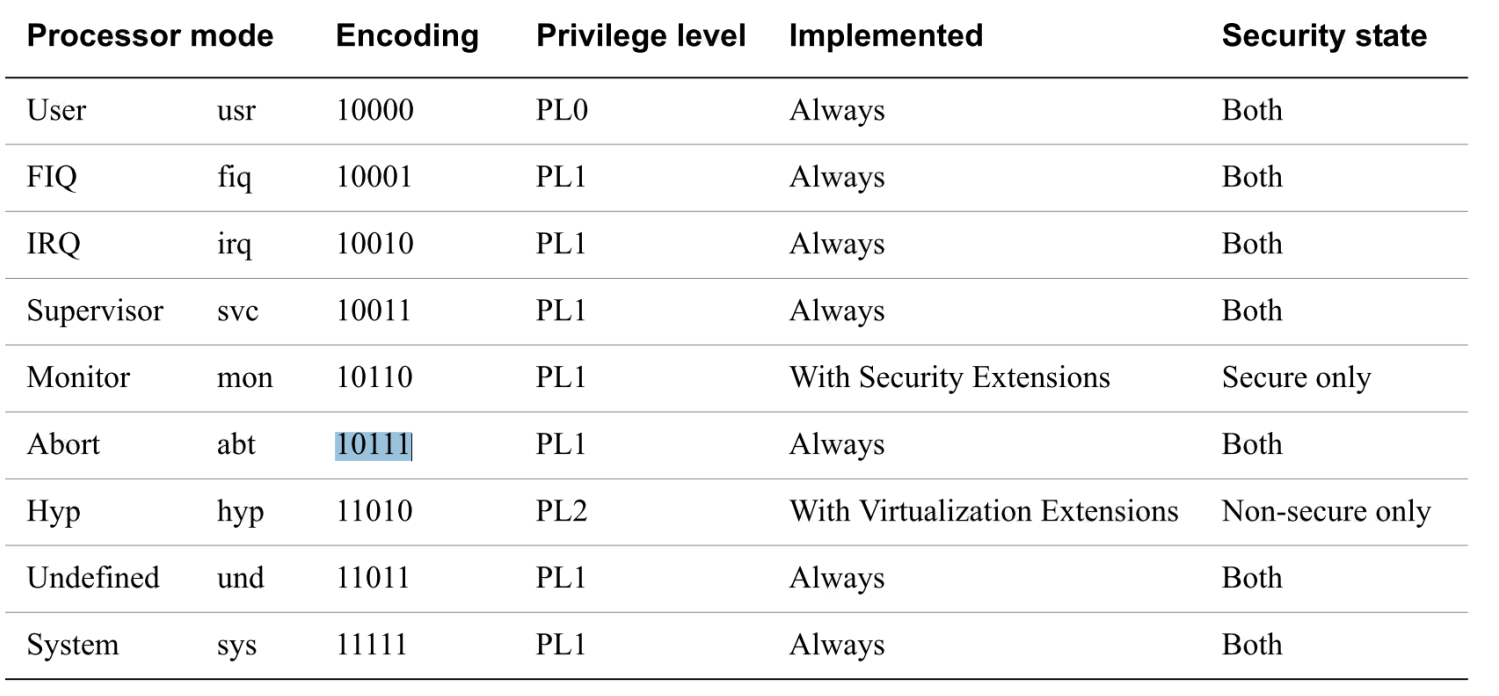

- 处理器工作模式

- ARM有7个基本 工作模式(特权 / 非特权)

- User :非特权模式,++大部分任务执行在这种模式++(权限最低)

- FIQ:当一个高优先级(fast)中断产生时将会进入这种模式

- IRQ:当一个低优先级(normal)中断产生时将会进入这种模式

- SupQervisor:管理员模式、默认模式,当复位或软中断指令执行时将会进入这种模式

- Abort :当++存取异常++时将会进入这种模式()

- Undef: 当执行++未定义指令时++会进入这种模式

- System :特权模式、使用和User模式相同寄存器集的特权模式Cortex-A

- Cortex-A特有模式: 用于调试------专用安全模式

- Monitor:是为了安全而扩展出的用于执行安全监控代码的模式;也是一种特权模式------专用安全模式

- ARM有7个基本 工作模式(特权 / 非特权)

- 切换处理器工作模式

- ARM寄存器个数

- ARM有37个32-Bits长的寄存器:1 个用作PC( program counter)、1个用作CPSR(current program status register)、5个用作SPSR(saved program status registers)、30个通用寄存器)

- Cortex体系结构下有40个32-Bits长的寄存器

2.核心总结

①复杂指令集与精简指令集

②ARM版本:ARM 经典 → Cortex-A/R/M

③16个通用寄存器,cpsr,spsr,MMU,cache缓存,

③裸机阶段:必须要关闭MMU,打开icache,关闭dcache

④单总线,多总线

⑤flash闪存,新一代非易失性存储器

nor flash:每个字节可寻址

еMMC nand fkash:以块为单位寻址

⑥ARM7种工作模式

⑦ARM寄存器个数------ARM有37个32-Bits长的寄存器、Cortex体系结构下有40个32-Bits长的寄存器

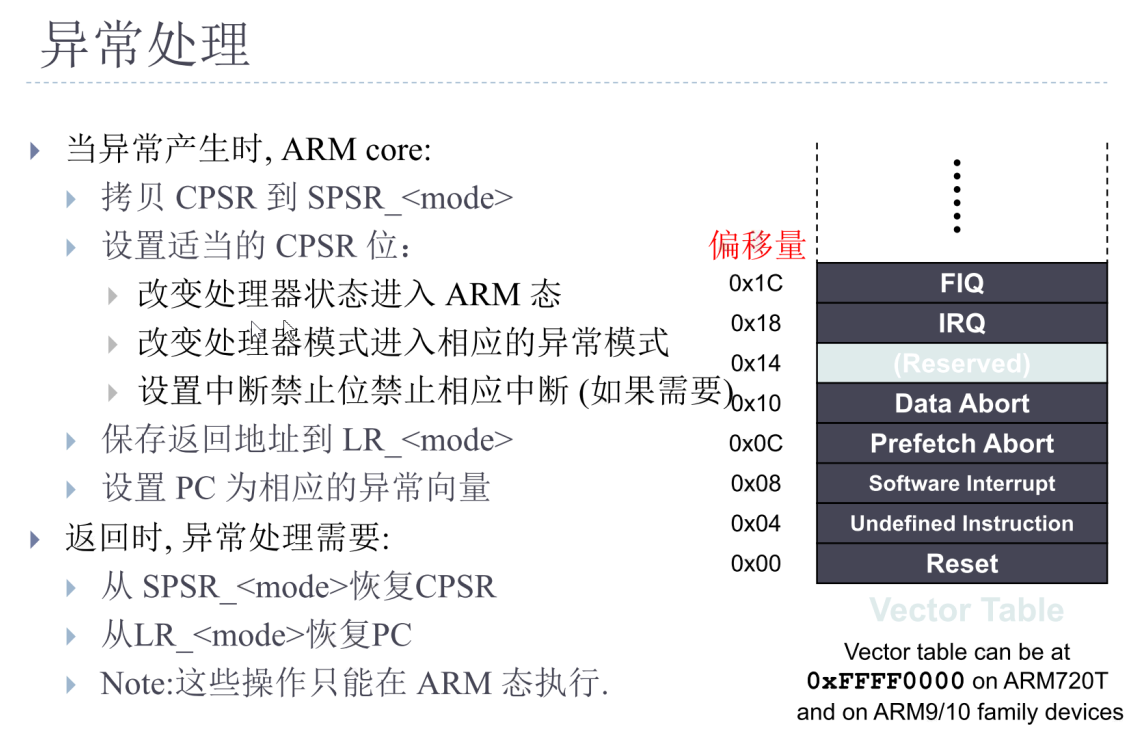

⑧异常处理流程