一、概述

本章节利用FPGA模拟EEPROM的从机响应程序,并创建hex文件写入EDID编码。

二、设计流程

我们可以在FPGA利用代码模拟EEPROM的响应程序,给HDMI主机返回正确的EDID编码。FPGA端把预设的EDID储存在片上ROM中,根据HDMI主机发送的IIC读写请求信号,利用IIC通信标准的时序将主机所读取的EDID编码传输给电脑端。电脑端接收到正确的EDID编码后,就会通过HDMI输出端口,输出所选尺寸的视频输出。该视频输入到FPGA开发板后,经过解码,编码再输出,最后在显示屏上显示出所输出的画面。

三、获取EDID编码

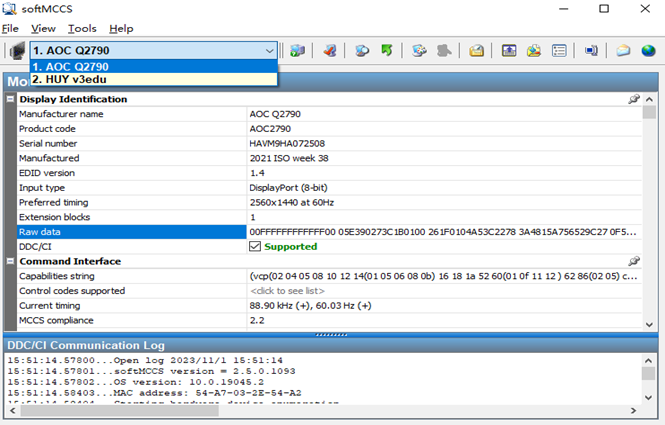

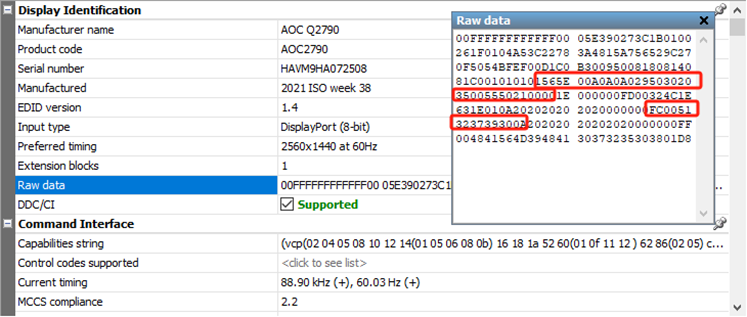

为了获取显示器的原EDID信息,这里提供了一款softMCCS软件,打开软件后左上方的位置可以选择显示器,(如果主机只连接一个显示器就只有一个选项)。里面也可以看到显示器的信息,其中Raw data就是该显示器的EDID内容,点击右边数据可以看到具体的EDID编码。这里只显示了128位的基础EDID内容,不过我们也不用关心扩展的EDID信息。

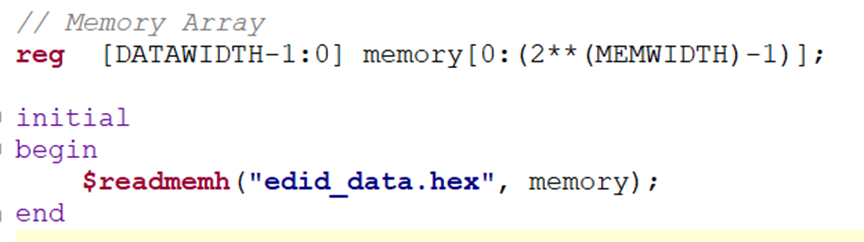

接下来可以先修改显示器的名称和推荐分辨率的编码内容。H36-H47位置为推荐分辨率,00 00 00 FC 00这5个字节是显示器名称的标志,后边的编码内容为显示器名称,根据ASCII码修改,共13位。倒数第二个字节为扩展标识,因为我们没有用到扩展码,所以扩展标志设置为00。最后一个字节的校验码再进行计算修改。到此我们的EDID内容已经修改完毕,接下来要把修改完的EDID编码储存在hex文件中,初始化加载到自定义的ROM模块中。利用'"$readmemh"语句即可将hex文件中的数据初始化到内存阵列中。

hex文件中的编码内容按照一个字节一行,顺序进行排列。ROM模块如下所示:

module BRAM

#( parameter MEMWIDTH = 8, //256 * data

parameter DATAWIDTH = 32

) // Size = 32KB

(

input wire clk,

input wire wen,

input wire [MEMWIDTH-1:0] waddr,

input wire [MEMWIDTH-1:0] raddr,

input wire [DATAWIDTH-1:0] data_in,

output reg [DATAWIDTH-1:0] data_out

);

// Memory Array

reg [DATAWIDTH-1:0] memory[0:((2**(MEMWIDTH))-1)];

initial

begin

$readmemh("edid_data.hex", memory);

end

always@(posedge clk)

begin

if(wen)

memory[waddr] <= data_in;

end

always@(posedge clk)

begin

data_out <= memory[raddr];

end

endmodule

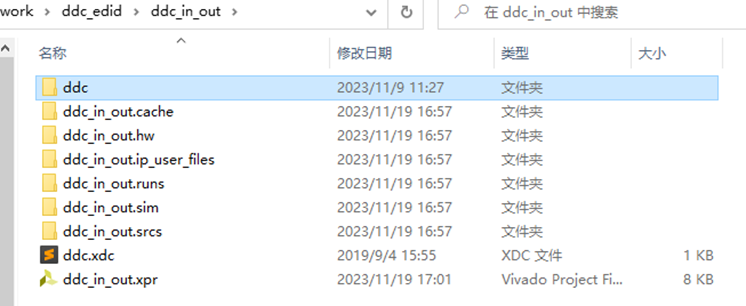

工程中添加hex文件:

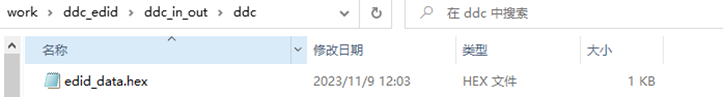

在工程文件里创建一个新的文件夹:

文件夹中创建hex文件:

文件夹中创建hex文件:

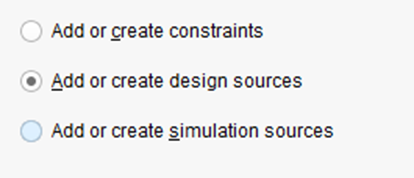

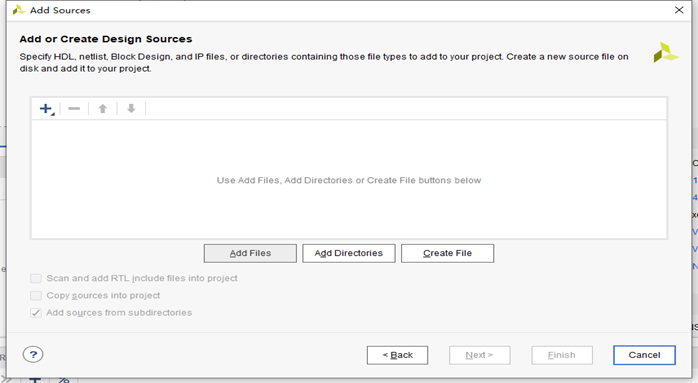

vivado工程中添加设计文件:

添加已创建文件:

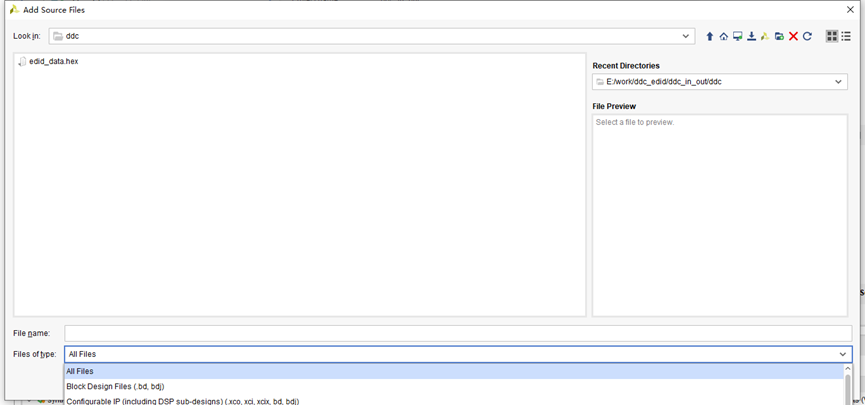

文件类型选择所有类型,点击hex文件并确认:

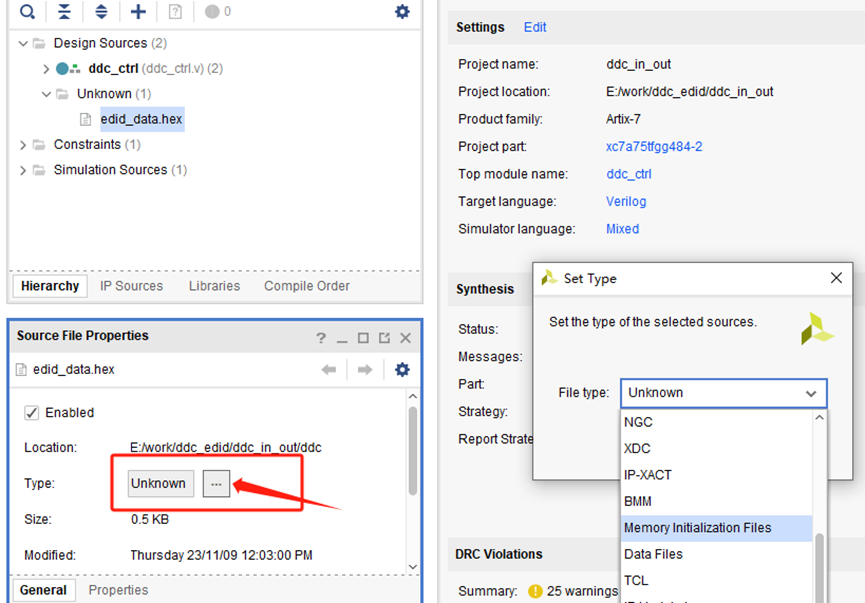

在vivado工程中选中hex文件,在源文件属性框里选择类型Memory initialization files。

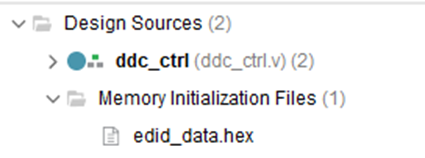

添加hex文件后文件目录如下:

四、总结

现在EDID已经可以存储到rom中,之后的章节来使用仿真模拟主机发送IIC读时序,来验证FPGA端发送的EDID信息。电脑端接收到正确的EDD编码后,会通过HDMI将显示器的视频输出到fpga,视频流经过FPGA后再输出到另一个显示器上。

本文章由威三学社出品

对课程感兴趣可以私信联系