AFE5832的初始化流程:

AFE5832使用比AD9253复杂,因为AFE5832集成功能更复杂,所以AFE5832必须要使用spi去读写控制其寄存器,像很多tgc增益等等的高级复杂的功能的设置,都必须通过spi接口去修改寄存器实现;

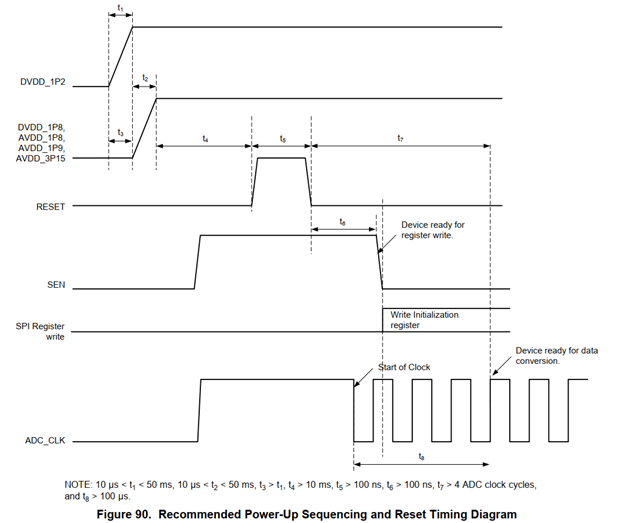

上图为芯片上电时序图,

在上电后,首先需要RESET管脚,复位拉高至少100ns,

然后至少等待100us以上,等待ADC时钟等状态稳定,才能进行SPI读写等操作;

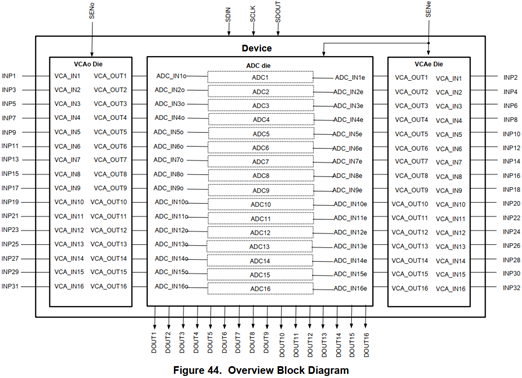

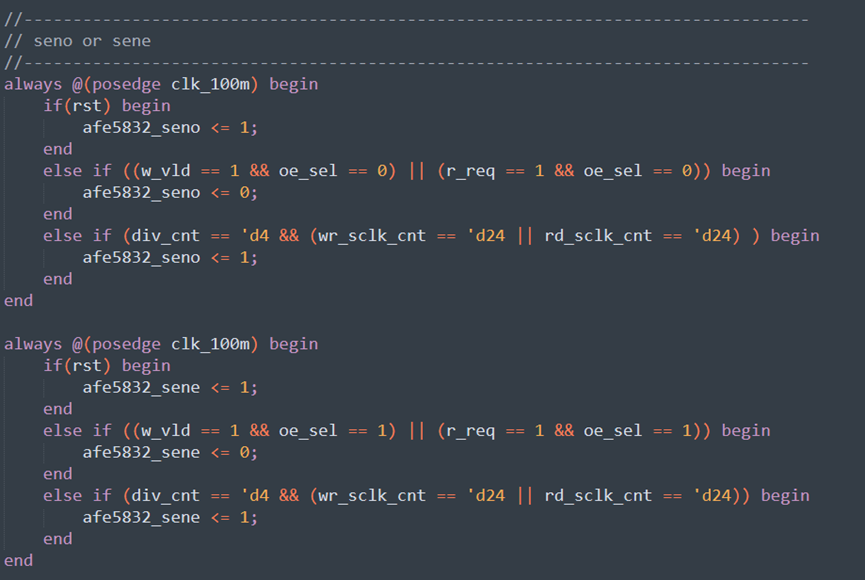

且由于AFE5832有两组Die,然后spi读写时片选分为seno和sene分别选择其中一个die,所以在初始化时,还需要对两组die分别操作,

在上电完成后,要进行芯片的初始化:

在复位完成后等待100us以上,

首先控制VCAo Die的寄存器读写,

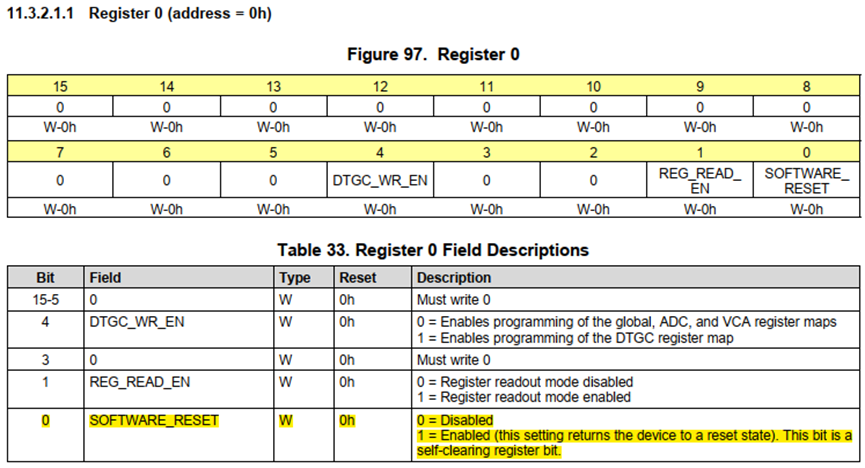

给下图中地址为0的寄存器的bit0置1,软复位一下,该复位值会自动清零,

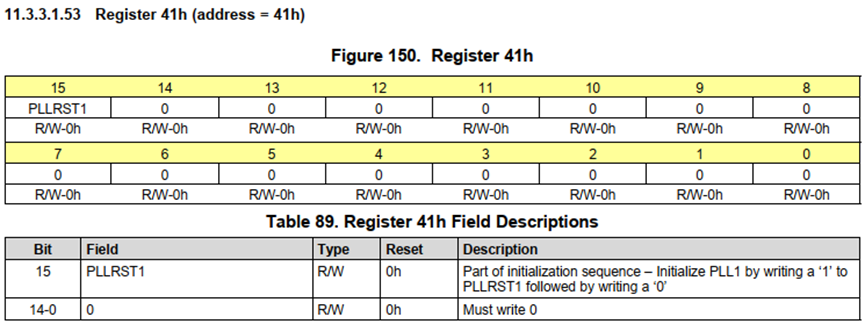

然后要初始化PLL,

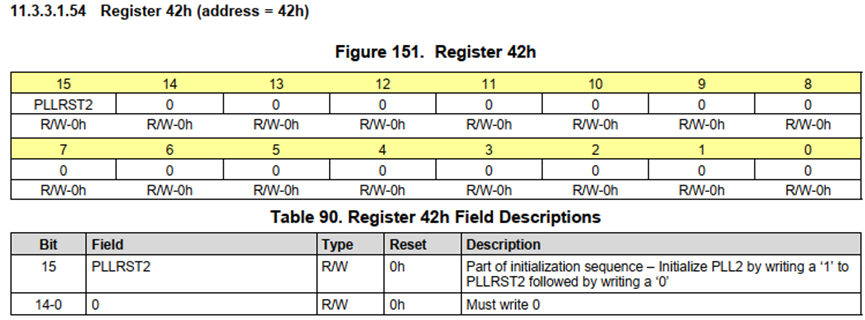

给寄存器地址为0x41和0x42的pllrst1和pllrst2寄存器的bit15置1复位,且在置1复位后,等待10us,再将两个寄存器该位其置0手动清楚复位值,

PLL复位后,

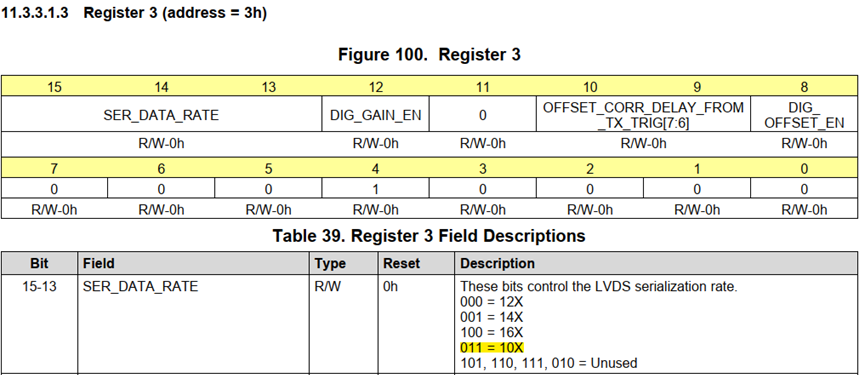

设置ADC的串行化因子,向寄存器地址3中,向比特15-13中写入011选择10x的序列化因子,

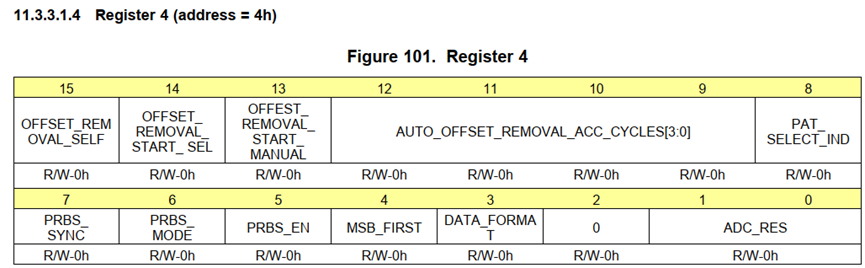

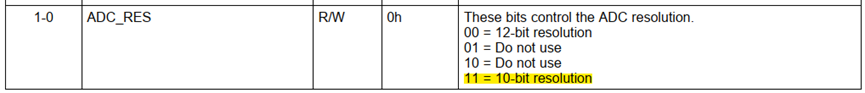

设置ADC的分辨率,向寄存器地址4中,向比特1-0中写入11选择10bit分辨率,

然后在VCAo Die的寄存器读写pllrst复位和ADC设置后,重复上述操作对VCAe Die再进行一次,

最后寄存器配置完毕后,把TX_TRIG管脚,拉高10ns,用于单个或多个AFE5832同步奇偶输入的采样瞬间;

都配置完成后,LVDS接口一般就可以正常输出数据了,FPGA就可以开始对数据进行解串处理等操作了;

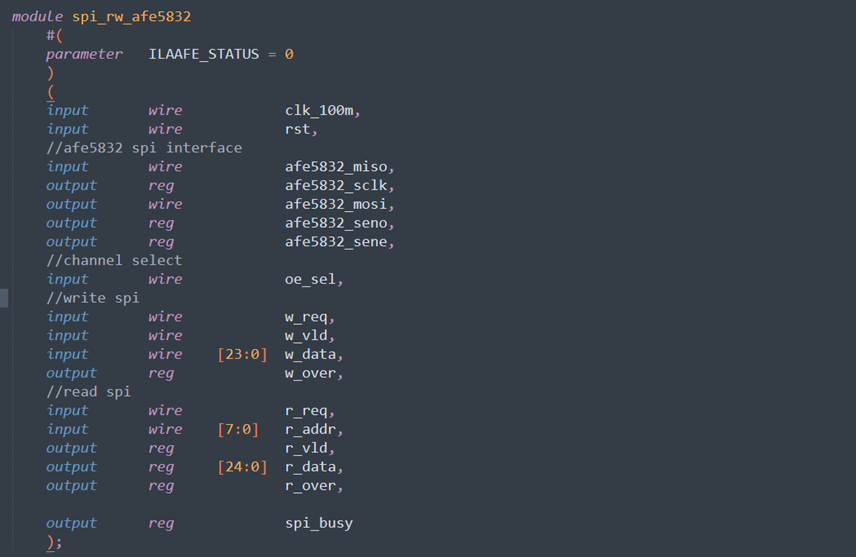

实现SPI接口时,

注意spi接口还分有两根cs选中线,分别控制两个die;

本文章由威三学社出品

对课程感兴趣可以私信联系