xilinx的fir compiler IP支持整数、小数的内插和抽取。对于整数倍内插和抽取,都比较好理解。本文主要介绍小数倍内插。

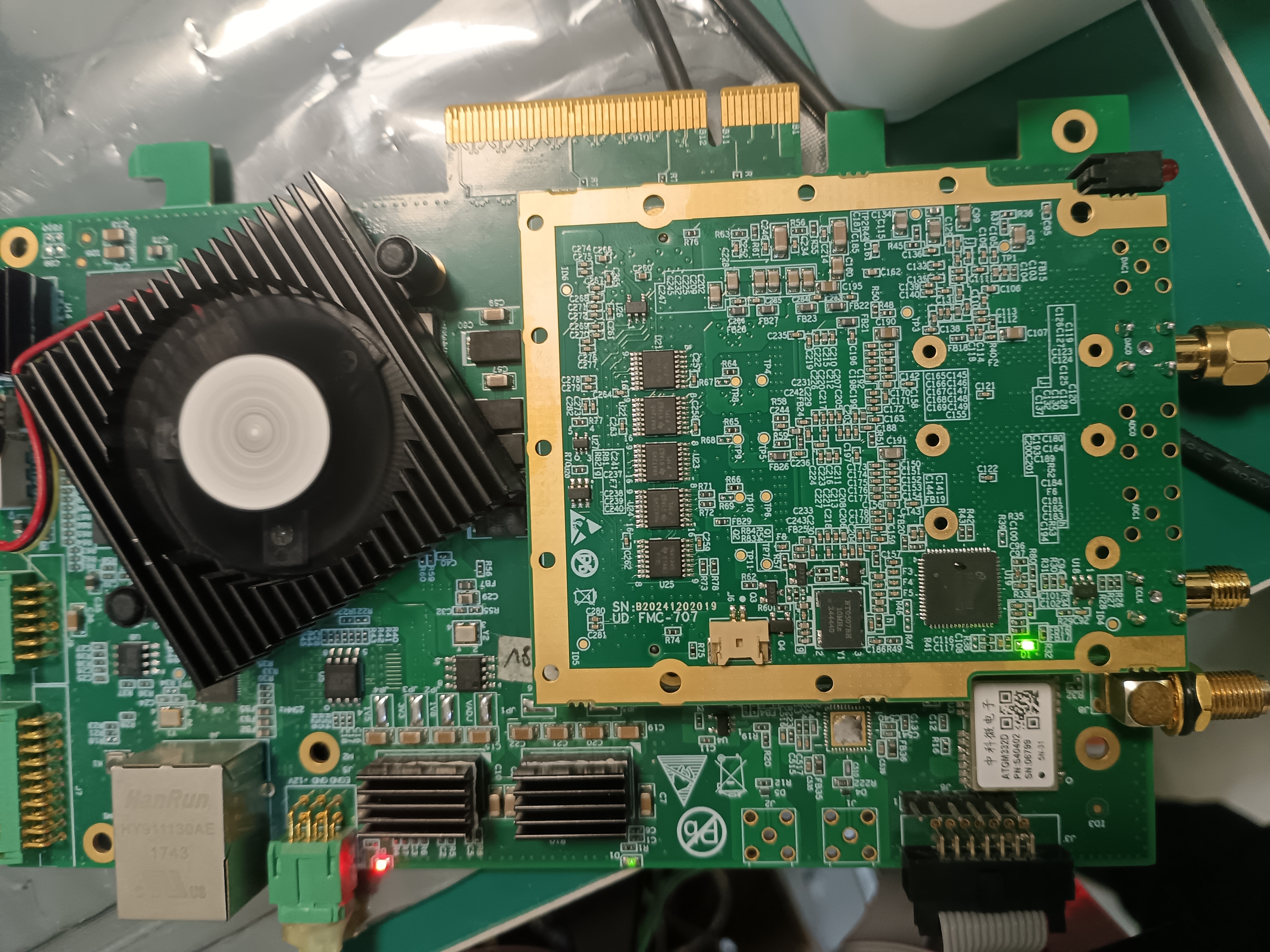

测试中,使用优数科技的FMC-707采集回放板卡。该板卡支持2通道250M@16bit的采集和2通道12G@16bit的回放,使用LMK04828 PLL芯片,支持全国产化。

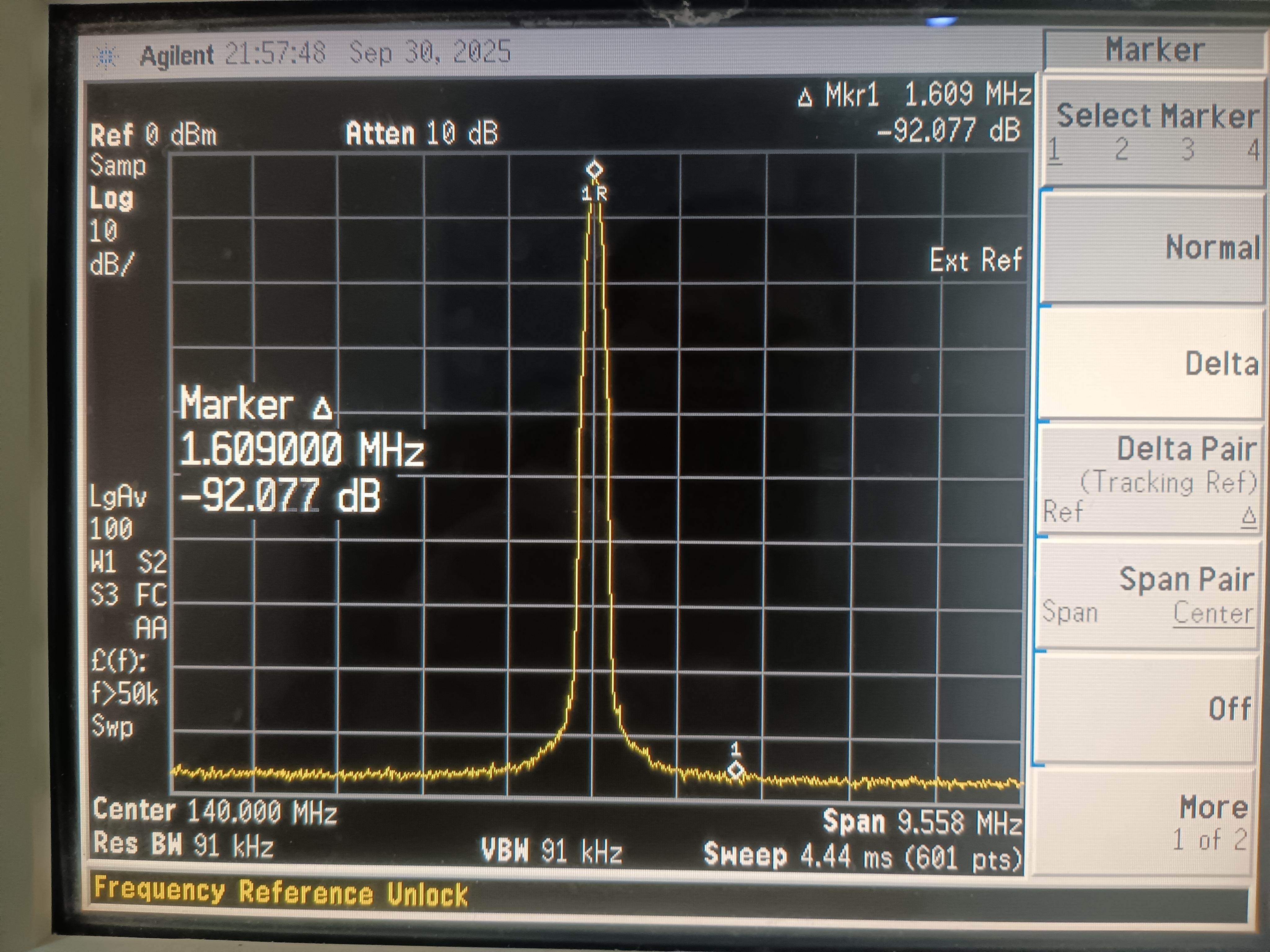

客户的需求为:采集通道中心频率为140MHz,带宽为80MHz,采样率为186.66MHz,回放也希望同样的速率。

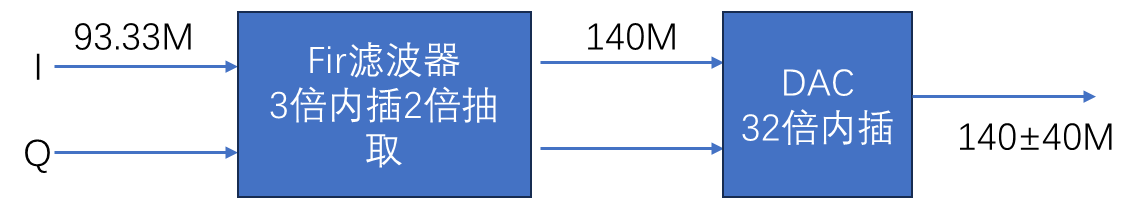

本文只介绍da回放的设计:

由于板载内参考时钟为10MHz,VCXO为100MHz,LMK04828的VCO频率范围VCO0(2370 to 2630 MHz), VCO1(2920 to 3080 MHz),不能直接输出186.66MHz的频率,但是可以输出140/280MHz的频率。

FPGA内,调用DCM,把LMK04828输出的140变为93.33MHz,然后再经过小数倍内插和抽取滤波器,送到DAC芯片,DAC芯片内部32倍内插后输出140±40MHz的中频信号。

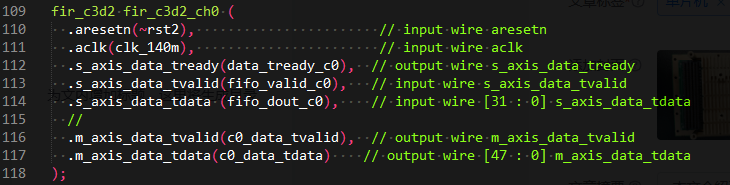

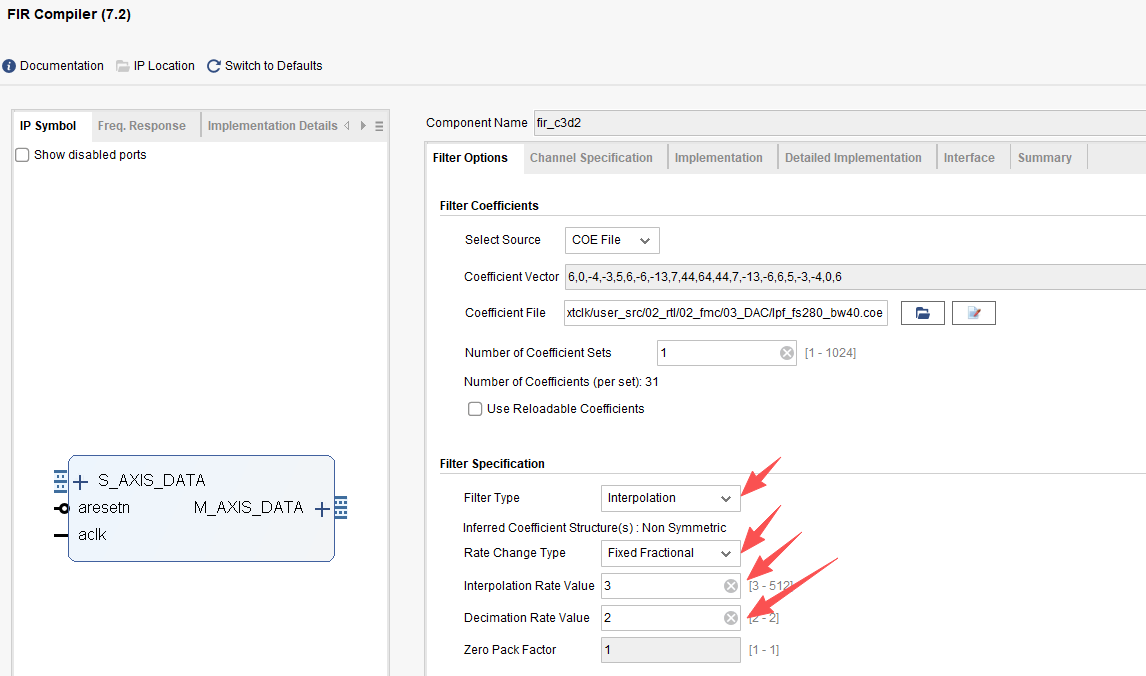

比较容易搞错的是FIR的Fixed Fractional内插interpolation的IP参数。

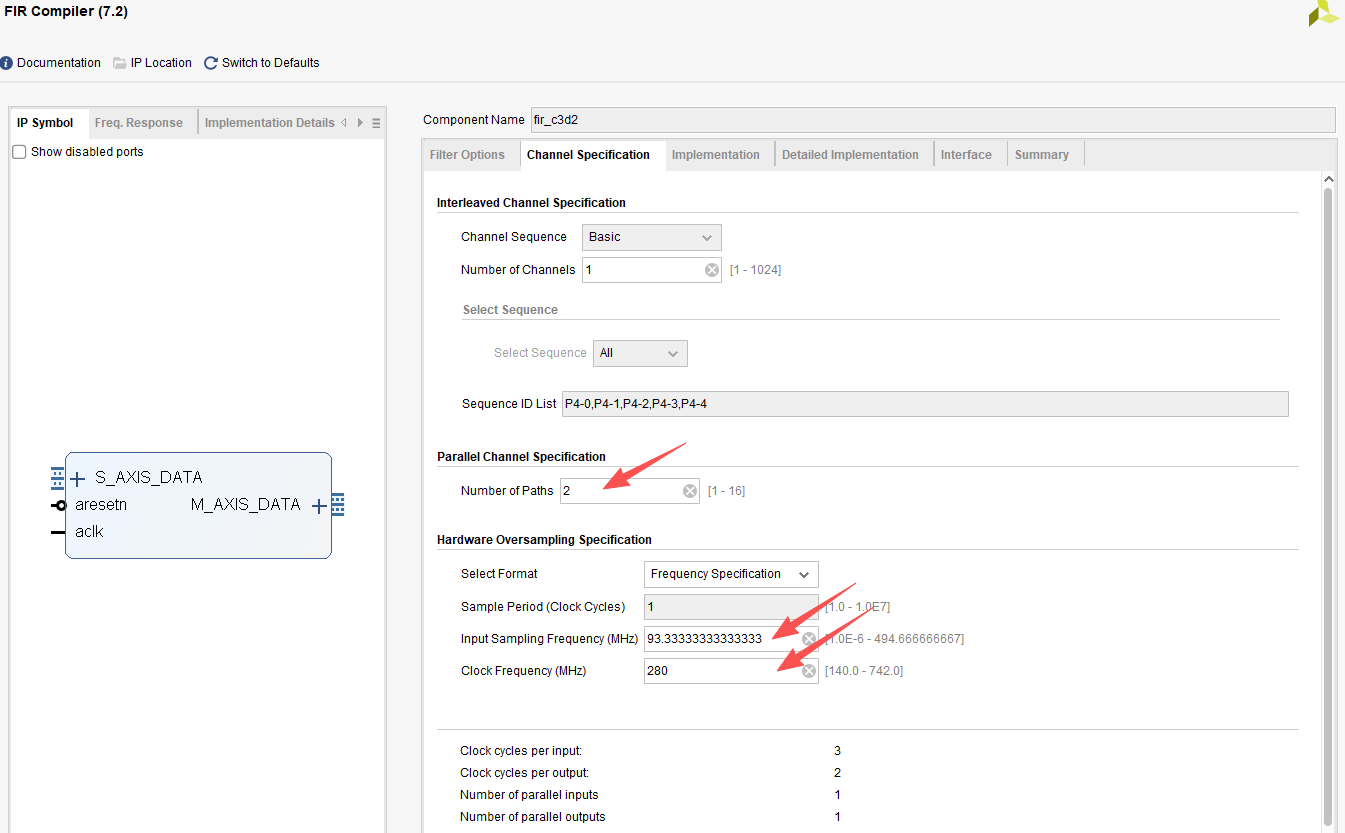

上图选择Fixed Fractional,3倍内插2倍抽取。

通道数设置为:因为是IQ,例化1个滤波器IP就够了;

输入的数据速率是93.33MH,时钟频率给280MHz(3倍93.333MHz);

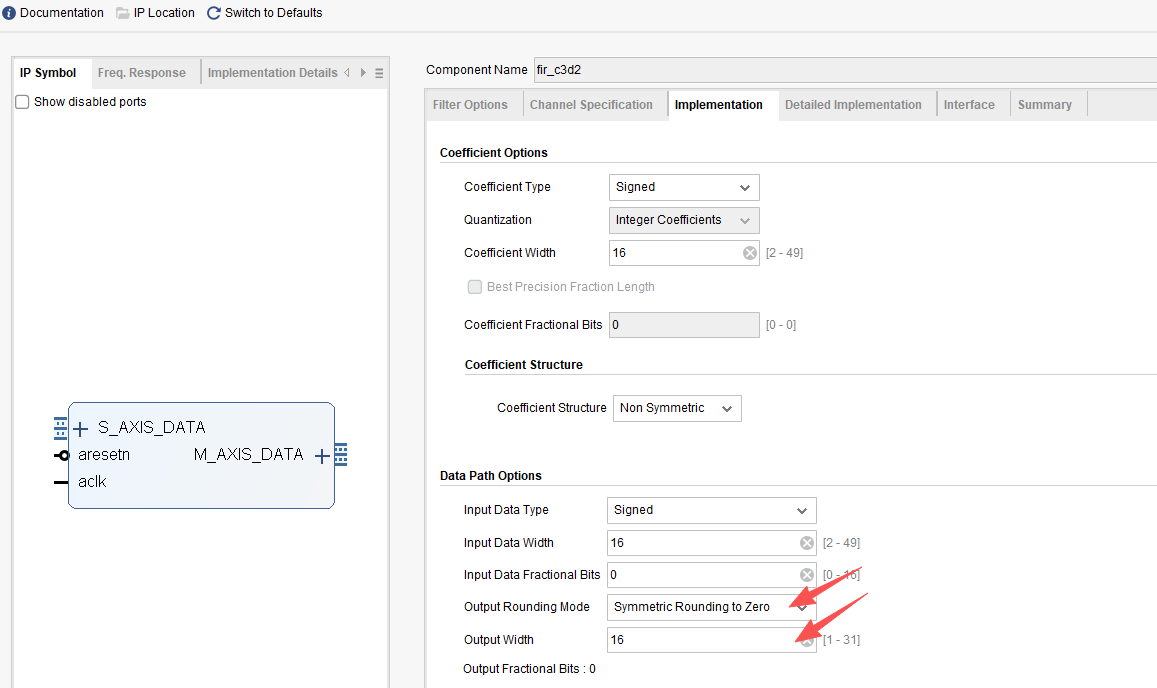

输出IP自动截位了。

需要注意的是滤波器系数设置:

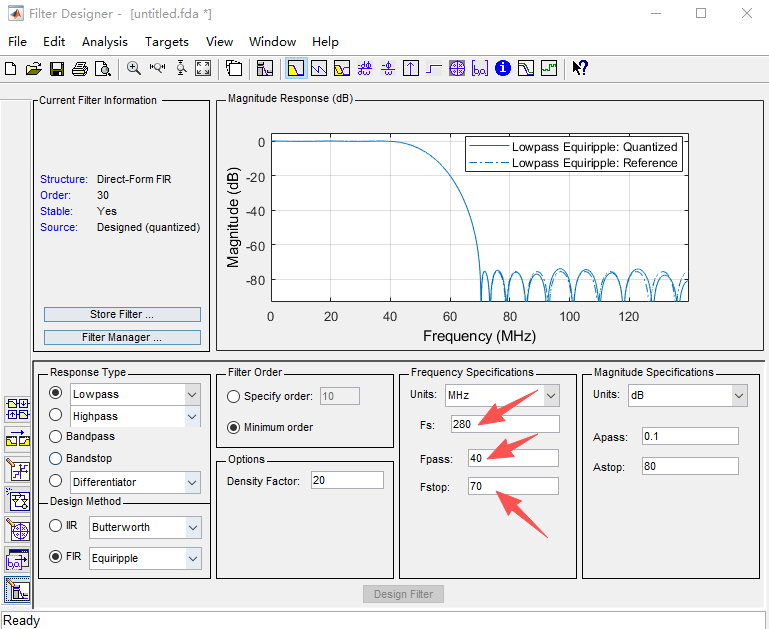

Fs为插值后的速率(280MHz),通带频率为抽取后的通带(40MHz),Fstop不超过输出速率的1/2(140MHz/2=70MHz)。

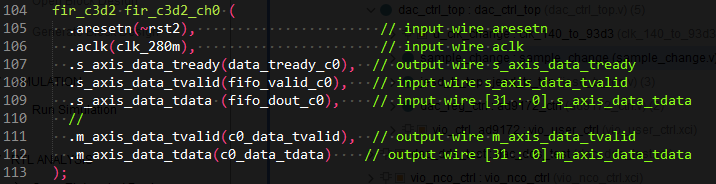

由于基带IQ输入的速率为93.33MHz,而Fir滤波器的时钟频率又是280MHz,故此处要通过一个FIFO,并且3个时钟周期间隔去fifo中取一个数据。

DAC芯片采用双link,模式0,每个通道1个lane。dac芯片内插32倍,dac输出速率为4.48Gsps,lane速率为5.6Gbps。

把IP的时钟频率从280M修改为140MHz进行测试,IP仍然工作正常: