关于焊点检测(SJ-BIST)模块实现

语言 :Verilg HDL 、VHDL

EDA工具:ISE、Vivado、Quartus II

-

-

- 关于焊点检测(SJ-BIST)模块实现

-

- 一、引言

- 二、焊点检测功能的实现方法

-

- [(1) 输入接口](#(1) 输入接口)

- [(2) 输出接口](#(2) 输出接口)

- [(3) 模块实现核心状态图](#(3) 模块实现核心状态图)

- [(4) 模块实现原理图](#(4) 模块实现原理图)

-

-

关键词: Verilog HDL,焊点检测功能

一、引言

本文使用FPGA实现焊点检测功能。

二、焊点检测功能的实现方法

(1) 输入接口

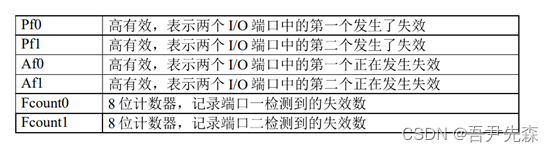

(2) 输出接口

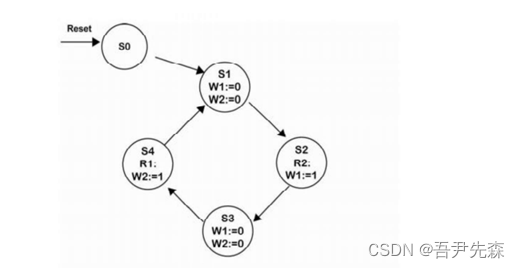

(3) 模块实现核心状态图

如上图表示两端口 SJ-BIST 的状态图。上图所示的循环用来写一系列可转换的1和0,一个1和0通过一个端口,然后穿过另一个I/O 端口。从一个端口输出一个1会导致从另一个端口读一个 1。否则,读入一个逻辑 0表示一个焊接点在这个点受到了伤害,以致一个足够严重和持续时间足够长的高阻失效已经发生,并已经导致了写操作的失败。

下面描述每个状态及每个状态的动作:

1.S 是复位状态。

2.状态 S2 和 S4 用来写逻辑 1并且读取外部电容信号

3.状态 S1和 S3 用来写逻辑 0 并清除外部电容。

4.转台 S2 和 S4 用来检测失效:

a) 如果读入的不是逻辑 1,用来写逻辑 1的I/0 端口发生了一个高阻失效。

b) 但一个失效发生时,更新这个 i/o 端口的失效计数。然而,如果这个i/o端口已经处在一个激活的失效状态,不更新失效计数,把这个失效作为前一个失效的延续。

如果读入的是一个逻辑 1,用来写逻辑 1的相应的I/ 端口是无错的;复位这个端口的活动失效信号。复位可以在任何状态发生,并会强迫状态机转至状态 0,清除失效计数及失效标识。

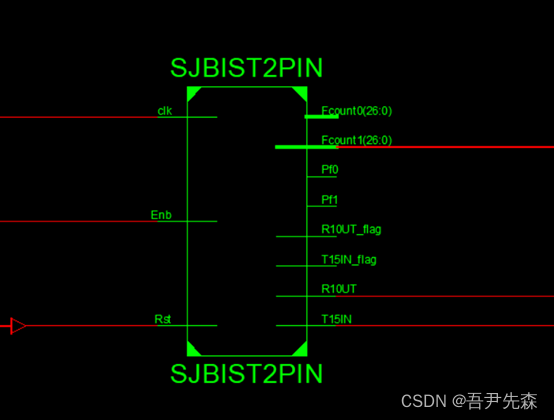

(4) 模块实现原理图

如下图所示是模块实现原理图