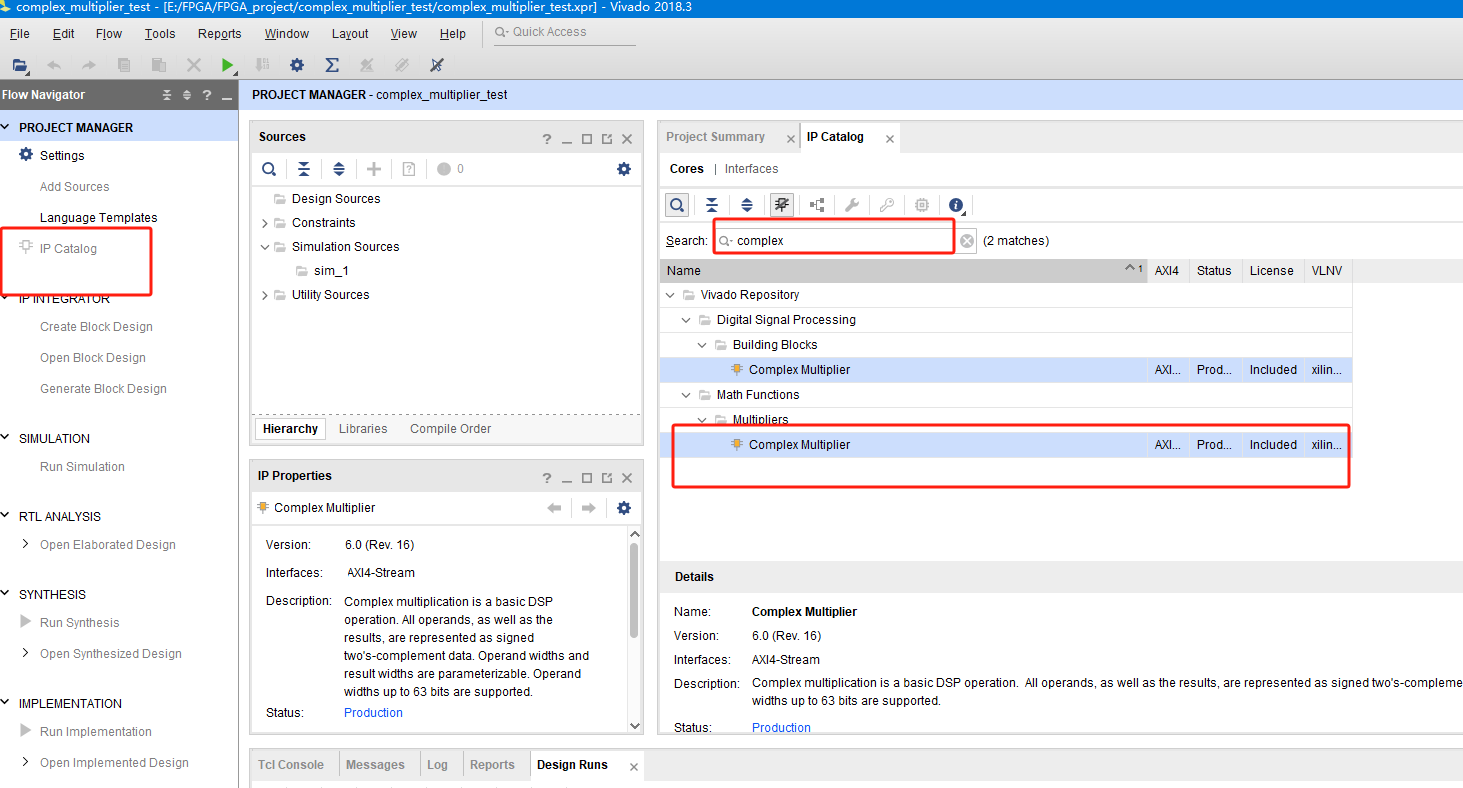

一、IP核解析

这一部分参考自:FPGA IP之算数运算IP(1)_哔哩哔哩_bilibili

IP核设置也是先僵硬复制up主的配置,后续再灵活变通。

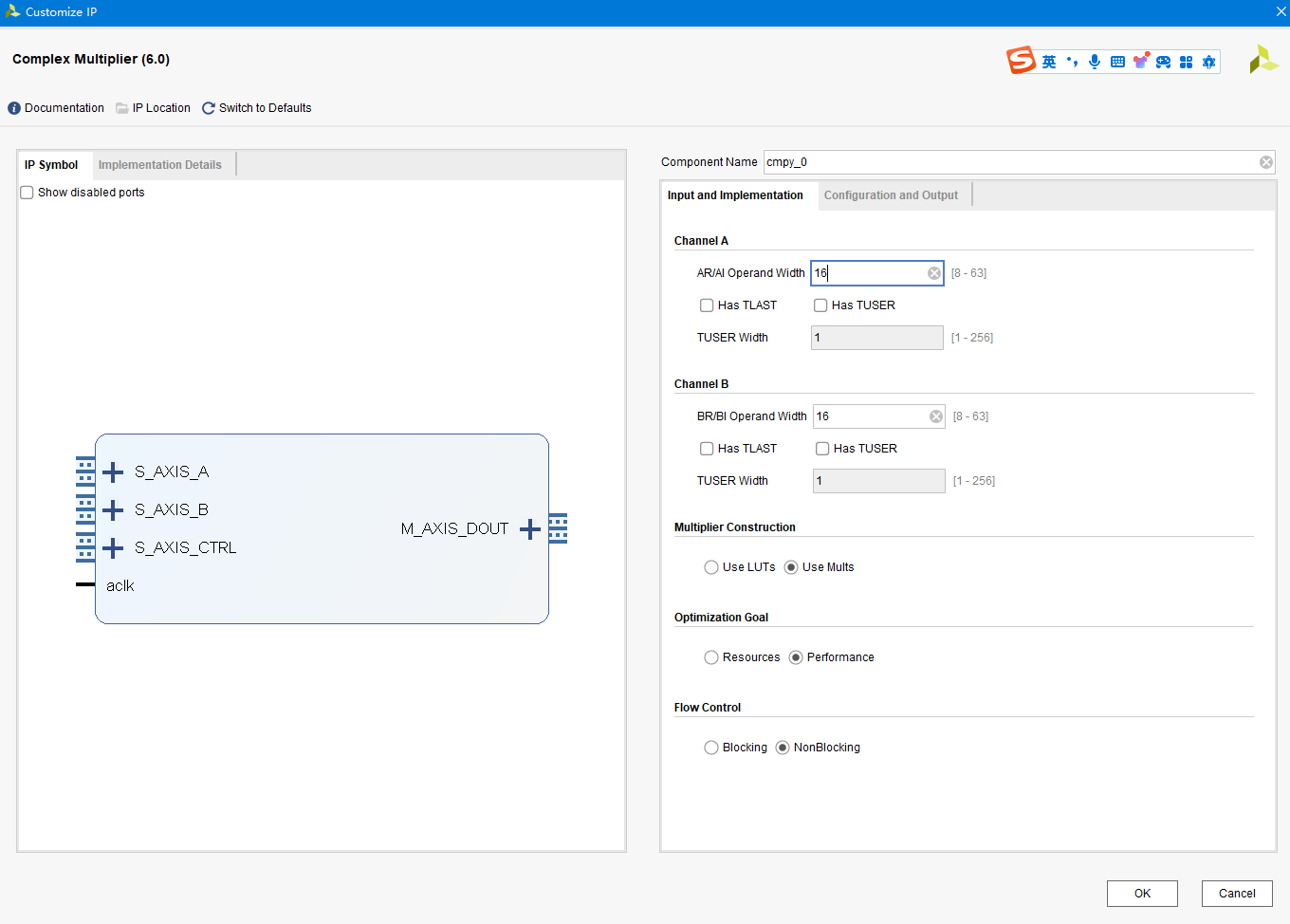

在这张图片中,我们看到的是一个"Complex Multiplier (6.0)" IP 核的配置界面。以下是各个配置参数的详细说明:

1.1 Multiplier Construction

Use LUTs: 选择这个选项时,乘法器将使用查找表(LUTs)来实现。这种方法通常适用于较小的操作数位宽,因为它在资源和速度之间提供了一种折衷方案。

Use Mults: 选择这个选项时,乘法器将使用DSP资源来实现。这种方法通常适用于较大的操作数位宽,因为它更高效。

1.2 Optimization Goal

Resources: 选择这个选项时,IP核会优先优化资源利用率,即尽可能少地使用FPGA的硬件资源。

Performance: 选择这个选项时,IP核会优先优化性能,即尽可能提高数据处理速度。

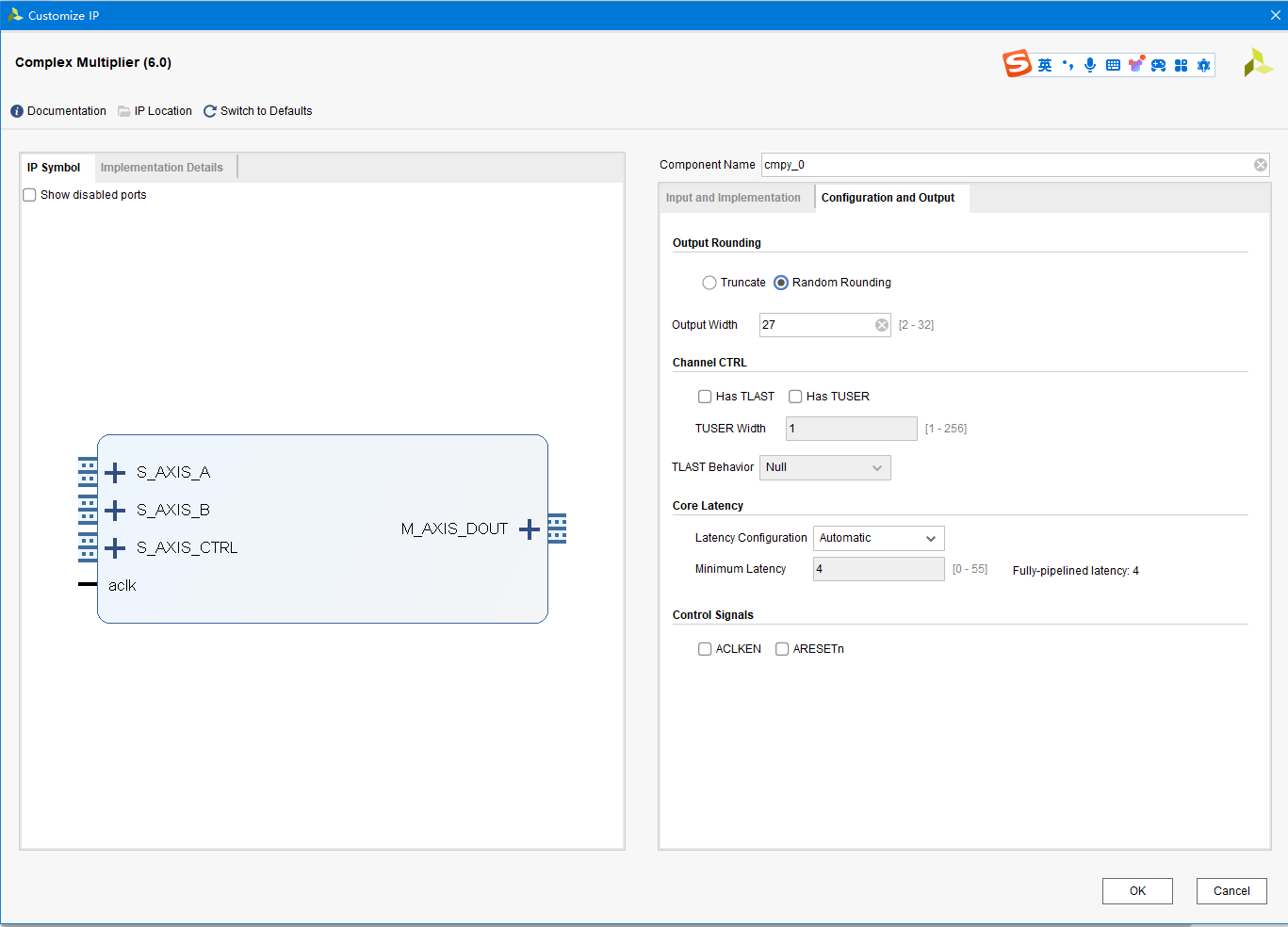

1.3 Output Rounding

Output Rounding 是指在进行乘法运算时,结果的尾数部分如何处理。由于乘法运算可能会产生比设定输出宽度更长的结果,需要对结果进行截断或舍入,以符合设定的输出宽度。

Random Rounding 是一种舍入方法,通过随机选择四舍五入或直接截断,来决定最终输出值。这种方法有助于在统计上减少舍入误差的偏差,特别是当需要处理大量数据时。

Truncate Truncate:选择这个选项时,超出输出宽度的部分会被直接截断(即丢弃),不进行舍入。这是最简单的一种处理方法,但可能会导致一定的舍入误差。

Output Width Output Width 是设置乘法运算结果的位宽。在这个例子中,设置为27位,范围在2到32位之间。这个参数决定了乘法器的输出数据的精度和FPGA资源的利用情况。