一 默认配置

在启动文件中,已经对时钟进行了初始化,默认按外部8M晶振,配置系统时钟为48MHZ,APB为系统时钟的2分频,为24MHZ。在system_ac780x.c文件中,可以找到下面这个系统初始化函数,里面有SetSysClock()函数,对时钟进行了初始化。

cs

void SystemInit (void)

{

#if defined (__VTOR_PRESENT) && (__VTOR_PRESENT == 1U)

SCB->VTOR = (uint32_t) &__Vectors;

#endif

SystemCoreClock = SYSTEM_CLOCK;

SetEflashClock();

SetSysClock();

CKGEN_SetAPBClockDivider(APBCLK_DIV);

//SPM_EnableLVD(DISABLE); //disable LVD if need

}如果需要配置不一样的时钟,可以通过系统文件里的宏定义修改,但并不建议在系统文件上修改,可以自己写配置函数。

二 时钟模块简介

1.时钟源:

高速内部时钟(HSI):内部 RC 振荡器提供 8MHz 时钟源

外部高速时钟(HSE):外部 OSC 提供 4MHZ ~30MHz 晶振

低速内部时钟(LSI): 内部低速 RC OSC 提供 32KHz 时钟源

系统时钟 (SYSPLL): 提供高达 48MHz 的高速时钟

2.系统时钟框图

手册中的框图可以帮助我们更好的理解时钟的每个配置步骤。

输入频率:支持4~30MHZ

VCO = 输入频率 * FBKDIV / PREDIV

系统时钟 = VCO / POSDIV / SYSCLKDIV

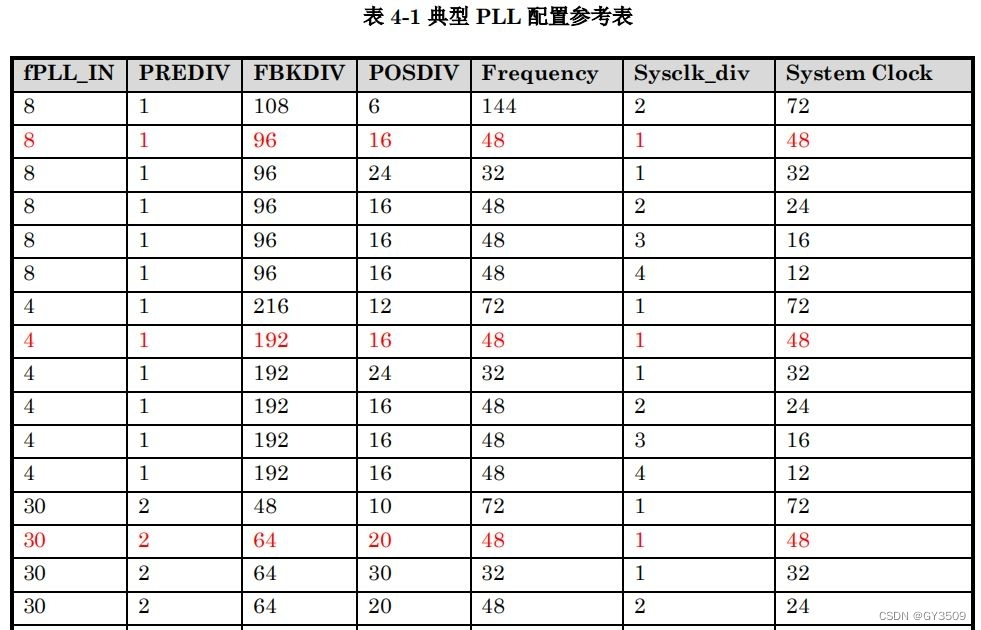

同时,手册中也提供了典型的配置参数供参考。因为有些点的频率值是有限制的,比如VCO的频率范围是0.5GHZ~1.5GHZ,那么直接参考典型配置参考表就肯定不会有问题,找到合适的参数即可。

三 自定义时钟

以AC7801的开发板做测试,板子上外部晶振为8MHZ。这里以配置系统时钟为48MHZ,APB时钟为24MHZ为例。根据上面的参考表,可选择PREDIV = 1,FBKDIV = 96,POSDIV=16,VOC = 8*96/16 =48M。相关寄存器如下图,可知:SYSPLL1_PREDIV为0,SYSPLL1_POSDIV为8,SYSPLL1_FBKDIV为96。

为了直观的测试时钟的频率,用一个定时器,定时产生中断,在中断中翻转一个I/O电平,以此来测时钟频率。定时器初始化如下:定时器的时钟源为APB时钟24M,配置定时器装载值为24000000,则1S产生一次中断。

cpp

void TIMER_Config(void)

{

TIMER_ConfigType config;

memset(&config, 0, sizeof(config));

config.periodValue = 24000000; /*!< TIMER channel period value */

config.linkModeEn = DISABLE ; /*!< TIMER channel linkmode enable */

config.interruptEn = ENABLE ; /*!< TIMER channel interrupt enable */

config.callBack = TIM_CallBack; /*!< TIMER channel callback pointer */

config.timerEn = ENABLE; /*!< TIMER channel enable/disable */

TIMER_Init(TIMER_CHANNEL0, &config); //TIMER0初始化配置

}1. 中断处理

cpp

void TIM_CallBack(void *device, uint32_t wpara, uint32_t lpara)

{

if (wpara & TIMER_CHANNEL_TF_T**_Msk)

{

GPIOC->ODR ^= (1<<7);

}

}2.外部时钟配置------库函数

cpp

void SYS_CLOCK_HSE(void)

{

/* check if xosc enable success? */

if (SPM_EnableXOSC(ENABLE) == SUCCESS)

{

CKGEN_SetPLLReference(PLL_REF_EXTERNAL_OSC);//PLL参考时钟选择外部振荡器

}

else /* if xosc enable fail, */

{}

/* set system clock divider */

CKGEN_SetSysclkDiv(0);//系统时钟1分频

/* check if pll enable success? */

if (SPM_EnablePLL(ENABLE) == SUCCESS)/使能SYSPLL

{

CKGEN_SetPllPrevDiv(0);//PREDIV

CKGEN_SetPllPostDiv(8);//PLL_POSDIV

CKGEN_SetPllFeedbackDiv(96);//PLL_FBKDIV

CKGEN_SetSysclkSrc(SYSCLK_SRC_PLL_OUTPUT);//系统时钟源选择PLL时钟

}

else /* pll enable fail */

{}

CKGEN_SetAPBClockDivider(APBCLK_DIVIDER_2);//APB时钟为系统时钟2分频

}3.外部时钟配置------寄存器

外部时钟的使能以及就绪标志,PLL使能以及就绪标志等,在第6章系统电源管理SPM模块下的SPM_PWR_MGR_CFG1寄存器里。

配置过程比较常规,使能时钟------>等待时钟就绪------>PLL时钟源选择------>时钟分频及倍频配置------>系统时钟源选择

cpp

void SYS_CLOCK_HSE_REG(void)

{

SPM->PWR_MGR_CFG1 |= 1<<29;//外部高速时钟XOSC使能

while((SPM->PWR_MGR_CFG1 &(0X80000000))==0)//等待XOSC就绪

{}

SPM->PWR_MGR_CFG1 |= (1<<27);//SYSPLL使能

while((SPM->PWR_MGR_CFG1 &(0X40000000))==0)//等待PLL时钟就绪

{}

CKGEN->CTRL |= (1<<20);//PLL参考时钟选择外部振荡器

CKGEN->SYSPLL1_CFG0 = ((CKGEN->SYSPLL1_CFG0 & (~(uint32_t)(0x3<<30)))|(0<<30)); //PREDIV

CKGEN->SYSPLL1_CFG0 = ((CKGEN->SYSPLL1_CFG0 & (~(uint32_t)(0x1f<<25)))|(8<<25)); //POSDIV

CKGEN->SYSPLL1_CFG0 = ((CKGEN->SYSPLL1_CFG0 & (~(uint32_t)(0xff<<15)))|(96<<15)); //FBKDIV

CKGEN->CTRL |= ((CKGEN->CTRL & (~(3<<4)))|(0<<4)); //系统时钟分频为1

CKGEN->CTRL |= (1<<0);//系统时钟源选择PLL时钟

CKGEN->CTRL |= (1<<8);//APB为系统时钟2分频

}4.内部时钟配置------库函数

采用内部高速8M时钟源做配置

cpp

void SYS_CLOCK_HSI(void)

{

CKGEN_SetPLLReference(PLL_REF_INTERAL_OSC);//PLL参考时钟选择内部振荡器

CKGEN_SetPllPrevDiv(0); //PREDIV

CKGEN_SetPllPostDiv(8); //POSDIV

CKGEN_SetPllFeedbackDiv(96); //FBKDIV

CKGEN_SetSysclkDiv(0); //系统时钟1分频

/* check if pll enable success? */

if (SPM_EnablePLL(ENABLE) == SUCCESS)

{

/* pll enable success,use pll output as system clock src */

CKGEN_SetSysclkSrc(SYSCLK_SRC_PLL_OUTPUT);//系统时钟源选择PLL时钟

}

else

{

/* pll enable fail */

}

CKGEN_SetAPBClockDivider(APBCLK_DIVIDER_2);//APB为系统时钟2分频

}5.内部时钟配置------寄存器

cpp

void SYS_CLOCK_HSI_REG(void)

{

CKGEN->CTRL &= ~(1<<20);//PLL参考时钟选择内部振荡器

SPM->PWR_MGR_CFG1 |= (1<<27);//SYSPLL使能

while((SPM->PWR_MGR_CFG1 &(0X40000000))==0)//等待PLL时钟就绪

{}

CKGEN->SYSPLL1_CFG0 = ((CKGEN->SYSPLL1_CFG0 & (~(uint32_t)(0x3<<30)))|(0<<30)); //PREDIV

CKGEN->SYSPLL1_CFG0 = ((CKGEN->SYSPLL1_CFG0 & (~(uint32_t)(0x1f<<25)))|(8<<25)); //POSDIV

CKGEN->SYSPLL1_CFG0 = ((CKGEN->SYSPLL1_CFG0 & (~(uint32_t)(0xff<<15)))|(96<<15)); //FBKDIV

CKGEN->CTRL |= ((CKGEN->CTRL & (~(3<<4)))|(0<<4)); //SYSCLK_DIV,系统时钟1分频

CKGEN->CTRL |= (1<<0);//系统时钟源选择PLL时钟

CKGEN->CTRL |= (1<<8);//APB为系统时钟2分频

}6.主函数

主函数中调用时钟初始化函数,并对TIMER0配置,同时需要对使用到的I/O进行配置。

cpp

int main(void)

{

//SYS_CLOCK_HSE();

SYS_CLOCK_HSE_REG();

//SYS_CLOCK_HSI();

//SYS_CLOCK_HSI_REG();

TIMER_Config();

GPIO_SetFunc(GPIOC, GPIO_PIN7, GPIO_FUN0);/*功能复用选择*/

GPIO_SetDir(GPIOC, GPIO_PIN7, GPIO_OUT);

GPIO_SetPinLevel(GPIOC, GPIO_PIN7, GPIO_LEVEL_HIGH);

while(1)

{

}

}