笔者所在学校将数电的内容融合进了计算机组成原理的课程里面。

所以我在学习计组时花时间去速通了一下数电。本笔记由本人在b站观看大量视频后写出,凝聚了本人的心血。

来源:1、数字电子技术基础期末复习速成(0基础逆袭90+)_哔哩哔哩_bilibili(主体)

4、数电:计数器_哔哩哔哩_bilibili(不明白的话可以找一些其他课)

5、学校ppt

文章目录

- 一、数制的转换:

- 三、化简题公式口诀和逻辑函数的书写:

- 四、最小项的写法和公式法简化:

- 五、卡诺图的化简:

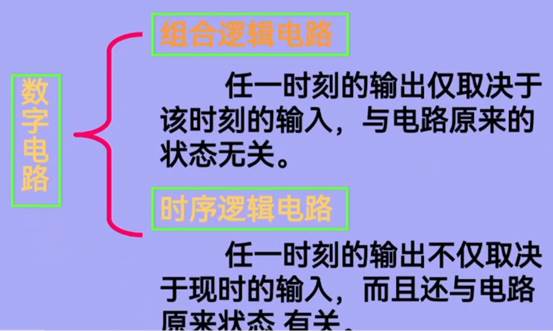

- 六、组合逻辑电路:

- 七、编码器:

- 八、译码器:

- 九、数据选择器:

- 十、触发器:

- 十一、时序逻辑电路:

一、数制的转换:

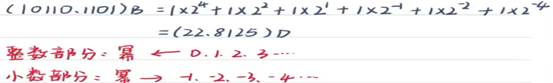

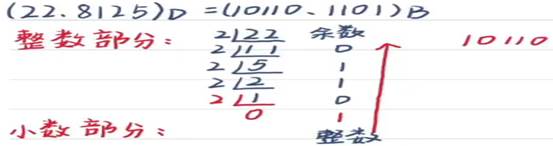

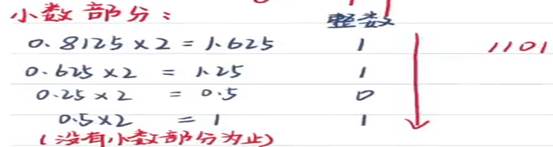

1、二进制(B)和十进制(D):

B-->D:

例题:

D-->B:

2、二进制(B)和八进制(O):

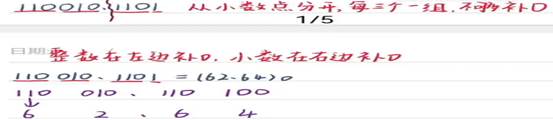

B-->O:

例题:

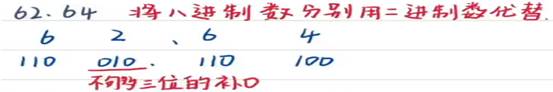

O-->B:

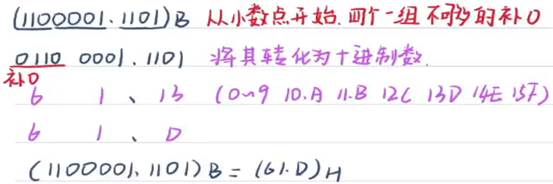

3、二进制(B)和十六进制(H):

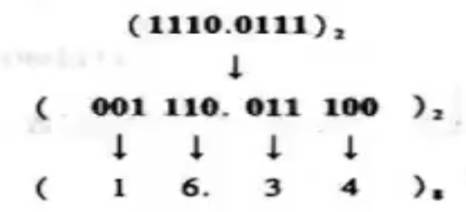

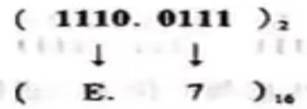

B-->H:

例题:

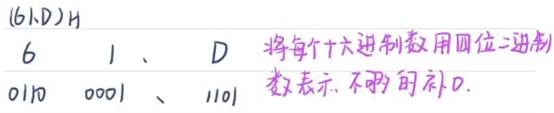

H-->B:

例题:

4、D--O、D--H、O--H:

先转化成二进制再转换。

三、化简题公式口诀和逻辑函数的书写:

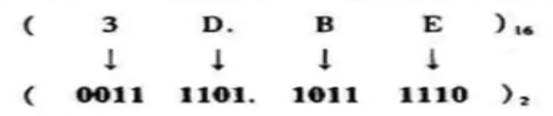

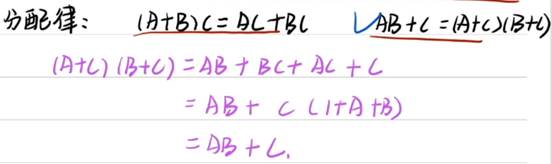

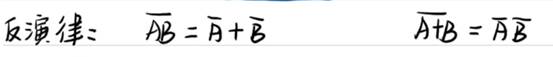

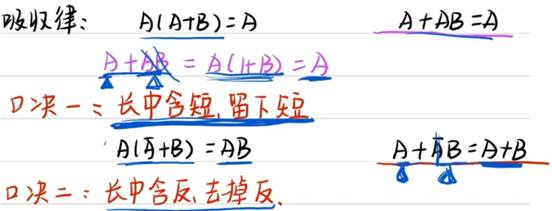

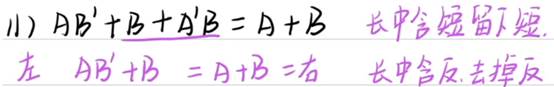

公式:

长逆变短逆,与变或,或变与。

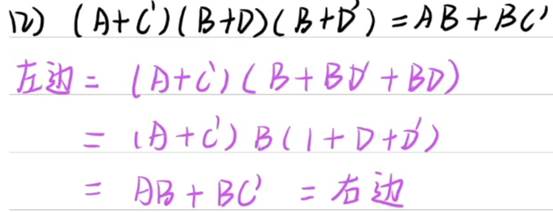

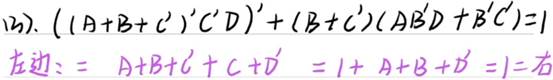

题型一、证明题:

从外往里去逆。

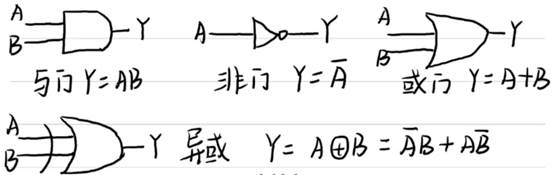

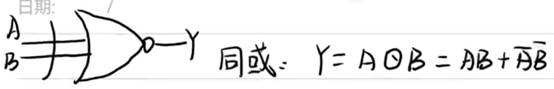

逻辑门符号:

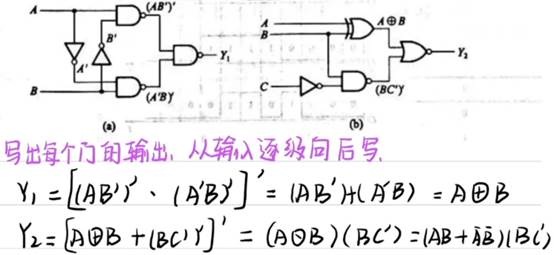

题型二、由图写逻辑表达式:

四、最小项的写法和公式法简化:

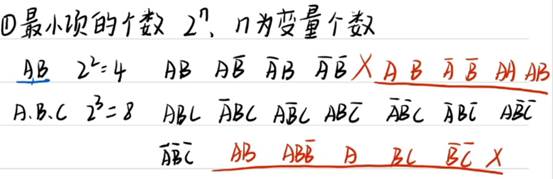

题型三、最小项:

每个变量能且只能出现一种形式

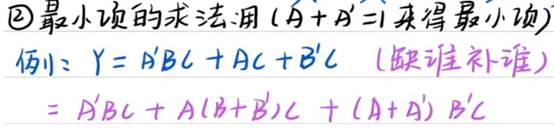

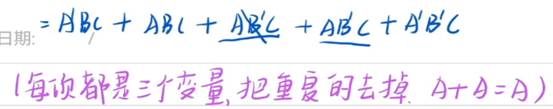

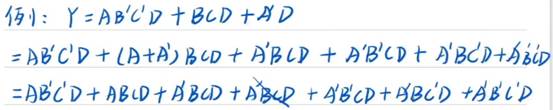

题型四、公式法化简:

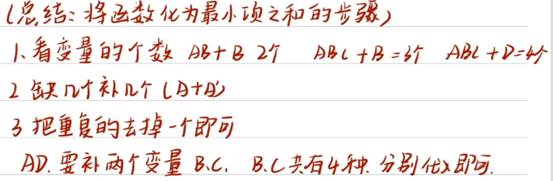

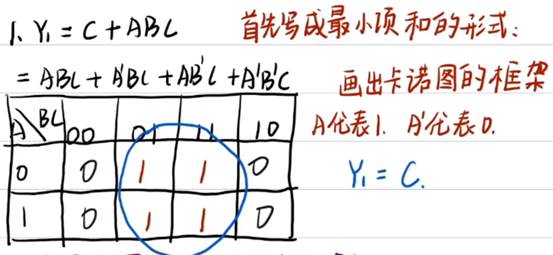

五、卡诺图的化简:

也可以圈0求非。

每次圈的个数只能是2的次方个(2、4、8...)。

对称于中心线的小方格也是相邻项。

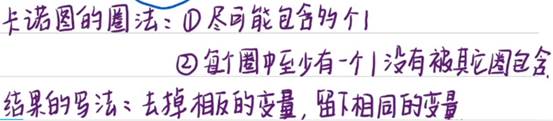

习题

化简具有无关项的逻辑函数

无关项:即可当0又可当1,用的上就是1,用不上就是0。

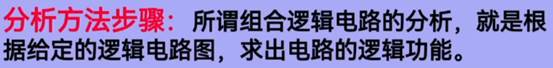

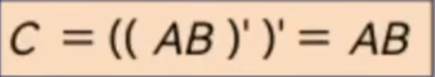

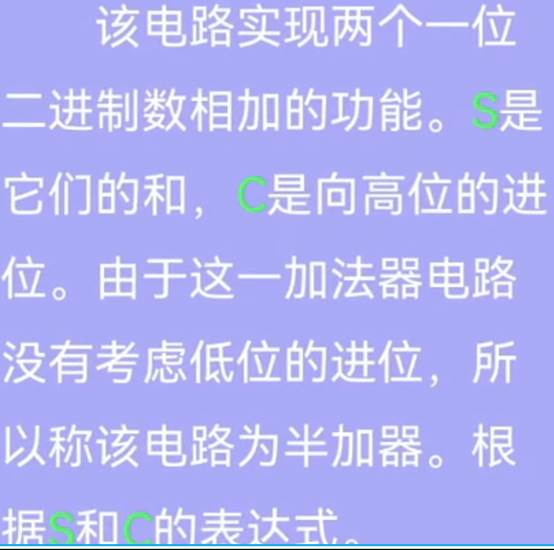

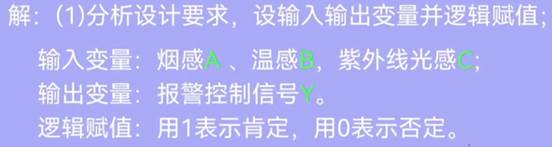

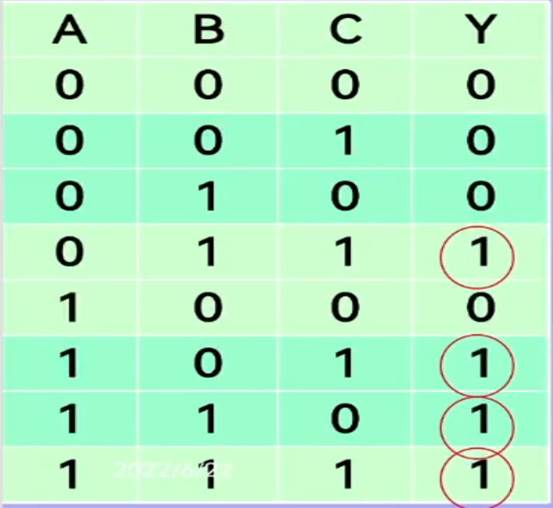

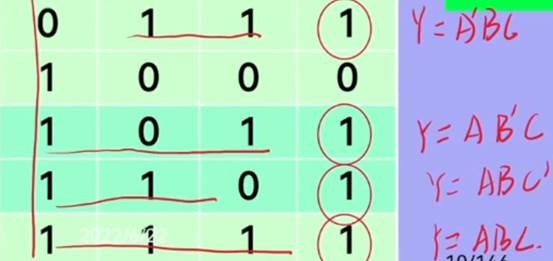

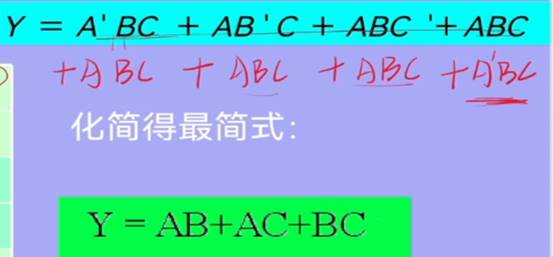

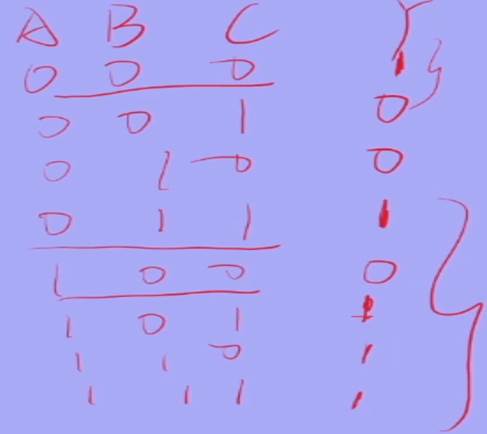

六、组合逻辑电路:

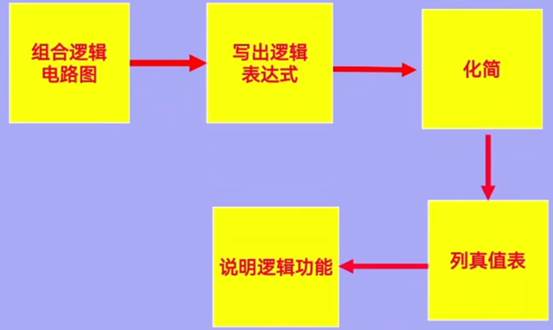

分析:

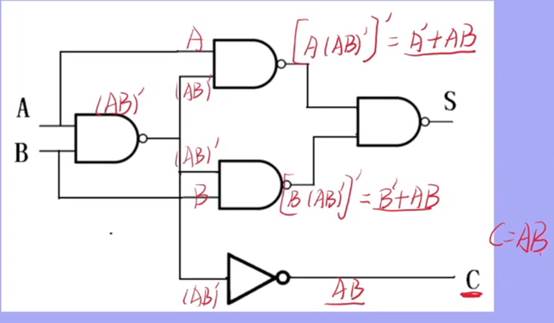

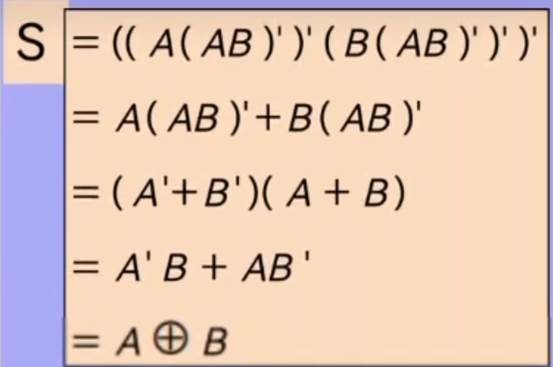

例1:

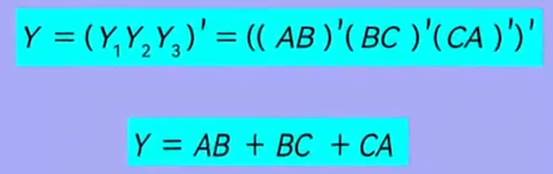

例2:

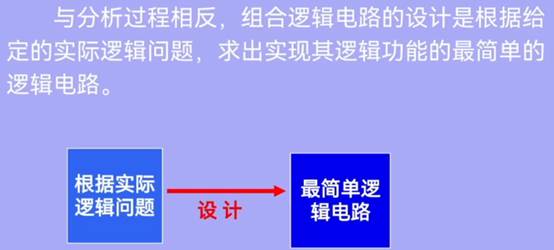

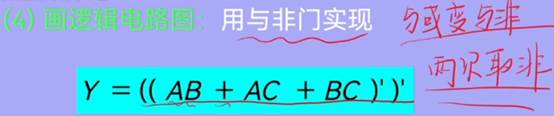

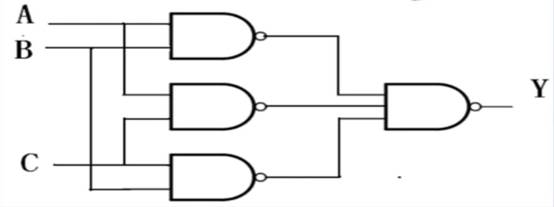

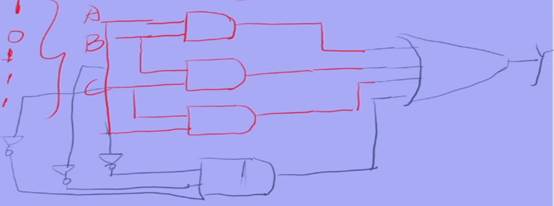

设计:

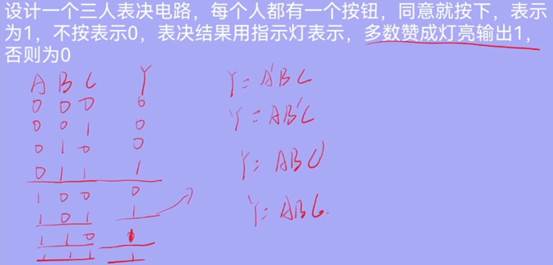

例1:

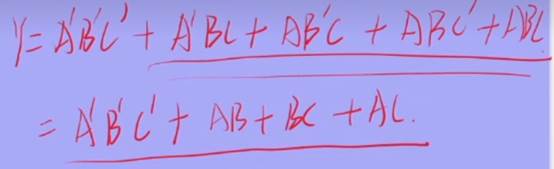

A+A=A所以ABC+ABC=ABC,这样达到化简得目的。或者用卡诺图化简。

例2:

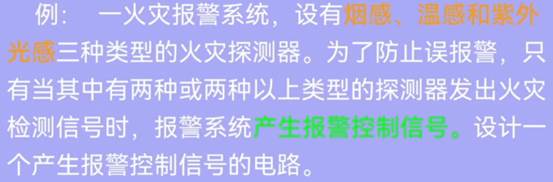

例3:

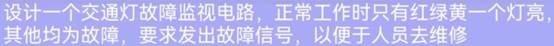

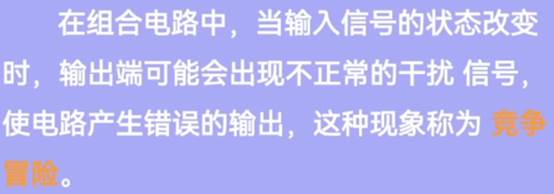

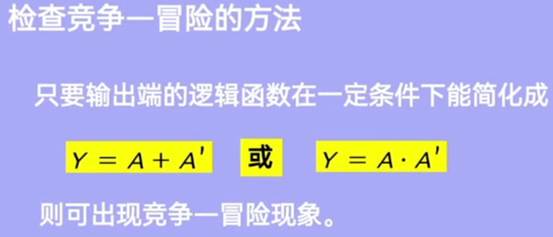

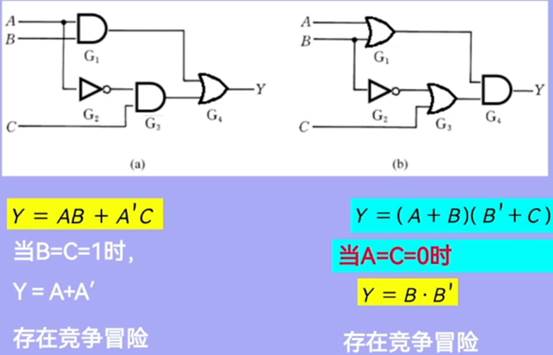

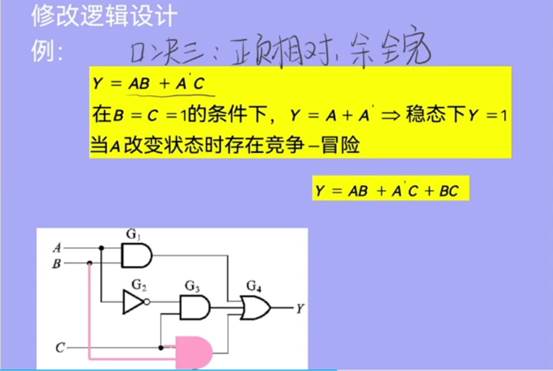

竞争冒险现象:

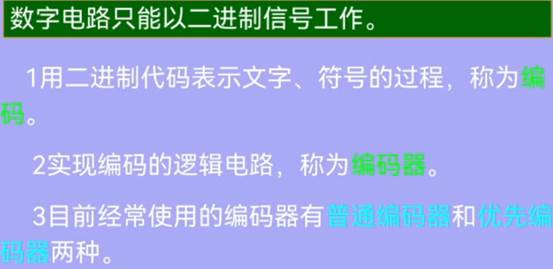

七、编码器:

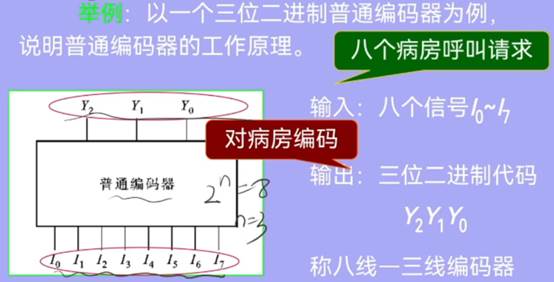

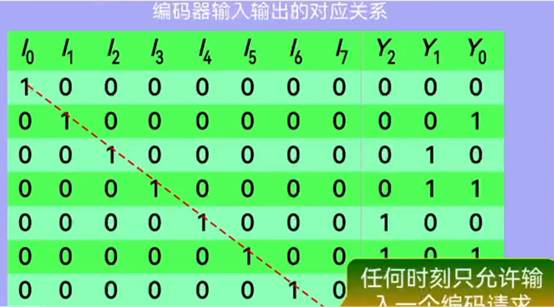

普通编码器:

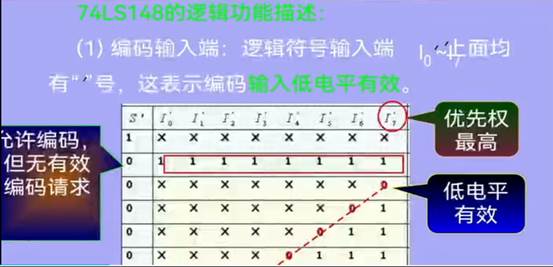

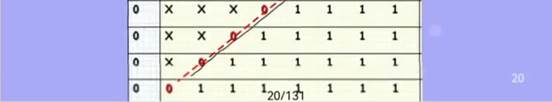

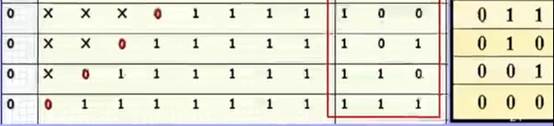

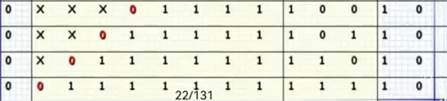

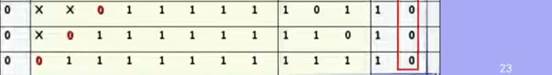

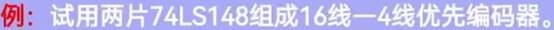

优先编码器:

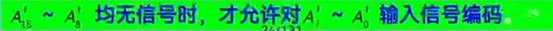

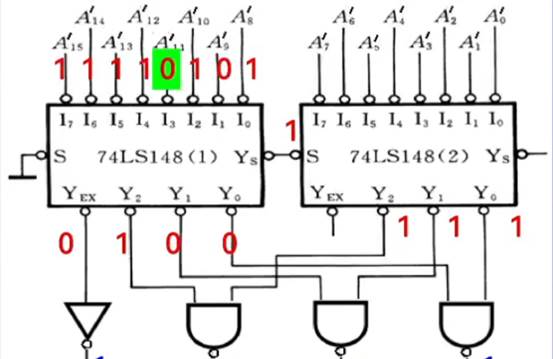

一撇表示低电平有效。选通输出端和扩展端主要用于两片及以上拓展用的。

注意在此I7'的优先权最高仅对于此编码器而言。

S'为0而输入为全1说明此时编码器能正常工作但没有信号申请编码。

例1:

S'接地及代表s'=0。

例2:

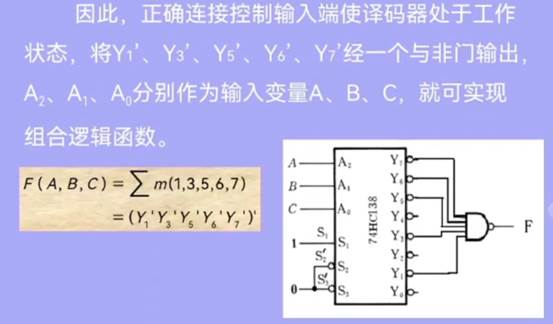

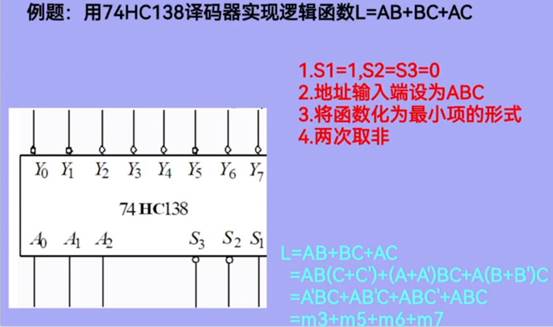

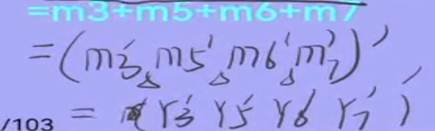

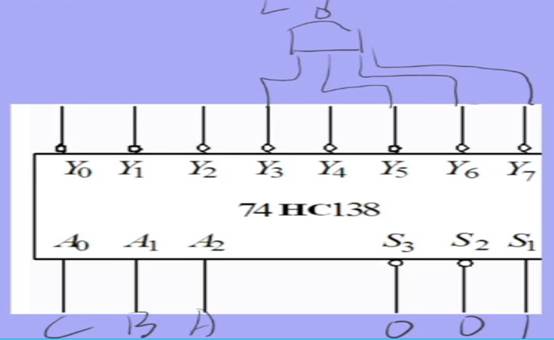

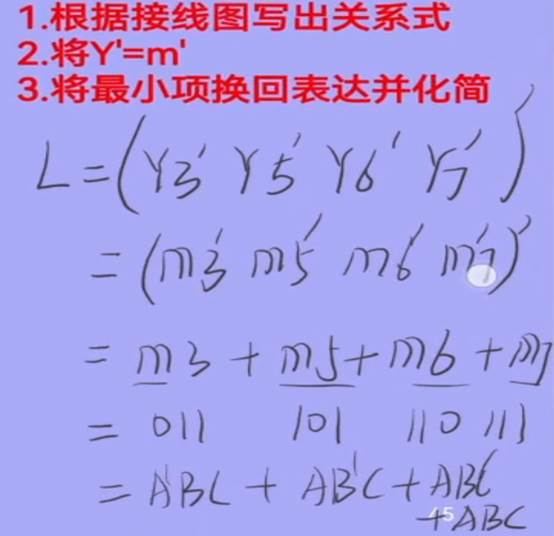

八、译码器:

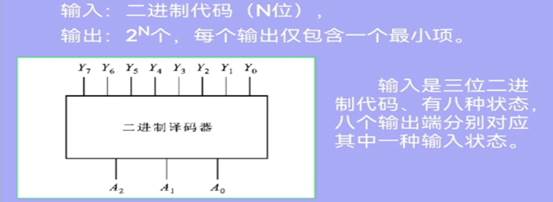

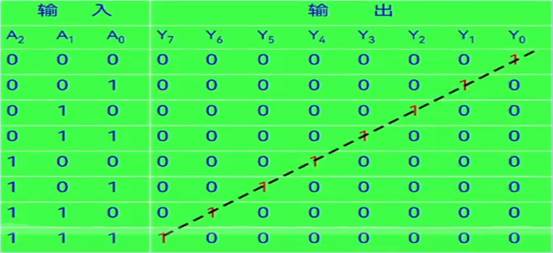

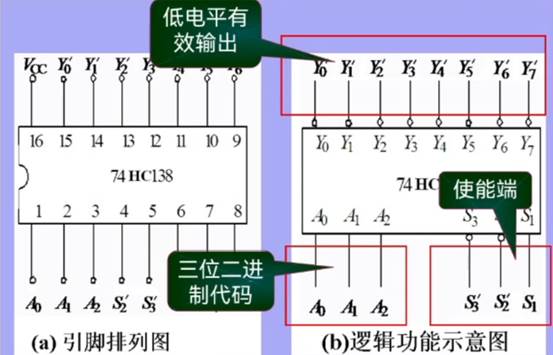

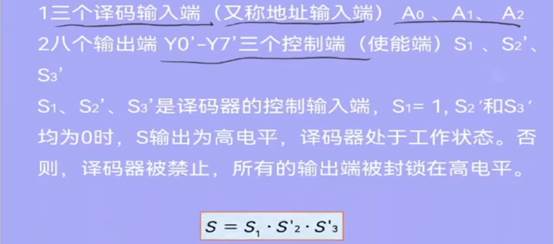

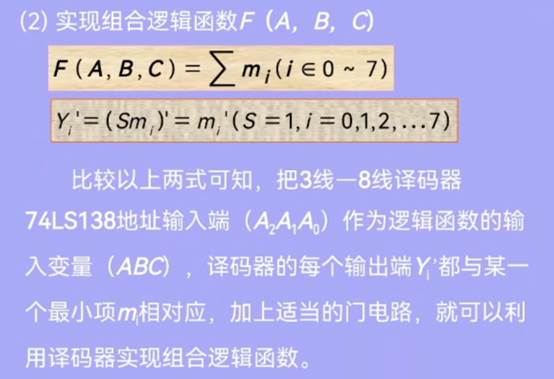

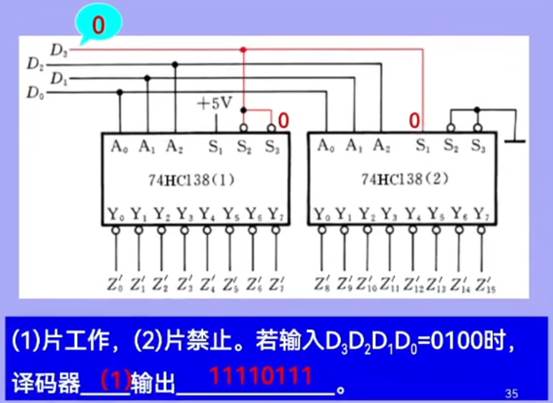

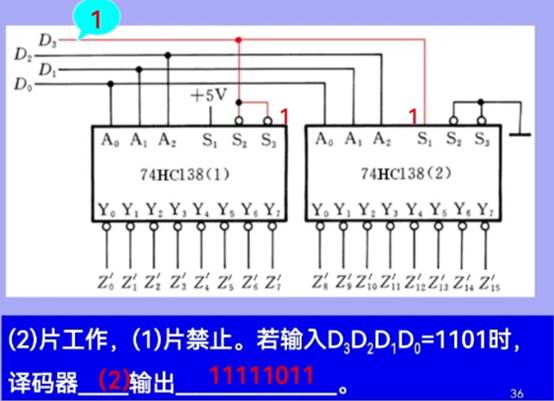

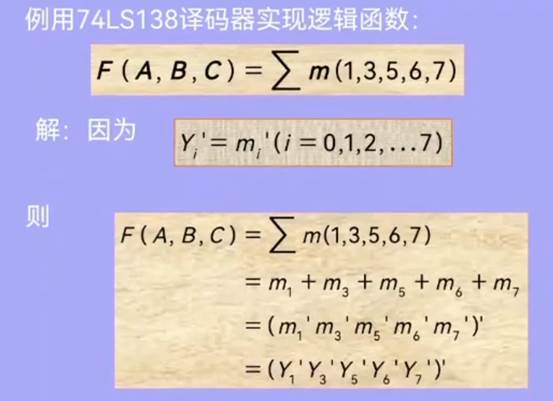

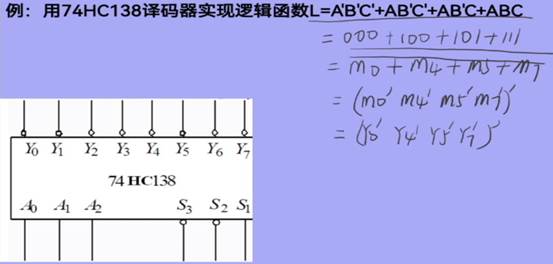

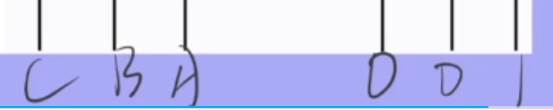

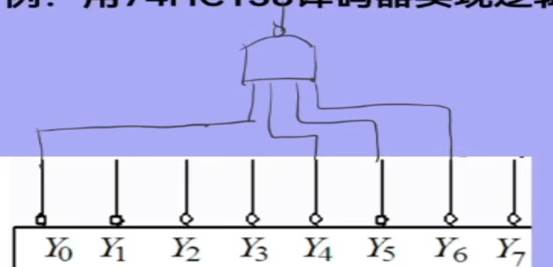

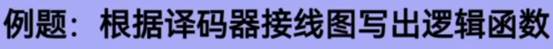

二进制译码器:

例1:

例2:

例3:

例4:

例5:

例6:

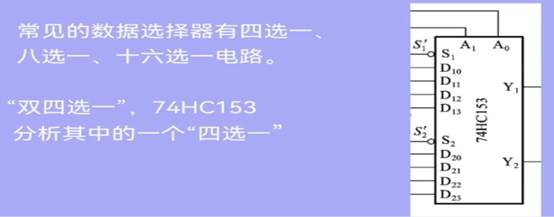

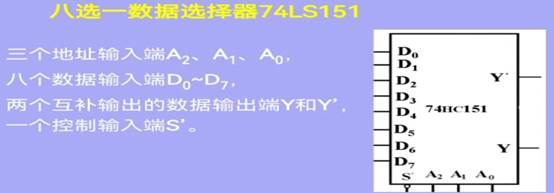

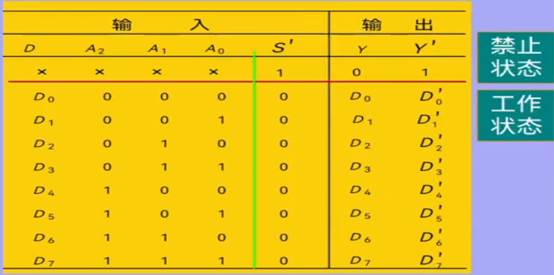

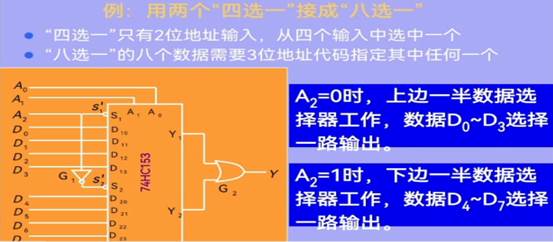

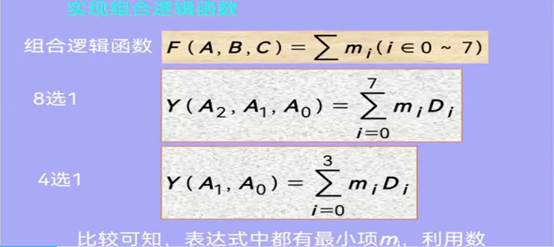

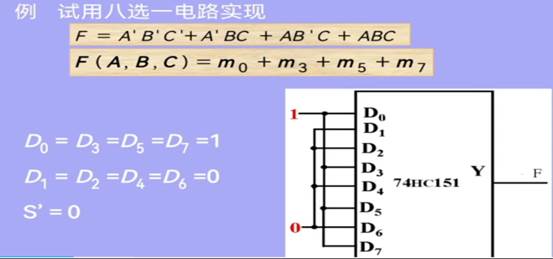

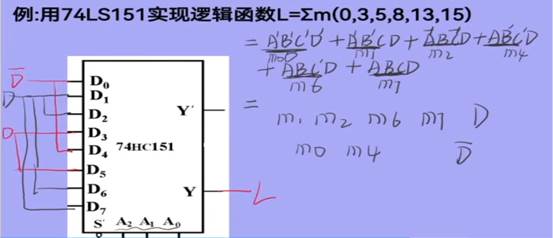

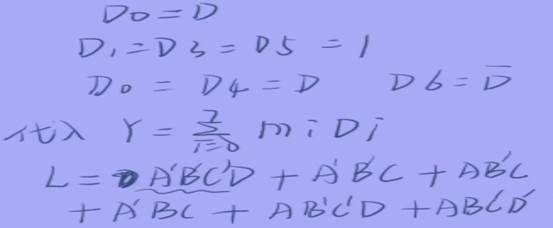

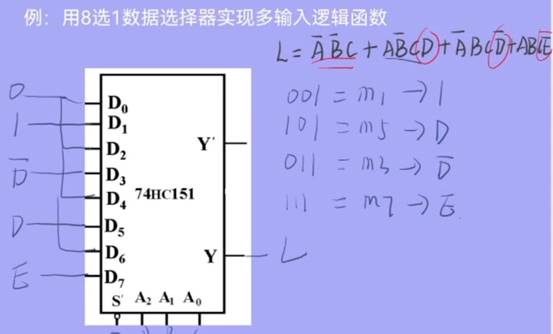

九、数据选择器:

Di的意思是指mi是否存在,Di只有0、1两个取值。

例1:

例2:

例3:

例4:

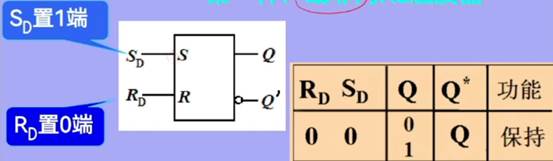

十、触发器:

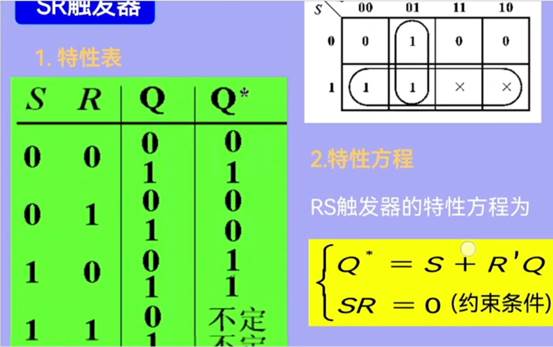

SR锁存器:

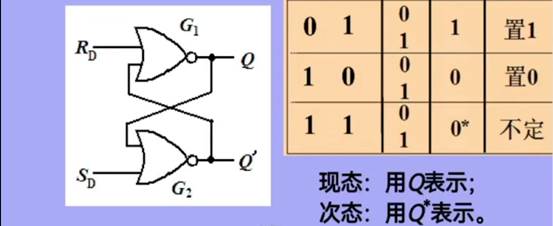

或非门SR锁存器:

1 1默认规定为0

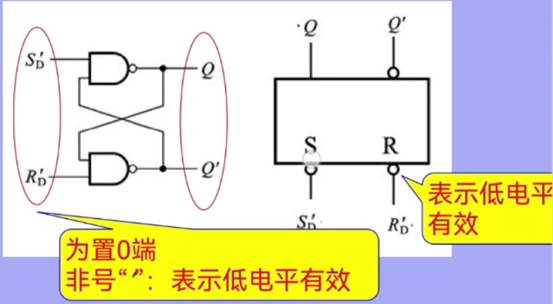

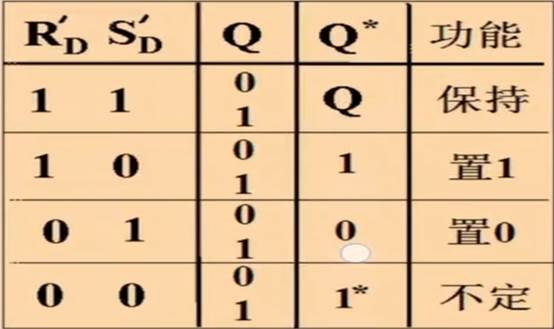

与非门SR锁存器:

0 0 默认规定为1

例1:

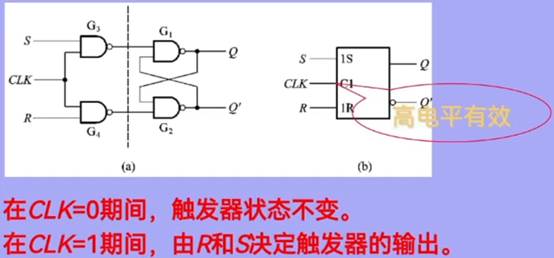

电平触发的触发器:

电平触发的RS触发器:

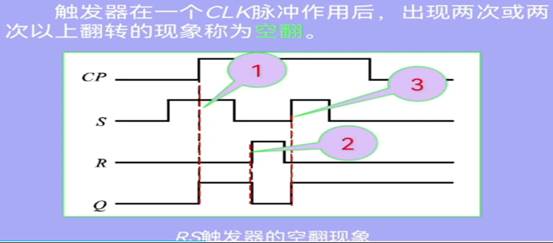

空翻现象:

普通的:

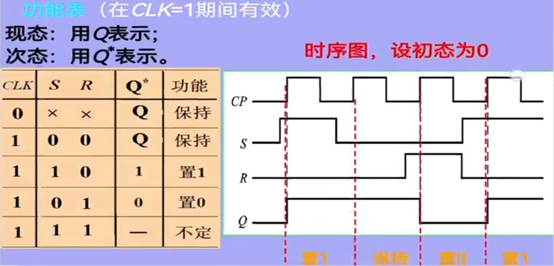

带异步置位、复位端的电平触发SR触发器:

Sd'和Rd'不受CLK脉冲控制

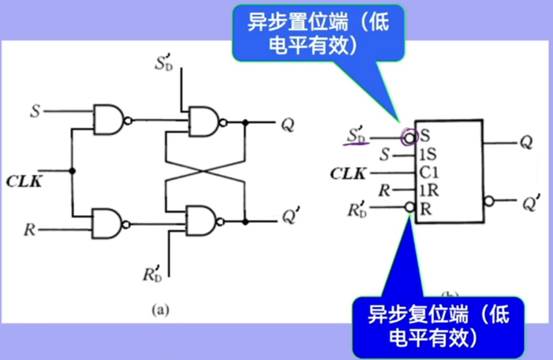

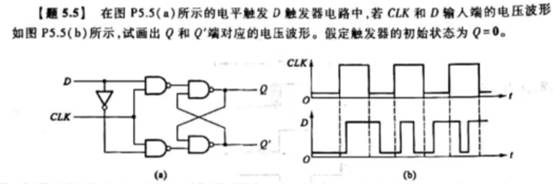

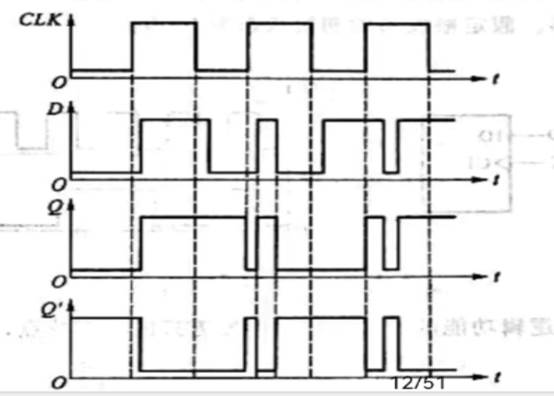

电平触发的D触发器:

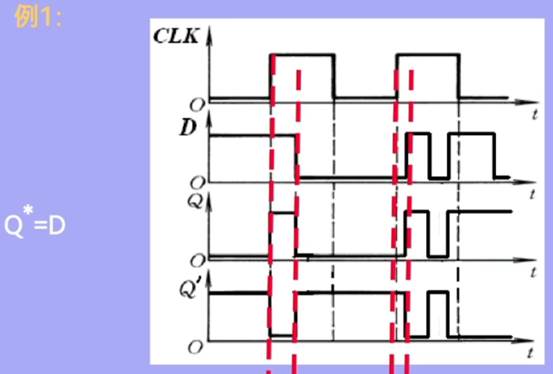

例1:

默认初始Q为0

例2:

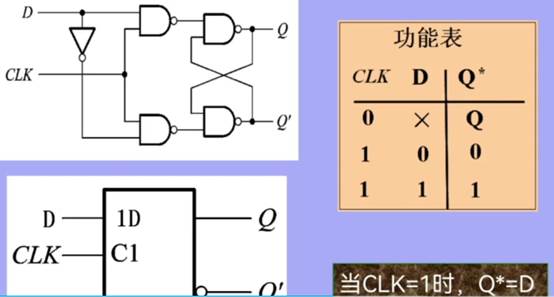

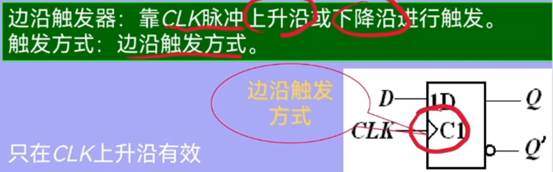

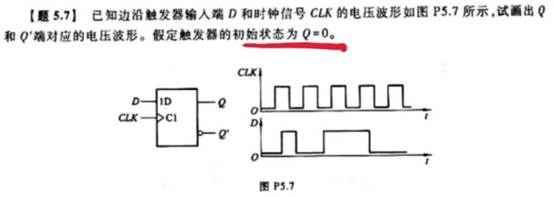

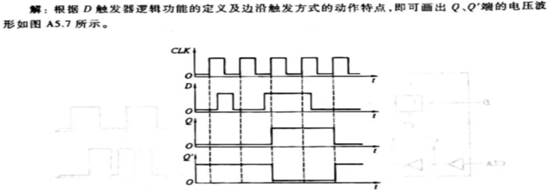

边沿触发器:

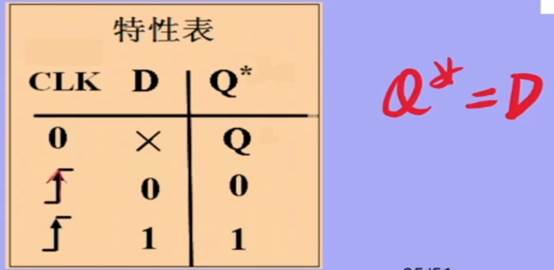

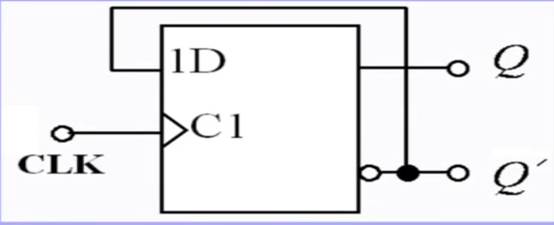

D边沿触发器:

普通的:

例1:

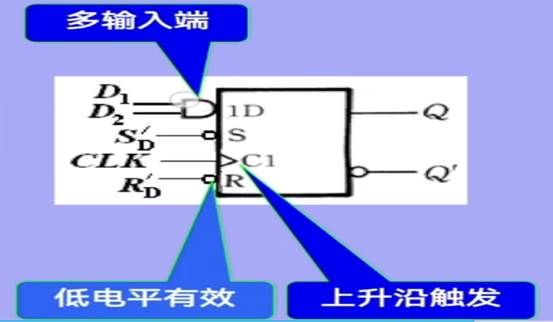

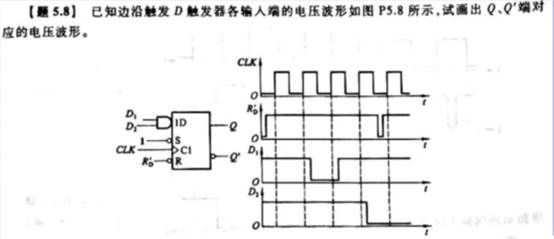

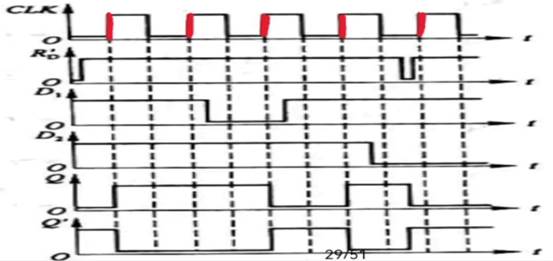

带异步置位、复位端的边沿触发D触发器:

多输入端带异步置位、复位端的边沿触发D触发器:

例1:

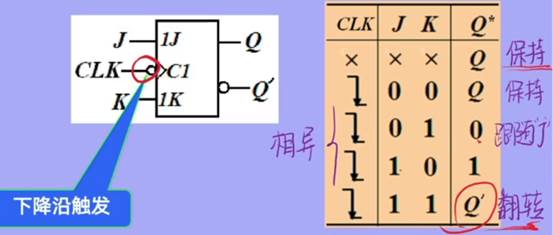

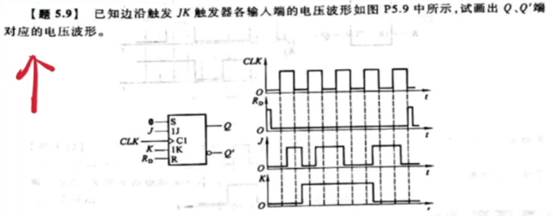

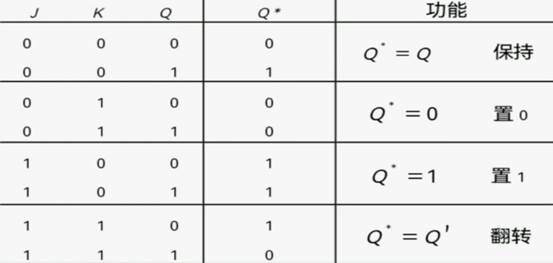

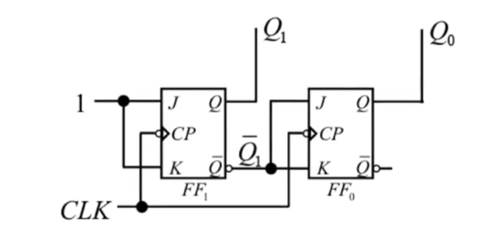

JK边沿触发器:

例1:

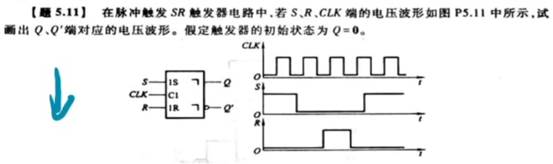

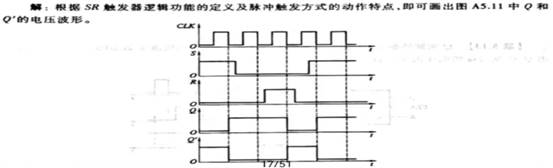

脉冲触发的触发器:

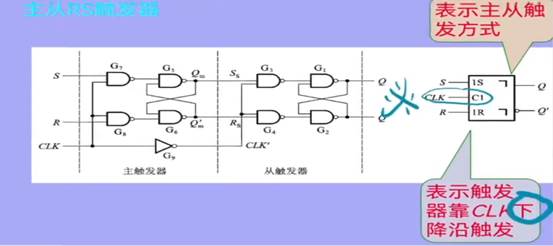

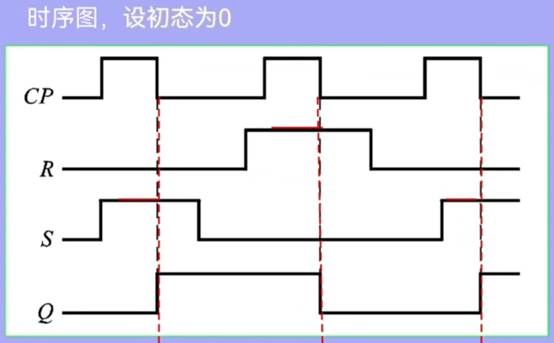

主从RS触发器:

确定Q*状态看的是整个CLK=1期间。

确定Q*状态看的是整个CLK=1期间。

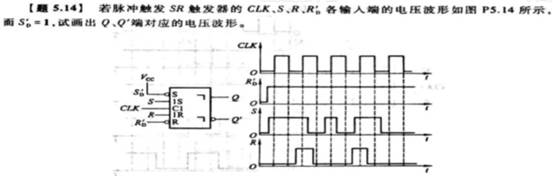

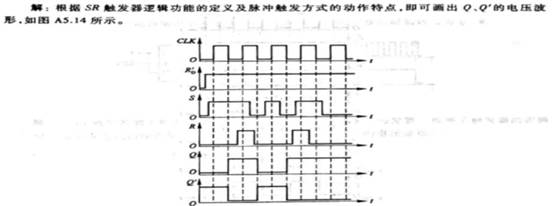

例1:

例2:

在clk=1期间若出现过s=1和r=1的状态(11不定)则跨过此状态去看它的下一个状态。

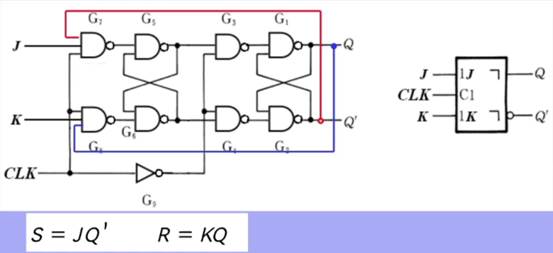

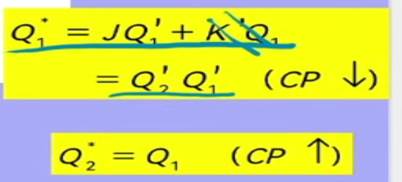

主从JK触发器:

普通的:

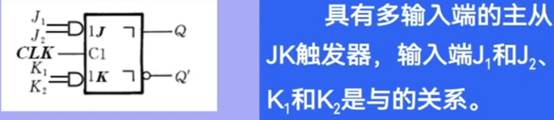

具有多输入端的主从JK触发器:

例1:

有尖峰脉冲的情况则根据封顶值确定Q*。若在CLK=1期间出现多个尖峰脉冲,则根据第一个的。

触发器的特性方程:

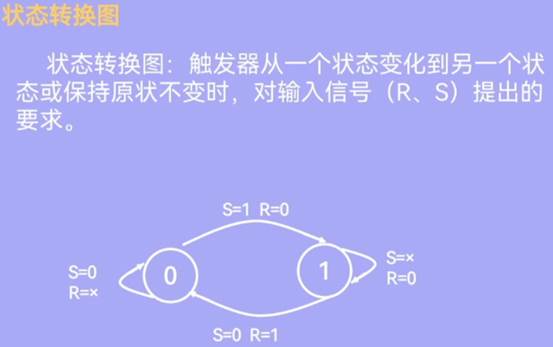

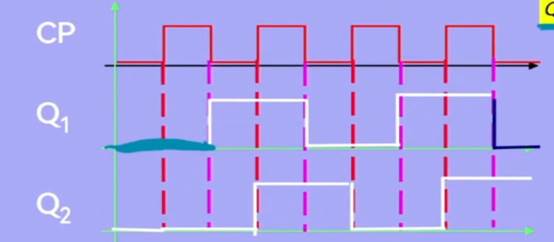

SR触发器:

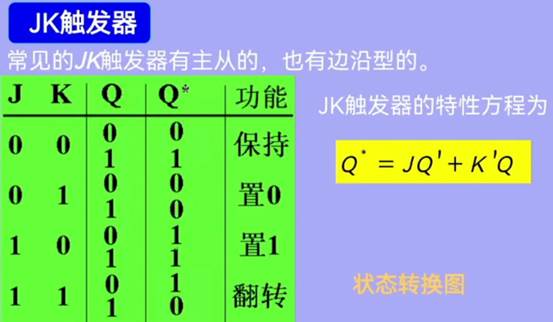

JK触发器:

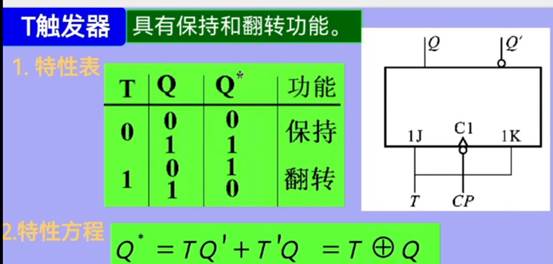

T触发器:

T'触发器:

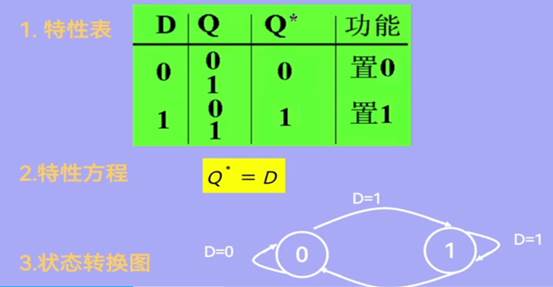

D触发器:

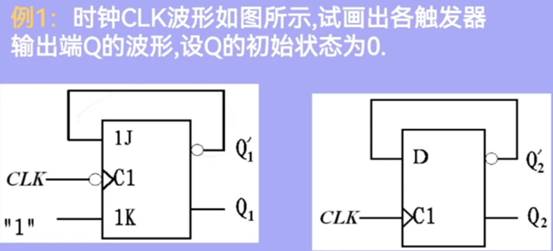

例1:

例2:

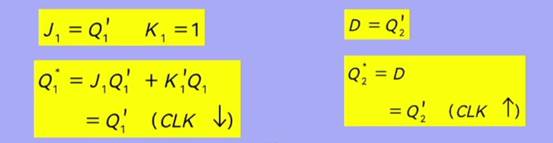

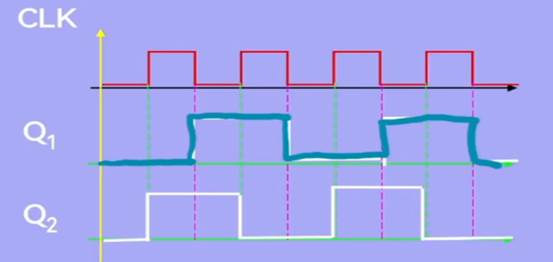

此题Q1 Q2应同时分析。

触发器之间的转换:

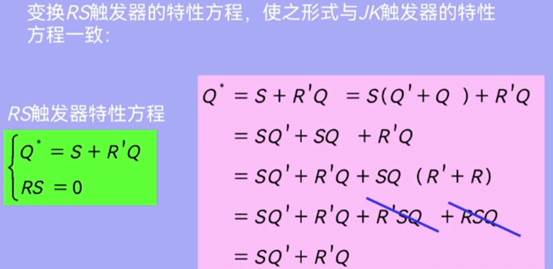

JK触发器-->RS触发器:

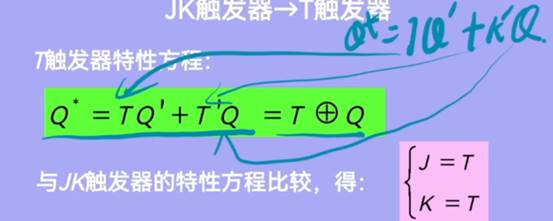

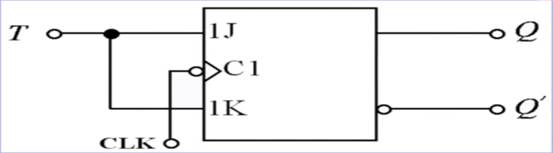

JK触发器--->T触发器:

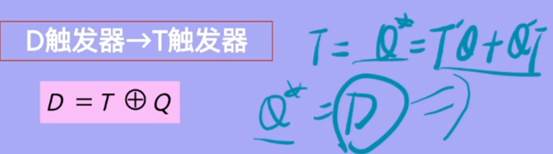

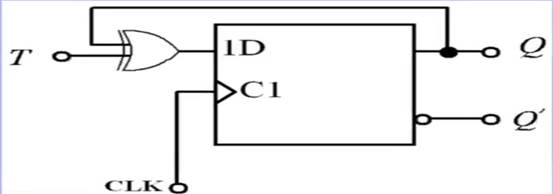

D触发器--->T触发器:

D触发器--->T'触发器:

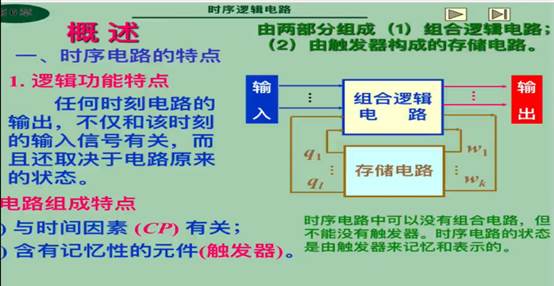

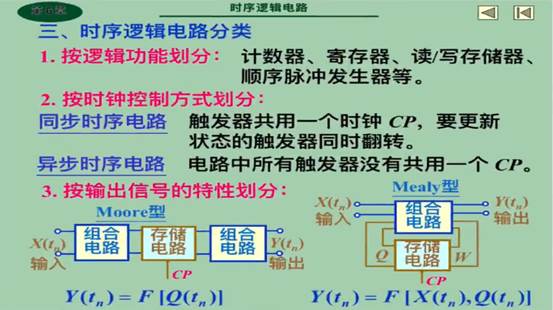

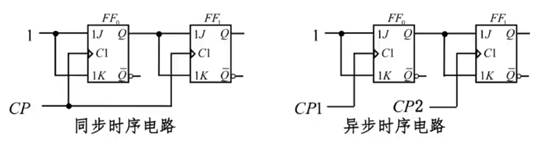

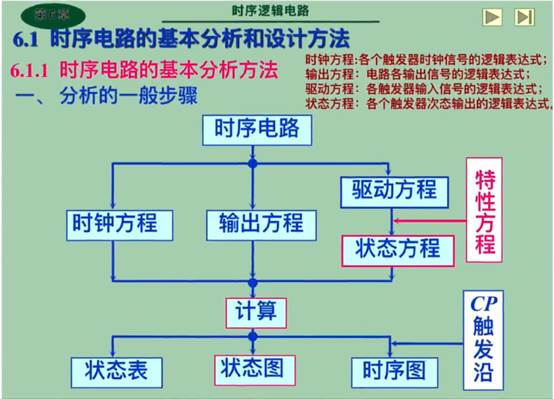

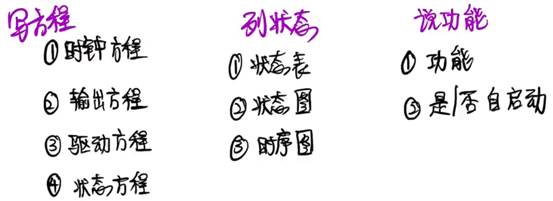

十一、时序逻辑电路:

分析:

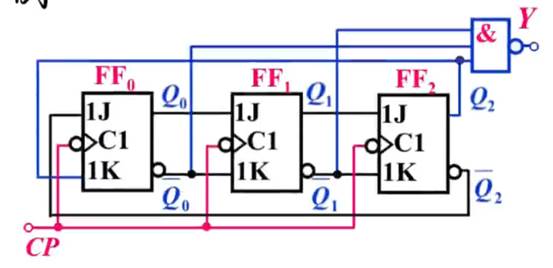

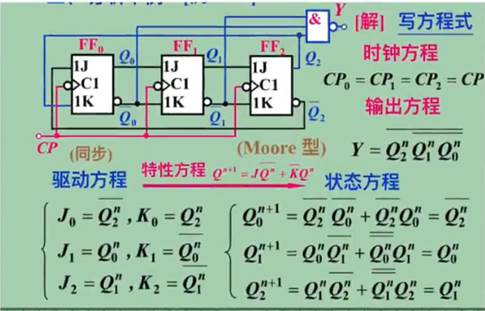

例1:

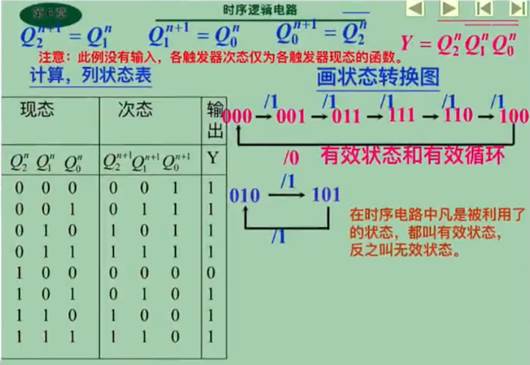

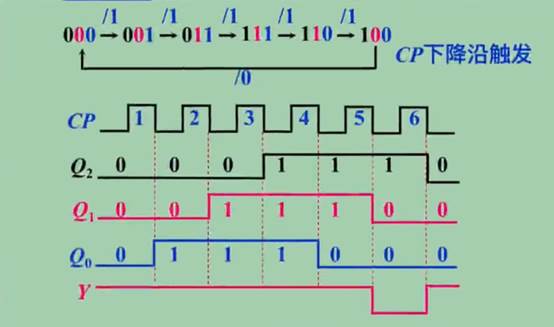

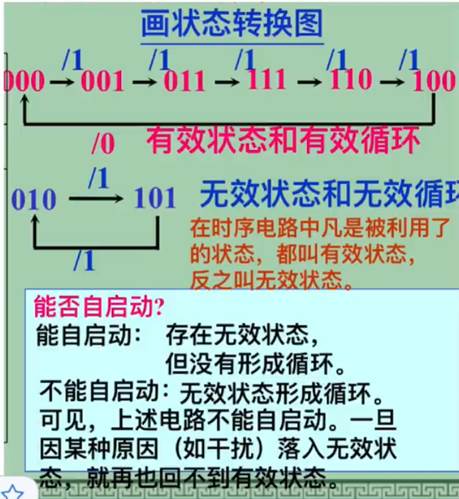

/后面是输出,前面是输入。010和101一直在打转,不能进入其他状态,所以这是两个无效状态,构成无效循环。

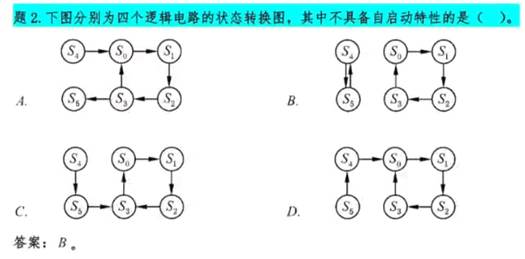

关于自启动:

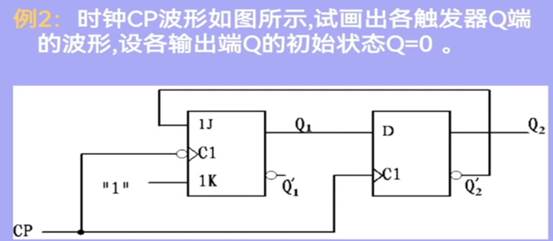

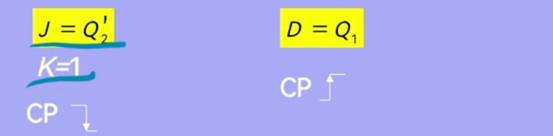

例2:

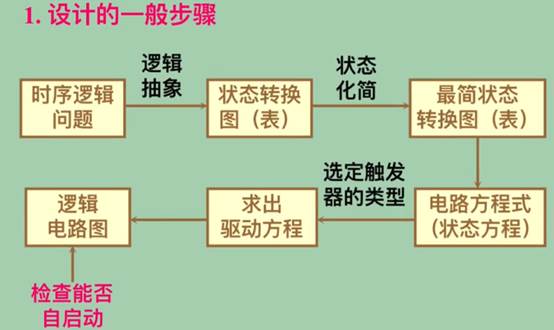

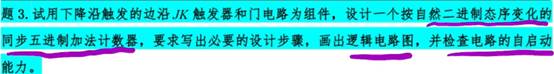

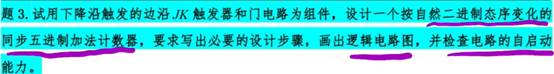

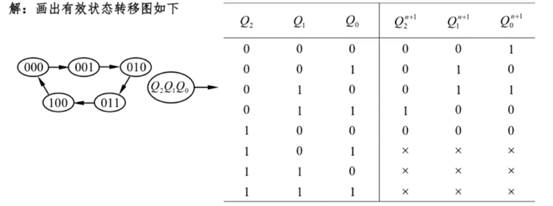

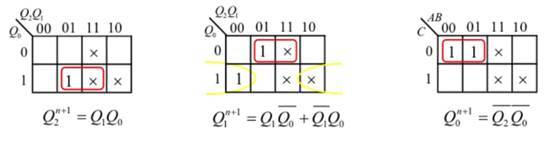

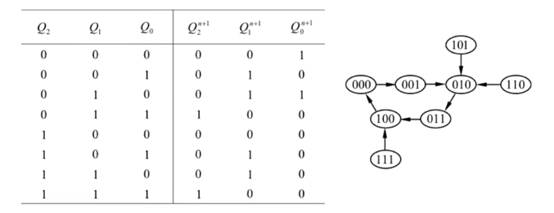

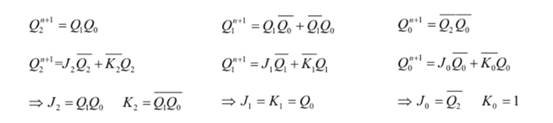

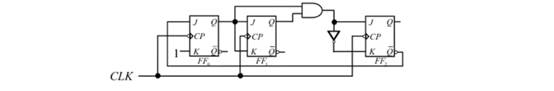

设计:

例1:

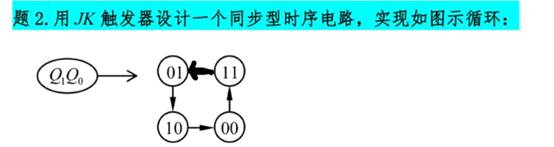

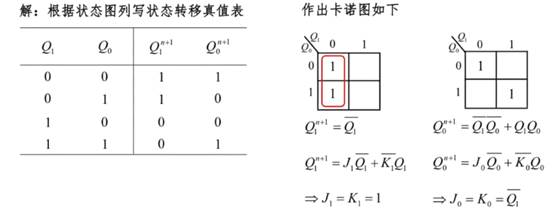

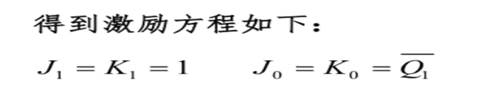

例2:

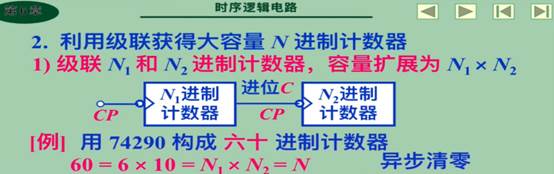

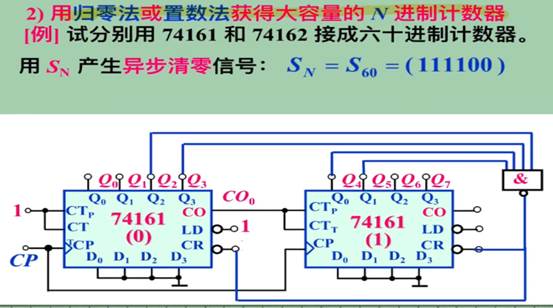

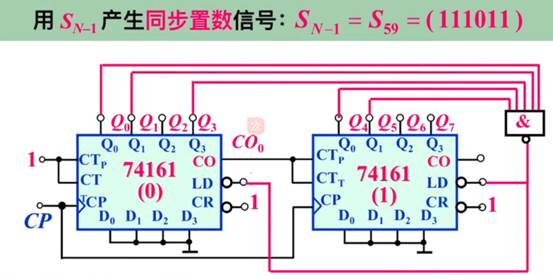

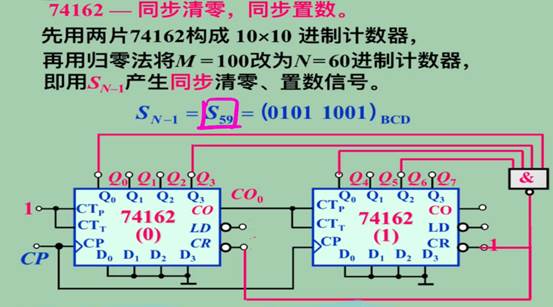

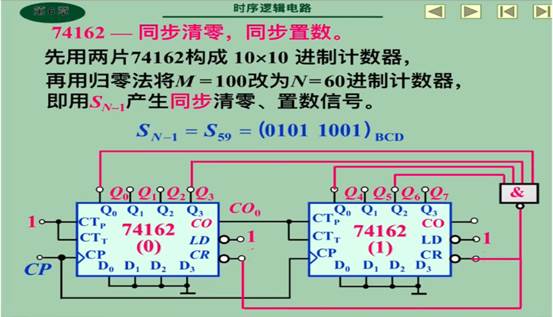

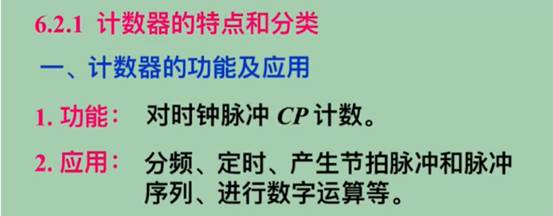

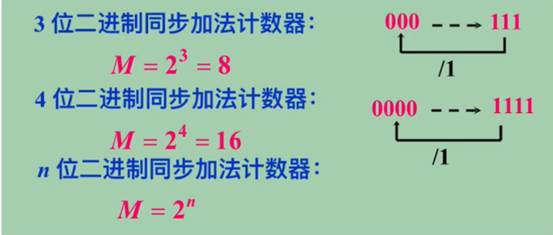

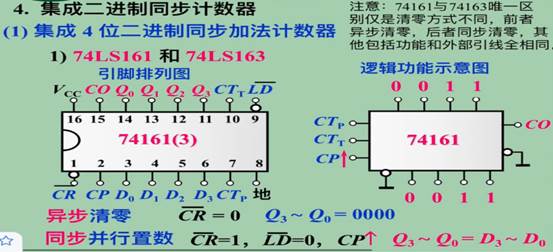

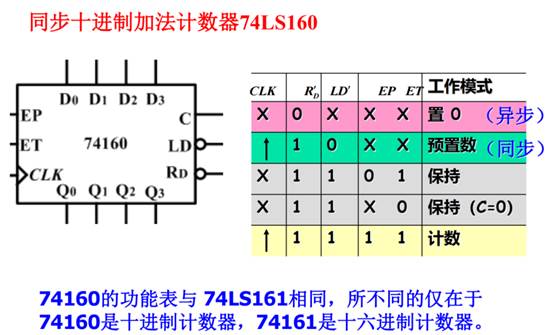

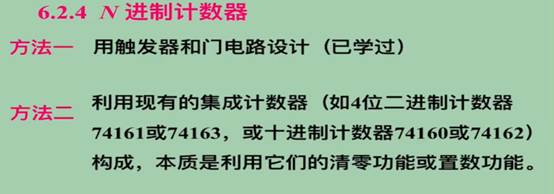

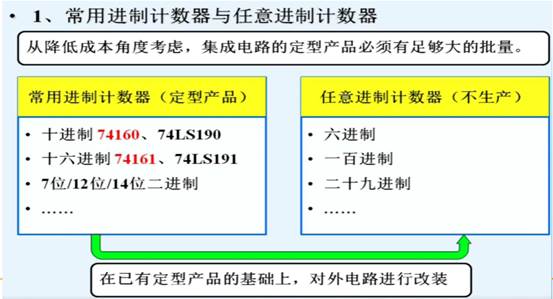

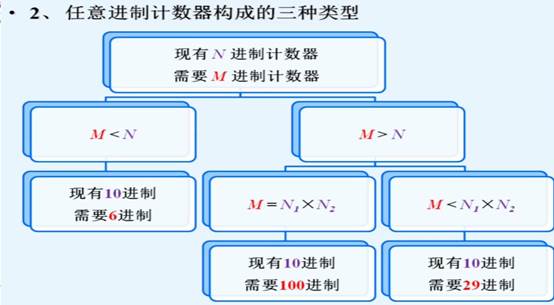

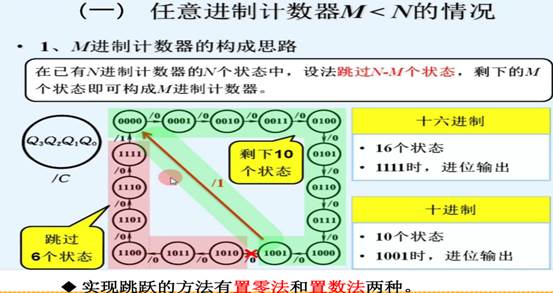

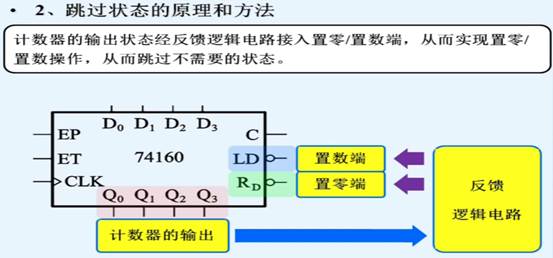

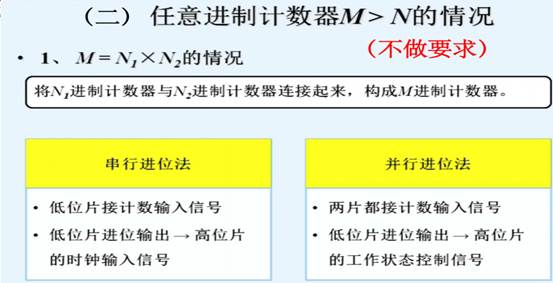

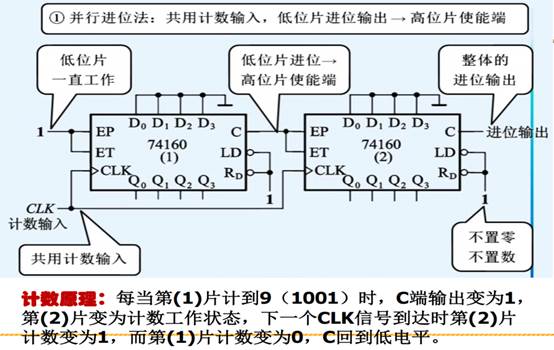

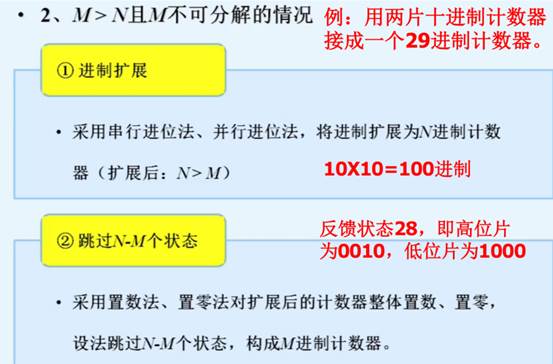

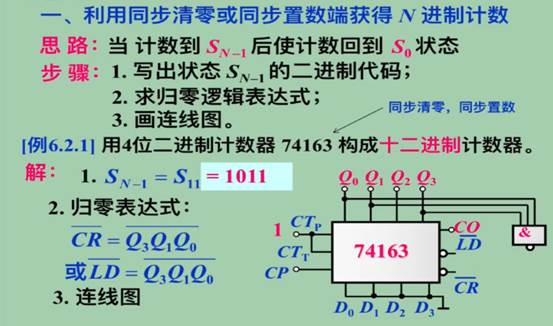

计数器:

例1:

上边没连完,可以根据归零表达式自己连一下。

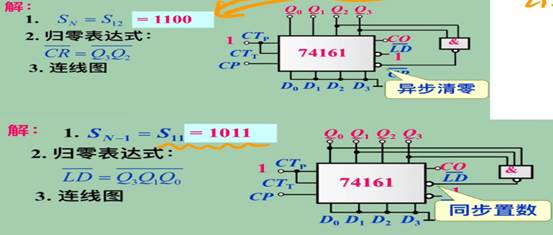

例2:

因为异步清零是瞬间产生的,所以计数可以计到Sn

例3: