目录

[二、Report pulse width](#二、Report pulse width)

[2.1 Report pulse width](#2.1 Report pulse width)

[2.2 配置界面](#2.2 配置界面)

[2.3 分析结果](#2.3 分析结果)

一、前言

在进行时序分析时,除了slack的分析,还存在pulse width的检查,下面将对pulse width检查进行详细说明。在report timing summary报告中,也会带上Pulse Width检查结果。

二、Report pulse width

2.1 Report pulse width

脉冲宽度检查是对信号波形进行一些规则检查,如检查设计是否满足每个时序单元时钟管脚的最小周期、最大周期、高脉冲时间和低脉冲时间要求,这些规则通常对应电路的功能限制。例如,对DSP时钟引脚的最小周期检查可以保证时钟驱动DSP单元时不会运行在一个高于内部DSP所能承受的频率。

脉冲宽度检查不会影响综合和实现阶段,在vivado中,位流生成之前会执行该分析检查。当发生脉冲宽度违例时,说明有不合理的时钟定义或不合理的时钟结构包括太多的偏斜,此时需要去查看设计器件的数据规格,确认违例处的实际支持范围,可以简化时钟树或将时钟资源布局到更靠近违例引脚的位置。

2.2 配置界面

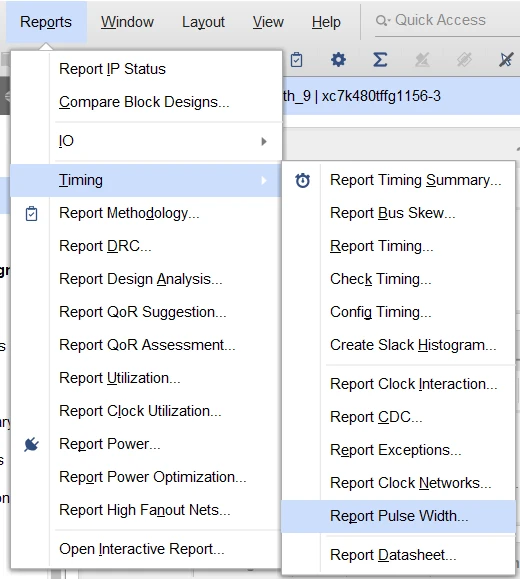

进入"Reports->Timing->Report Pulse Width"

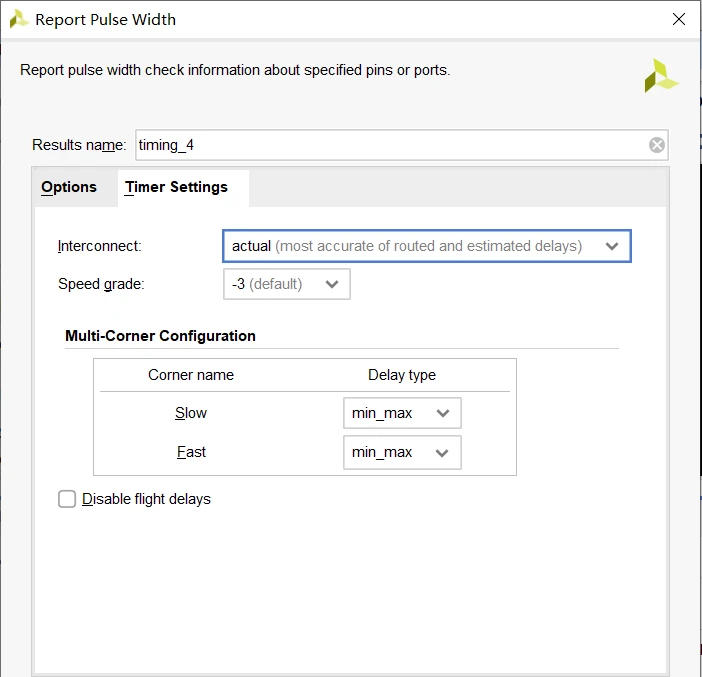

设置报告分析界面,相关配置选项如下

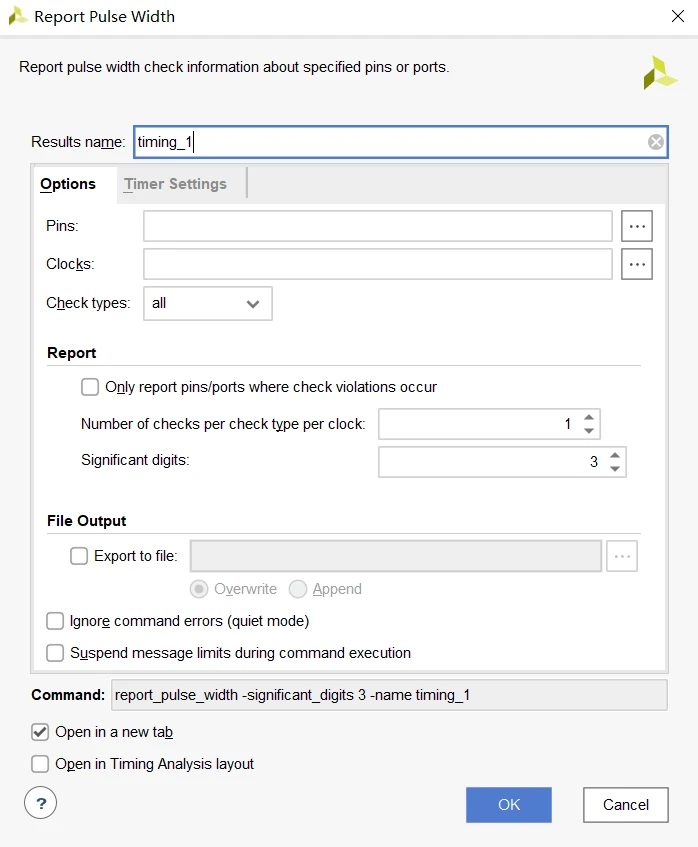

Results name:设置报告窗口名称,默认为timing_x的格式

Pins:可设置指定引脚进行检查,如果选择的非时钟单元引脚,如数据引脚,则报告为空

Clocks:可以通过此选择指定时钟进行检查,不指定时默认对所有时钟经过的时钟引脚进行检查

Check types:设置检查的类型,可选值有min_period,max_period,low_pulse,high_pulse,

max_skew,all,默认为all,即所有类型都检查。

only report pins/ports where check violations occur:勾选后报告只会显示违例的情况

Number of checks per check type per clock:设置对每个时钟检查报告的路径数,默认报告单条最差的路径

Significant digits:设置结果值的精度,默认为3,即小数点后3位

Export to file:勾选后,可以将报告结果以txt格式的文件导出,overwrite勾选表示覆盖原有的报告结果,Append表示不覆盖,进行结果内容的追加

Ignore command errors:执行命令时忽略命令的错误,直接运行,无任何返回信息

Suspend message limits during command execution:勾选后则会忽略信息输出的限制,显示命令执行后所有的信息

Timer Settings窗口设置

interconnect:设置时序分析的连接延时,可选值有actual(实际布局布线后的延时,最精确),estimated(使用评估的延时),none(只考虑逻辑延时)

Speed grade:在时序分析时指定速率等级,但不会改变实际设计中的速率等级

Multi-corner configuration:设置slow corner、fast corner下的延时类型分析,默认时min_max都分析,可以只分析min或max,以及都不分析。

Disable flight delays:勾选后计算I/O延时不会考虑封装延时,flight delay即是在封装引脚到die pad间的延时。

2.3 分析结果

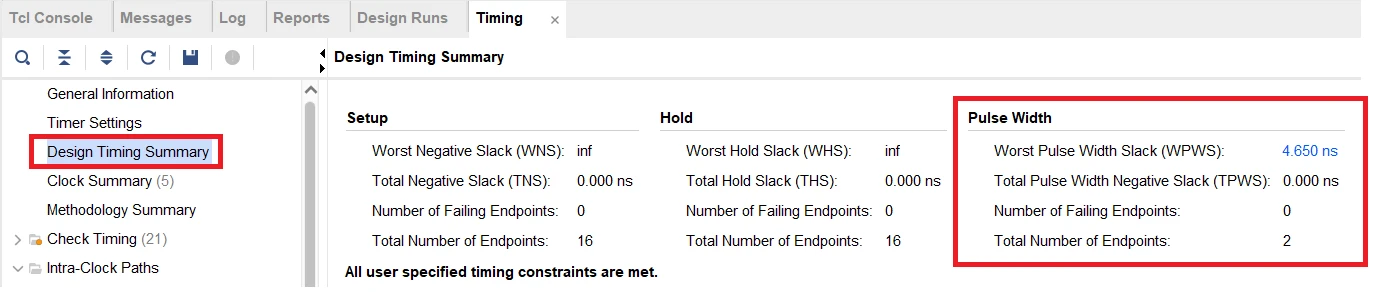

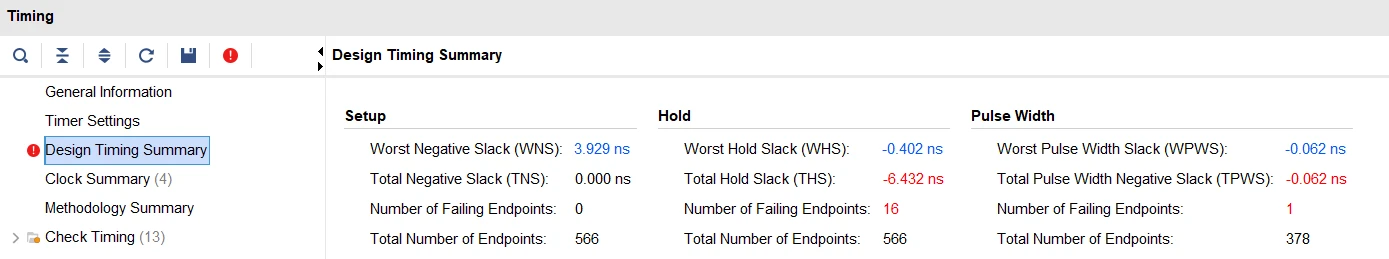

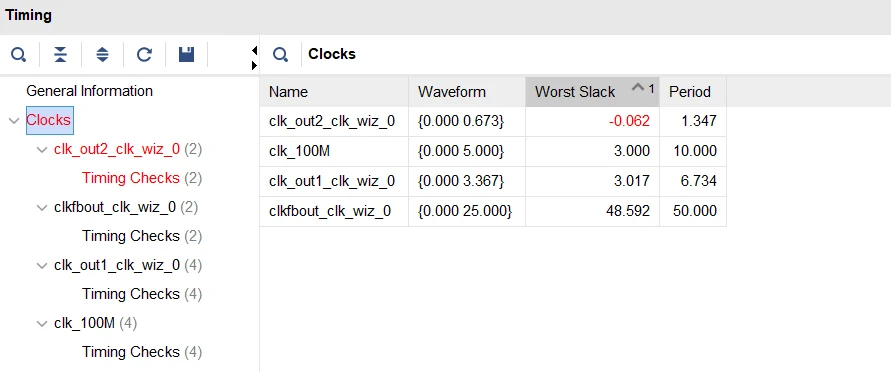

1)在Report Timing Summary的Design Timing Summary会有pulse width的总结报告

worst pulse width slack:报告最差的脉冲宽度slack值

Total Pulse width Negative Slack:所有脉冲宽度违例值之和,如果都不违例,则为0

Number of failing Endpoints:脉冲宽度违例的端点数目,上图为1个

Total Number of Enpoints:总的端点(时钟连接的时序单元)数目,上图为378个

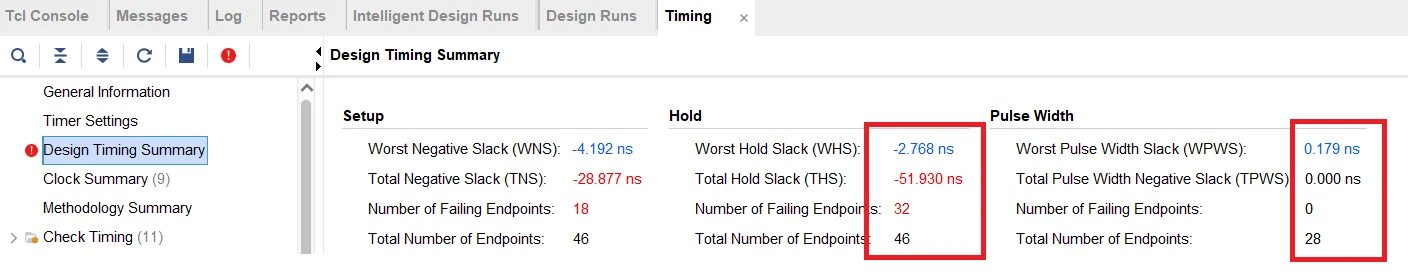

下图示例为没有脉冲宽度违例,可以看出脉冲宽度违例和setup/hold违例是两个独立的概念

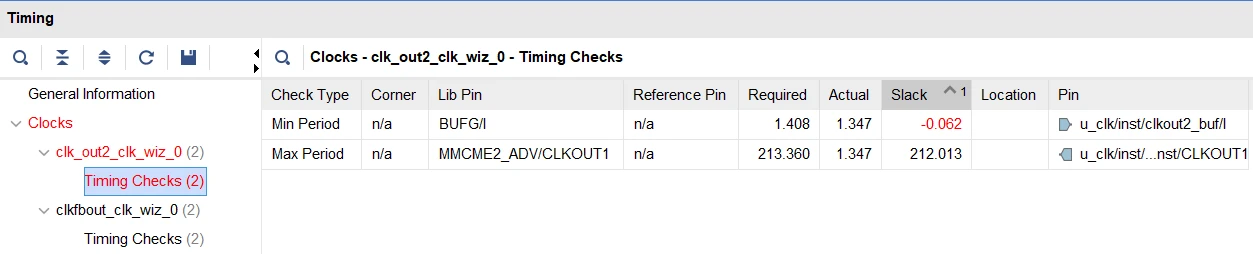

- 在具体时序路径下有关于各时钟驱动所有时序引脚的pulse width报告

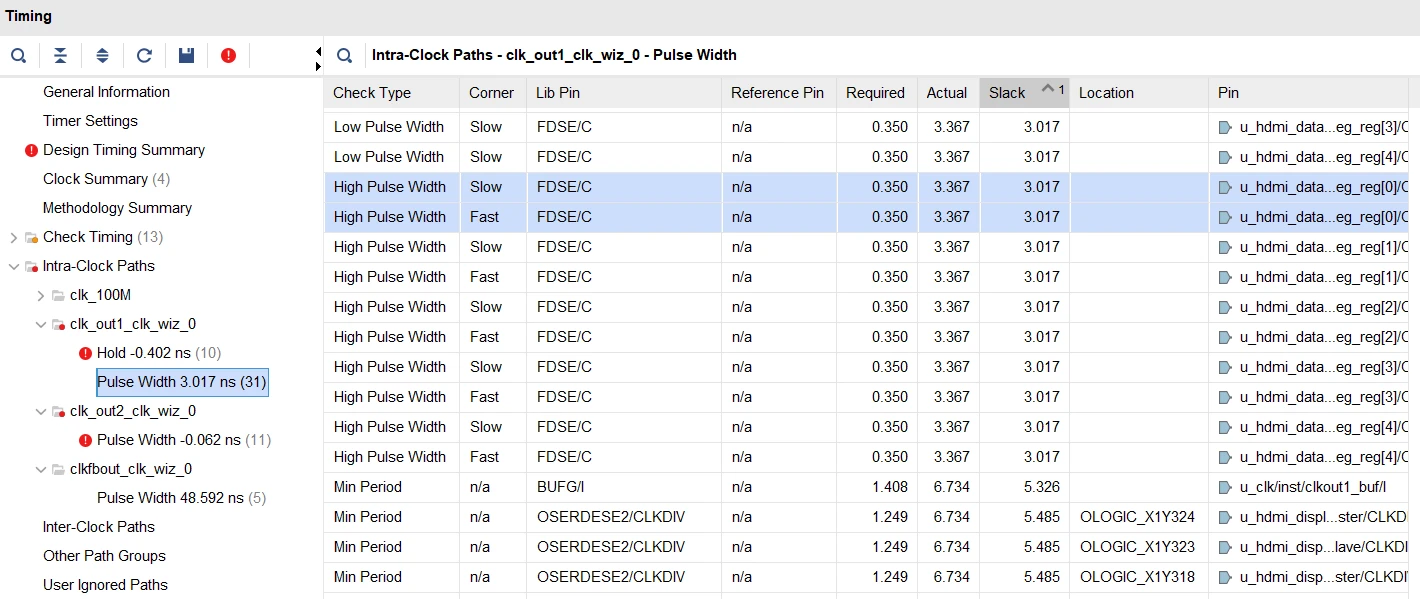

3)也可在Reports->Timing->Report Pulse Width中专门生成脉冲宽度违例的报告,报告按时钟的角度进行分类

详细内容如下,每个时钟检查的类型,min period/max period,corner,lib pin,required时间,和actual时间,以及slack,slack计算方式为:actual-required