LabVIEW RT(Real-Time)和FPGA模块是为开发实时系统和高性能控制应用而设计的,能够有效满足工业控制、自动化测试、信号处理等领域的严格要求。通过这两个模块,开发者可以充分发挥LabVIEW的并行处理能力,实现高效稳定的系统控制。

1. RT模块:实时控制的关键

LabVIEW RT模块允许程序在实时操作系统(RTOS)中运行,这对那些对延迟和时间精度有严格要求的系统尤为重要。RT模块适用于需要高响应速度和稳定性的工业自动化系统、嵌入式控制器和实时数据采集系统。

-

精准的时间控制:在LabVIEW RT中,程序通过定时循环(Timed Loops)来实现严格的时间调度,确保控制程序能在预设的时间内完成任务,减少延迟和抖动。

-

硬件与软件实时结合:LabVIEW RT与NI硬件(如cRIO、PXI等)紧密集成,使得开发者可以直接在硬件上部署控制程序,无需第三方中间件。

-

分离关键任务:使用RT模块时,建议将关键任务与非关键任务分离,确保重要控制任务不会因为其他后台任务的执行而出现延迟。

2. FPGA模块:高性能并行处理

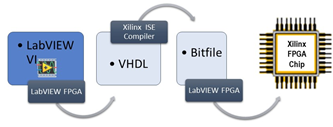

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,LabVIEW FPGA模块使得开发者可以在硬件层级编写程序,适用于那些需要高精度、低延迟的应用,如运动控制、高速数据采集和复杂信号处理。

-

并行处理能力:LabVIEW FPGA利用硬件的并行处理特性,可以在多个任务之间无缝运行。开发者可以在FPGA上部署独立的逻辑单元,各自独立地执行任务,无需等待其他任务完成。

-

高效利用资源:通过优化循环和条件判断,开发者可以精确控制FPGA上的资源使用,确保各个任务的执行效率最大化。

-

基于硬件的控制算法:FPGA适合用于实现基于硬件的闭环控制系统,如PID控制。开发者可以在毫秒级的时间内完成复杂计算,从而提高系统响应速度。

3. 结合使用RT和FPGA模块

在许多应用场景中,LabVIEW RT和FPGA模块常常结合使用,RT模块用于管理系统的整体控制逻辑,而FPGA模块用于处理高精度、高速度的底层任务。两者结合,开发者可以创建出强大的嵌入式控制系统:

-

FPGA处理核心控制任务:在应用中,通常将最重要的高速任务交由FPGA处理,如传感器数据采集、精密运动控制等,而实时任务如数据分析和状态监控由RT模块处理。

-

通信机制优化:LabVIEW提供的DMA(Direct Memory Access)通道可以在FPGA和RT之间进行快速数据传输,确保FPGA的数据能迅速传送到RT模块进行处理。

4. 开发应用

-

模块化设计:无论是使用RT还是FPGA模块,始终保持代码的模块化设计。这样不仅可以使系统更加灵活,还可以降低后期维护和扩展的难度。

-

定期测试与调试:FPGA和RT模块的程序开发过程中,开发者应定期进行测试,确保系统在实际环境中运行稳定。在LabVIEW中使用仿真功能,可以避免硬件调试过程中的不确定性。

5. 应用案例

-

工业自动化控制:通过LabVIEW RT模块,开发者可以设计高精度的工厂自动化控制系统,结合FPGA模块实现高速信号采集与实时反馈控制,确保生产线的高效运作。

-

高速数据采集与处理:在需要高速处理海量数据的场景中,FPGA可以用于实时采集传感器数据,而RT模块则可以在后台处理和分析这些数据,提升系统整体性能。