这里跟大家分享一个我自己写的小软件,实现从AD的原理图里自动找出网络名称和引脚的对应。存成文本方便后续做表格或是使用简单行列编辑生成引脚约束文件(如.XDC .UCF .TCL等)。

我们在FPGA设计中需要引脚锁定文件,就是指示TOP层的端口名称是实际芯片的那个哪个IO脚。这个工作比较繁琐,我们对照原理图每个网络这样搜索,效率很低。由于我基本使用AD设计原理图,知道可以生成protel的网表,我对protel网表格式很熟悉,可以做个软件找出他的引脚对应的网络名称,这样列出一个表格,就得到了原理图中网络名称跟FPGA芯片引脚对应的一个表格。

通过以下方式可以生成protel格式的网络:

即在打开的原理图项目:Design -> Netlist for Project -> Protel .

生成的网表是有小括号和中括号组成的,其中中括号内的是原件属性。小括号是网络名称以及连接的原件引脚。我们就从这个小括号里面找到看是否连接了FPGA的引脚,如果有连接就记录下这个网络和引脚,并输出到文件。

比如我们原理图中U1是要处理的FPGA,程序找到下面的网络就会记录下来。

记录下来生成文本文件:

有了这个文本文件就可以使用行列编辑生成自己需要文件格式。

这里我提供出自己写的这个小工具。如下图:

这里主要看dec_net.c这个文件,代码如下:

cpp

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

static char line[1024];

static char ux[20];

int str_find(char*a,char*b)

{

//find if b in a .

char*p=strstr(a,b);

return p!=NULL ;

}

static char buff[1000][100];

static int idx=0 ;

void prt_len(char*p,int len)

{

int r=len-strlen(p);

printf("%s",p);

while(r--)printf(" ");

}

void print_buff()

{

int i ;

int valid=0 ;

for(i=0;i<idx;++i)if(strstr(buff[i],ux))valid++;

if(valid>=2)return ;

if(valid==0)return ;

if(idx==1)return ;

if(idx!=2)return ;

for(i=0;i<idx;++i)prt_len(buff[i],30);

printf("%s \t",buff[i]) ;

puts(" ");

}

int feed_a_line(char*p)

{

///puts(p);

if(p)

{

strcpy(buff[idx++],p);

return idx ;

}

print_buff();

idx=0 ;

}

int check_a_line(char*p)

{

static int st=0 ;

if(st==0)

{

if(p[0]=='(')st=1 ;

return st ;

}

else if(st==1)

{

if(p[0]==')')

{

st=0 ;

feed_a_line(NULL);

return st ;

}

if(strstr(p,ux))feed_a_line(p);

else if(strstr(p,"-")==NULL)feed_a_line(p);

}

}

int main(int argc,char*argv[])

{

FILE*file ;

static char fn[20];

if(argc<3)

{

printf("uasge :\n\t dec_net file_name Ux\n ");

exit(1);

}

strcpy(fn,argv[1]);

strcpy(ux,argv[2]);

strcat(ux,"-");

file=fopen(fn,"r");

if(file==NULL)

{

printf("无法打开文件.\n");

return 1 ;

}

while(fgets(line,sizeof(line),file)!=NULL)

{

line[strcspn(line,"\n")]='\0' ;

check_a_line(line);

}

fclose(file);

return 0 ;

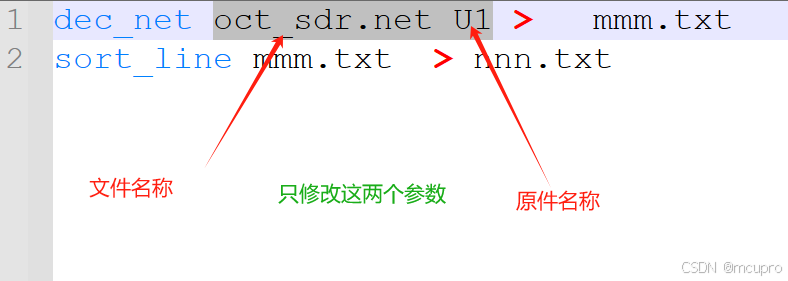

}运行这个需要两个参数 第一个是输入网络文件名,第二个就是要找的原件号。

dec_net oct_sdr.net U1 就是在oct_sdr.net这个文件里面找到U1的网络和引脚对应关系。

另外我还写一个对行进行排序的小工具sort_line,就使用简单冒泡排序,实现代码如下:

cpp

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

static char buff[2000][1024];

static int idx=0 ;

void print_buff()

{

int i ;

for(i=0;i<idx;++i)

printf("%s \n",buff[i]);

}

void bubble_sort(void)

{

static char temp[1000];

int n=idx ;

for(int i=0;i<n-1;i++)

{

for(int j=0;j<n-i-1;j++)

{

if(strcmp(buff[j+0],buff[j+1])>0)

{

strcpy(temp,buff[j]);

strcpy(buff[j],buff[j+1]);

strcpy(buff[j+1],temp);

}

}

}

}

static char line[1024];

int main(int argc,char*argv[])

{

FILE*file ;

if(argc>1)

file=fopen(argv[1],"r");

if(file==NULL)

{

printf("can not read file.\n");

return 1 ;

}

while(fgets(line,sizeof(line),file)!=NULL)

{

line[strcspn(line,"\n")]='\0' ;

// puts( line );

strcpy(buff[idx++],line);

/// feed_a_line (line ) ;

}

fclose(file);

//now all line in buff

printf("find line is %d \r\n",idx);

bubble_sort();

print_buff();

return 0 ;

}这样做出来的列表很整齐。如下图:

具体使用的时候,我们修改run_dec.bat 修改dec_net的两个参数,

运行之后就得到了一个nnn.txt 文件,用文本打开就看到生成的结果。

这里注意里面也可能包含了电源等非IO的网络以及引脚,这里注意手工排除一下。

cpp

通过网盘分享的文件:dec_net.zip

链接: https://pan.baidu.com/s/1zqR6sT5M37d1-pwwdPGERA 提取码: zxgd by 李伟