目录

1.课题概述

本课题采用基于伪码匹配相关峰检测的方式实现基于FPGA的特定序列检测器verilog实现,包含testbench和开发板硬件测试。

2.系统测试效果

仿真测试

当检测到序列的时候,峰值变量opeak会输出一个峰值,然后flag产生一个高电平,表示检测到序列。

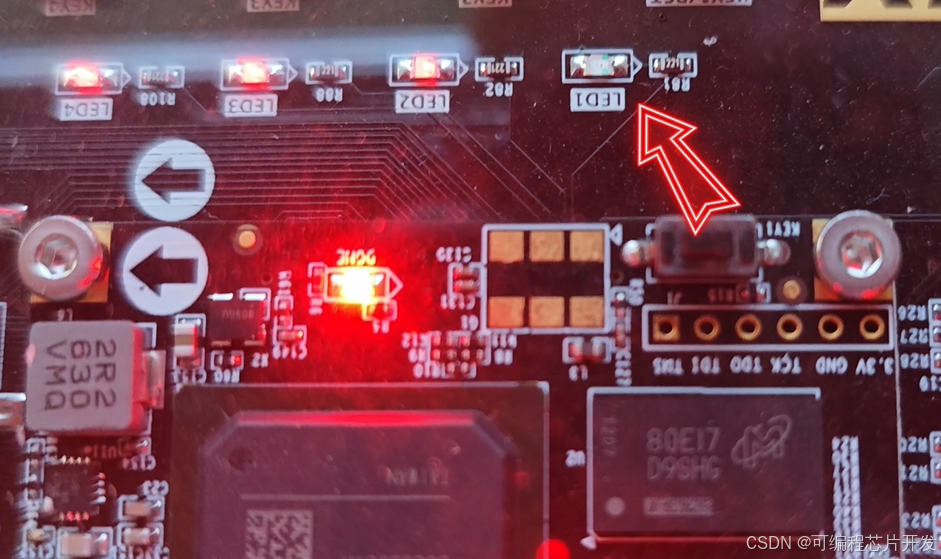

硬件调试

当检测到序列,则LED1灯点亮。

在实际测试过程中,如果你的开发板和我的不一样,可以参考本博客置顶文章进行硬件配置修改:

FPGA系统开发板调试过程不同芯片的移植步骤介绍-CSDN博客

通过这个链接的步骤,可以实现不同开发板上的系统调试。

3.核心程序与模型

版本:vivado2022.2

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/04/04 14:08:45

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops(

input i_clk,

input i_rst,

output signed[1:0]o_seq,

output signed[9:0]o_peak,

output o_search_flag

);

signaler signaleru(

.i_clk (i_clk),

.i_rst (i_rst),

.o_bits (o_seq)

);

parameter SAMP = 1;

//设置需要检测的样本

//parameter meq = 128'b01100111_11010011_01111110_11010100_00011101_11001100_10100111_00000100_11000011_10001011_01001111_01011101_10111010_10011011_10010011_11000011;

parameter meq = {64'b01100111_11010011_01111110_11010100_00011101_11001100_10100111_00000100,64'd0};

parameter lvl = 60;

seq_search #(SAMP,meq,lvl)

seq_search_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_X (o_seq),

.o_peak (o_peak),

.o_search_flag(o_search_flag)

);

endmodule

00X6_001m4.系统原理简介

特定序列检测器旨在从输入的信号流里识别出特定的二进制序列。在采用伪码匹配并依据相关峰来检测序列时,其核心原理为:把输入信号和本地存储的特定伪码序列进行相关运算,当输入信号包含特定序列时,相关运算的结果会呈现出一个明显的峰值,也就是相关峰。通过对这个相关峰进行检测,就能判断输入信号中是否存在特定序列。

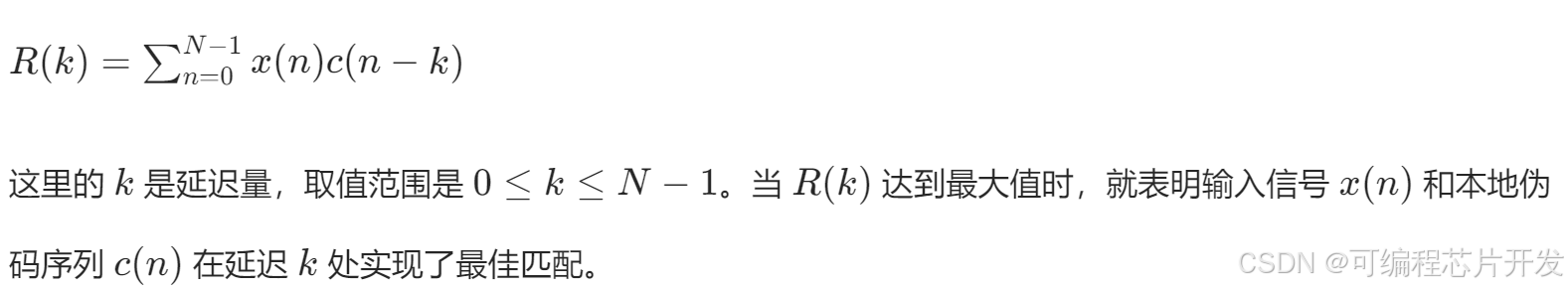

设输入信号序列为 x(n),本地伪码序列为 c(n),其中 n=0,1,⋯,N−1,N 为序列长度。相关运算的公式如下:

然后通过预先设定的一个阈值 T,当相关运算结果 R(k) 大于这个阈值时,就认为检测到了相关峰。阈值的设定需要依据实际情况进行调整,要综合考虑噪声水平、序列特性等因素。

FPGA的实现过程如下:

1.数据输入模块:负责接收输入信号。

2.伪码生成模块:产生本地的特定伪码序列。

3.相关运算模块:对输入信号和本地伪码序列进行相关运算。

4.峰值检测模块:检测相关运算结果中的峰值。

4.1 根据系统的噪声水平和序列特性,确定一个合适的阈值T。

4.2 对每个相关运算结果R(k)进行检查,判断其是否大于阈值T。

4.3 若R(k)>T,则判定检测到相关峰,输出检测信号。

5.输出模块:依据峰值检测结果输出检测信号。

5.完整工程文件

v

v