示例

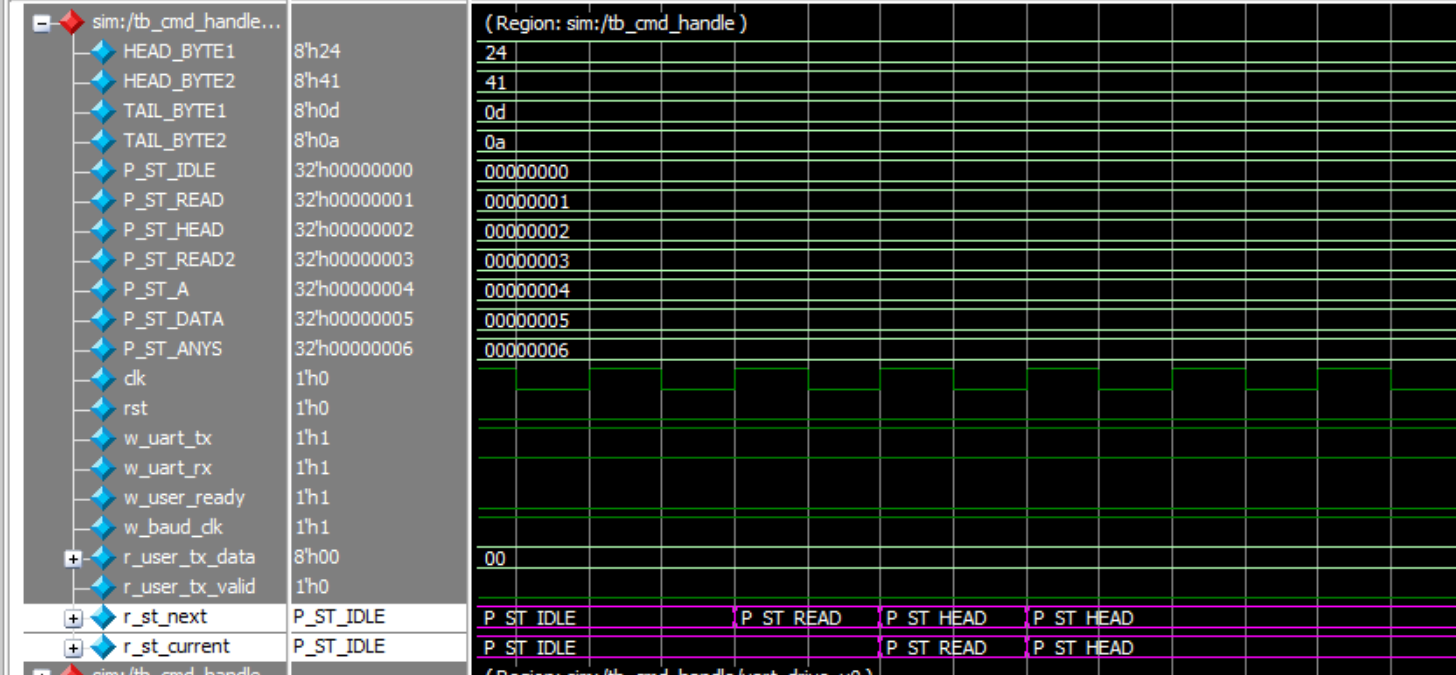

被仿真的文件名为:cmd_handle.v,其中有r_st_current和r_st_next两个状态机变量。

该模块在tb文件中,被例化的名称为cmd_handle_u0

按照如下格式写:cmd_handle_u0.r_st_current

示例tb文件:

c

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/04/10 21:54:40

// Design Name:

// Module Name: tb_cmd_handle

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb_cmd_handle();

cmd_handle #(

.P_SYSTEM_CLK (50_000_000 ), //输入时钟频率

.P_BAUD_RATA (115200 ), //波特率

.P_DATA_WIDTH (8 ), //Uart数据位宽

.P_STOP_WIDTH (1 ), //停止位位宽 1 or 2

.P_CHECK (2 ) //0为奇校验,1为偶校验

)cmd_handle_u0

(

.i_clk (clk ),

.i_rst (rst ),

.i_uart_rx (w_uart_tx),

.o_uart_tx (w_uart_rx),

.o_start_gain (),

.o_gain_speed ()

);

//--------------------------------------------------------------------------

//-- 状态机名称查看器

//--------------------------------------------------------------------------

//1个ASSIC码字符宽度是8位,例如"IDLE"有4个字符则需要32位宽

//80宽度可以容纳10个字符

reg [79:0] r_st_next ;

reg [79:0] r_st_current ;

//这段参数声明是一定要有的,否则在仿真时会报未声明变量的错误,如下图

localparam P_ST_IDLE = 0 ,

P_ST_READ = 1 ,

P_ST_HEAD = 2 ,

P_ST_READ2 = 3 ,

P_ST_A = 4 ,

P_ST_DATA = 5 ,

P_ST_ANYS = 6 ;

always @(*) begin

case(cmd_handle_u0.r_st_current)

P_ST_IDLE : r_st_current = "P_ST_IDLE " ;

P_ST_READ : r_st_current = "P_ST_READ ";

P_ST_HEAD : r_st_current = "P_ST_HEAD ";

P_ST_READ2: r_st_current = "P_ST_READ2";

P_ST_A : r_st_current = "P_ST_A ";

P_ST_DATA : r_st_current = "P_ST_DATA ";

P_ST_ANYS : r_st_current = "P_ST_ANYS ";

default:r_st_current = "P_ST_IDLE ";

endcase

end

always @(*) begin

case(cmd_handle_u0.r_st_next)

P_ST_IDLE : r_st_next = "P_ST_IDLE " ;

P_ST_READ : r_st_next = "P_ST_READ ";

P_ST_HEAD : r_st_next = "P_ST_HEAD ";

P_ST_READ2: r_st_next = "P_ST_READ2";

P_ST_A : r_st_next = "P_ST_A ";

P_ST_DATA : r_st_next = "P_ST_DATA ";

P_ST_ANYS : r_st_next = "P_ST_ANYS ";

default: r_st_next = "P_ST_IDLE ";

endcase

end

endmodule直接运行仿真,就可以: