在之前的专栏《硬件架构的艺术》里,有讲过亚稳态以及多个时钟的处理办法,但是感觉还是太宽泛了些,不太好理解。在这篇博客里,将主要参考《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》这篇论文,系统整理CDC处理方法。

亚稳态

产生原因与影响

产生原因: 寄存器采样不满足建立时间或保持时间要求

- 亚稳态的产生是无法避免的,只能想办法降低其发生的频率。在跨时钟域设计中,如果不采取手段,会有很大概率引入亚稳态。

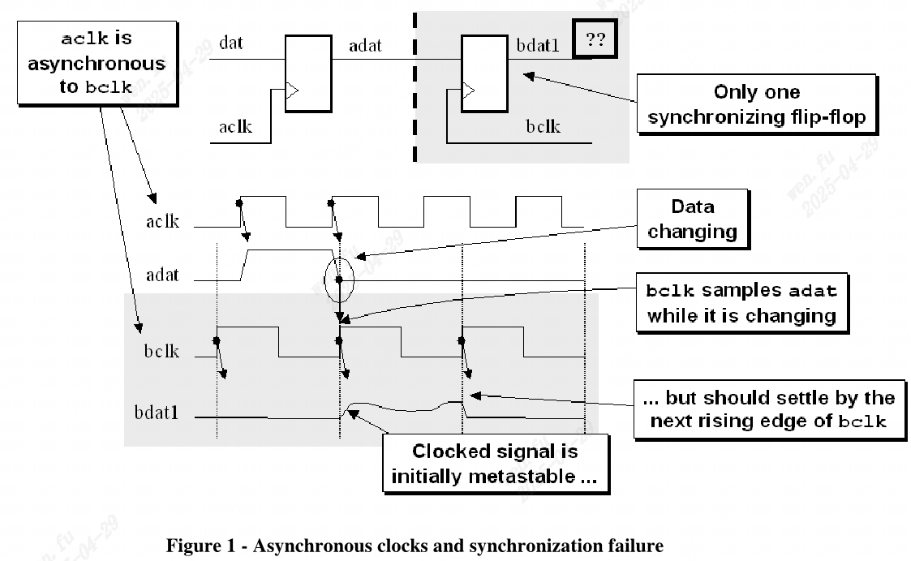

- 下图显示了一个同步失败的示例, 其原因是当一个时钟域中产生的信号在另一个时钟域的时钟信号上升沿附近被采样时,输出进入亚稳态并且没有收敛到合法稳定状态(0或1)。

**亚稳态的影响:**亚稳态最大的危害就是会将系统引入一个未知状态,对于许多设计而言,这无疑是致命的。

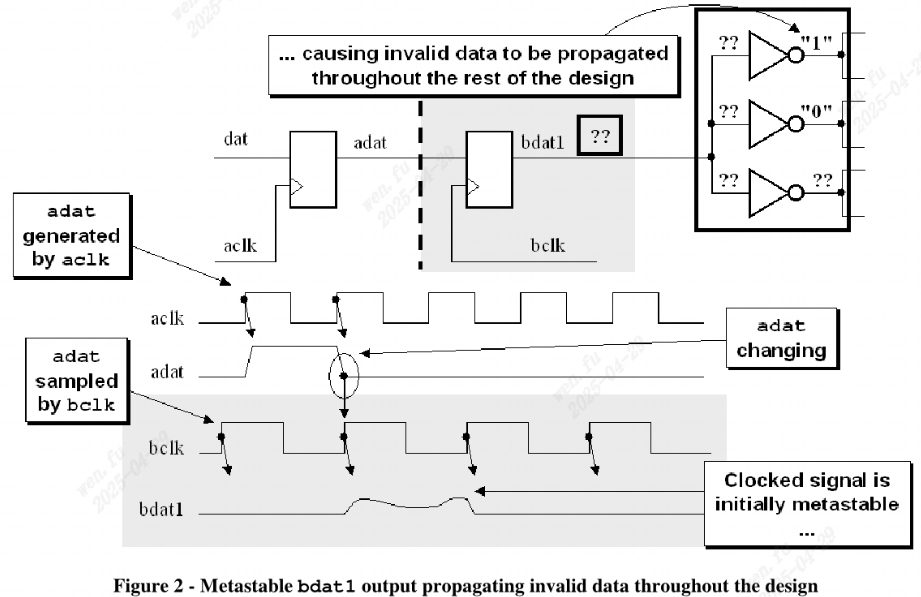

- 如下图所示,接收时钟域中的亚稳态输出会导致非法信号值在整个设计的其余部分传播。由于CDC 信号可能会波动一段时间,因此接收时钟域中其余部分的输入逻辑可能会将波动信号的逻辑电平识别为不同的值,从而将错误信号传播到接收时钟域中。

MTBF:平均无故障工作时间

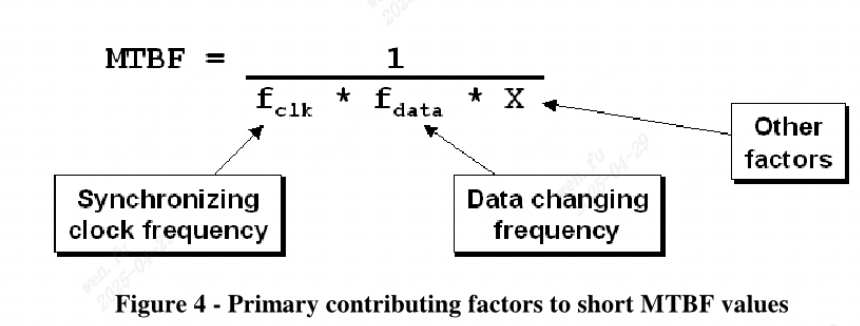

MTBF表征两次故障之间的时间,即多久会发生一次亚稳态。影响同步器电路MTBF 的两个最重要因素是采样时钟频率(信号被采样到接收时钟域的速度)和数据更改频率(跨越CDC 边界的数据更改速度有多快)。

- 从上面的部分方程可以看出,在更高速度的设计中,或采样数据变化更频繁时,故障发生的频率更高(MTBF 更短)。

- 这里的故障是指一个信号被传递到同步触发器,然后在第一级同步触发器上进入亚稳态,并且在一周期后继续处于亚稳态时被采样到第二级同步触发器中。由于该信号在一个时钟周期后没有稳定到已知值,因此当它被采样并传递到接收时钟域时,该信号仍可能处于亚稳态,从而导致相应逻辑出现潜在故障。

- MTBF的值越大越好,表示潜在故障之间的时间间隔较长。若能将MTBF控制在几十年(可以做到),则该设计即可视为几乎不会发生亚稳态的设计,毕竟数字系统预期寿命也没那么长(军工级除外)

两种同步场景

跨CDC 边界传递信号时可能出现两种情况:

- 允许漏采在时钟域之间传递的信号的值:有时不需要对每个值都进行采样,但重要的是采样值必须要准确。 例如,异步FIFO设计中,就可以允许漏采的存在。因为异步FIFO的设计最重要的是正确(或者说不错误)地判断FIFO的空和满。漏采一些数据并不会对其判断空满造成错误,某种意义上还会使其设计更加安全。

- 不允许漏采在时钟域之间传递的信号的值:CDC 信号必须被正确识别或握手后才允许更改。

在这两种情况下,CDC 信号都需要通过某种形式同步到接收时钟域中。

同步器

同步器是一种设备,它采样异步信号,并输出一个与本地或采样时钟同步的信号版本

双触发器同步器

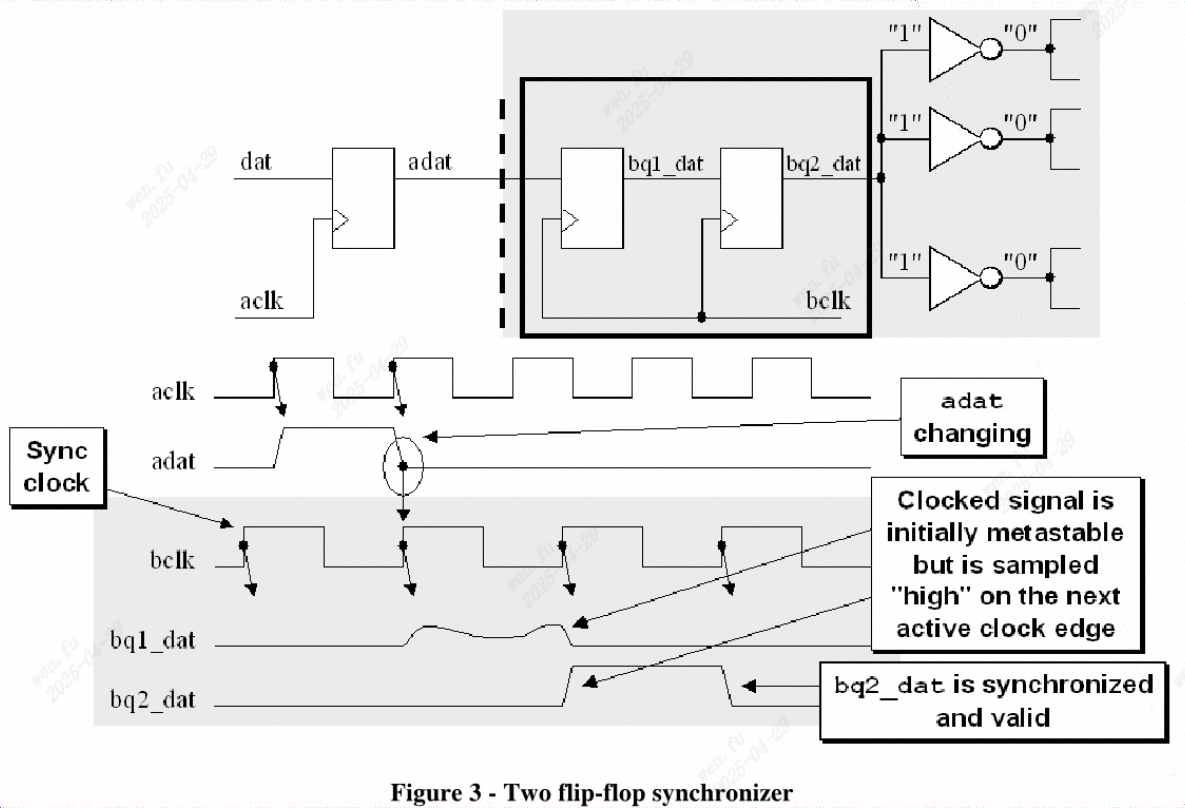

如下图所示,第一个触发器将异步输入信号采样到新的时钟域,并等待一个完整的时钟周期,以允许第一阶段输出信号上的亚稳态衰减,然后用相同的时钟对第二级触发器进行采样,其目的是使第二级触发器输出成为一个稳定且有效的同步信号,并在新时钟域内准备分配。