背景

《ug471_7Series_SelectIO.pdf》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。

第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。

第 2 章《SelectIO Logic Resources》介绍了输入输出数据寄存器及其双倍数据速率(DDR)操作,以及可编程输入延(IDELAY)和可编程输出延迟(ODELAY)。

第 3 章《Advanced SelectIO Logic Resources》介绍了ISERDESE2 、OSERDESE2与IO_FIFO。

了解了这个手册充分介绍的SelectIO架构和资源,以及所支持的电平标准。就可以利用相应的架构和资源实现与不同电平标准、通信速率间的外设建立起联系。

系列目录与传送门

- 基于Xilinx的7系列,

- 笔者学习、研究FPGA的过程、笔记,记录为:《凡人修FPGA传》。

说明1:本系列基于文档文档《ug471_7Series_SelectIO.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,非常支持并推荐大家去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:本博客是笔者用来记录学习过程的一个形式,并非专业论文。因此,在本博客中不会太注重图文格式的规范。

说明5:如果文章有误,欢迎诸位道友指出、讨论,笔者也会积极改正,希望大家一起进步!

文章目录

- 背景

- 系列目录与传送门

- 前言

- [1、ISERDESE2 特性](#1、ISERDESE2 特性)

- [2 ··· ISERDESE2 原语](#2 ··· ISERDESE2 原语)

- [3 ··· ISERDESE2 端口](#3 ··· ISERDESE2 端口)

- [4 ··· ISERDESE2 属性](#4 ··· ISERDESE2 属性)

- [5、ISERDESE2 时钟配置方法](#5、ISERDESE2 时钟配置方法)

-

- [5.1、NETWORKING 接口类型](#5.1、NETWORKING 接口类型)

- [5.2、MEMORY 接口类型](#5.2、MEMORY 接口类型)

- [5.3、MEMORY_QDR 接口类型](#5.3、MEMORY_QDR 接口类型)

- [5.4、OVERSAMPLE 接口类型](#5.4、OVERSAMPLE 接口类型)

- [5.5、MEMORY_DDR3 接口类型](#5.5、MEMORY_DDR3 接口类型)

- [6、ISERDESE2 位宽扩展](#6、ISERDESE2 位宽扩展)

- [7、ISERDESE2 延迟](#7、ISERDESE2 延迟)

- [8、ISERDESE2 从 OSERDESE2 接收的反馈](#8、ISERDESE2 从 OSERDESE2 接收的反馈)

- [9、在 ISERDESE2 中使用 D 和 DDLY](#9、在 ISERDESE2 中使用 D 和 DDLY)

- [10、BITSLIP 子模块](#10、BITSLIP 子模块)

-

- [10.1、Bitslip 操作](#10.1、Bitslip 操作)

- 10.2、BITSLIP子模块使用指南

- [10.3、Bitslip 时序模型和参数](#10.3、Bitslip 时序模型和参数)

- [11、ISERDESE2 模块例化](#11、ISERDESE2 模块例化)

- 12、参考文献

前言

输入串并转换器 (Input serial-to-parallel converters,ISERDESE2)

和 输出并串转换器(output parallel-to-serial converters ,OSERDESE2)

支持极高的 I/O 数据速率,使内部逻辑的运行速度可以到 I/O 速率的1/8。

1、ISERDESE2 特性

- 1、专用解串器/串并转换功能(Dedicated deserializer/serial-to-parallel converter)

ISERDESE2解串器支持高速数据传输,无需 FPGA 内部结构匹配输入数据频率。

支持单数据速率(SDR)和双数据速率(DDR)模式:

SDR 模式:可生成 2 位、3 位、4 位、5 位、6 位、7 位或 8 位宽的并行字(parallel word)。

DDR 模式:单个 ISERDESE2可生成 4 位、6 位或 8 位宽的并行字,两个ISERDESE2 级联,可生成 10 位或 14 位宽的并行字。

- 2、Bitslip子模块(Bitslip submodule)

Bitslip 子模块允许设计人员重新排列进入 FPGA 内部结构的并行数据流的顺序。这可用用于含训练模式的源同步接口校准。

- 3、对 基于选通信号的存储接口 的专用支持(Dedicated support for strobe-based memory interfaces)

ISERDESE2 包含专用电路(包括 OCLK 输入引脚),可以在 ISERDESE2 模块内处理从选通信号(Strobe)到 FPGA 时钟域的转换。

-

4、支持多种接口协议:网络接口、DDR3接口、QDR接口、异步接口。

-

图 3-1 展示了 ISERDESE2 的结构框图,重点标注了主要组件与特性,包括可选反相器。

2 ··· ISERDESE2 原语

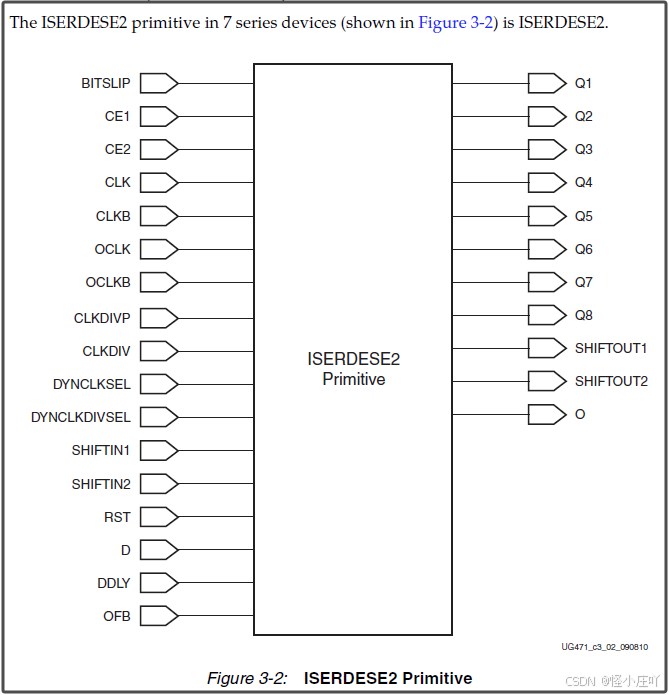

ISERDESE2 原语,如图3-2所示。

3 ··· ISERDESE2 端口

- 1、 Registered Outputs -- Q1 to Q8

Q1 至 Q8 是 ISERDESE2 模块的寄存器输出端口。

单个 ISERDESE2 模块最多支持 8 位解串(1:8 解串比)。

更高位宽(最大到 14 位)仅在双倍数据速率(DDR)模式下支持。

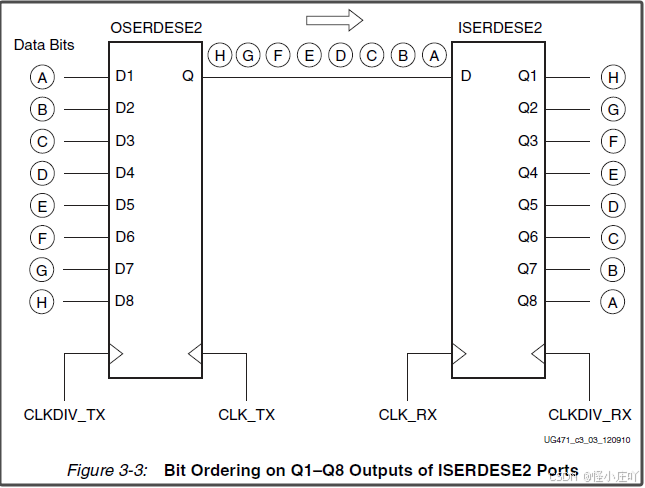

接收的首个数据比特将出现在 Q 输出端的最高位。

如图 3-3 所示,OSERDESE2 的输入比特顺序与 ISERDESE2 的输出顺序互为镜像。例如:

OSERDESE2的输入:字 FEDCBA 的最低有效位(LSB) A 输入至 D1 端口。

ISERDESE2 的输出:同一比特 A 从 Q8 端口输出。

如果,CLK频率为200 MHz:

SDR模式(8-bit):串并转换速率为 200 MHz × 8 = 1.6 Gbps。

DDR模式(8-bit):串并转换速率为 200 MHz × 8 × 2 = 3.2 Gbps

当使用级联位宽扩展时:

发送端 OSERDESE2 的 D1 始终作为最低有效输入位;

接收端 ISERDESE2 的 Q8 始终作为最低有效输出位。

- 2、Combinatorial Output -- O

O 是 ISERDESE2 模块的非寄存型输出端口。

其数据 直接来自数据输入端口D 或者 通过 IDELAYE2 模块的延迟数据输入DDLY。

- 3、Bitslip Operation - BITSLIP

BITSLIP 引脚高电平有效,操作与 CLKDIV 同步。

每次触发 Bitslip 时,Q1 至 Q8 输出端口数据执行桶形移位(Barrel-Shifter)。

DDR 模式下 与 SDR 模式下(单次移位 1 位)的操作不一样。

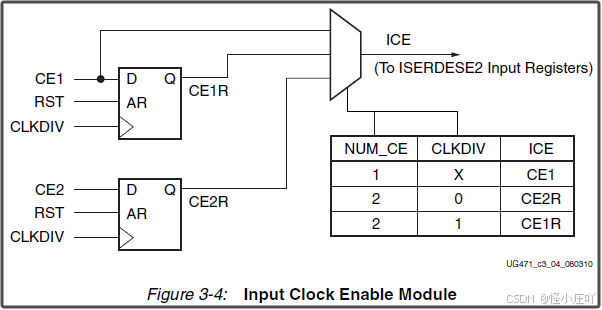

- 4、Clock Enable Inputs - CE1 and CE2

如图3-4所示,每个ISERDESE2模块包含一个输入时钟使能模块。

NUM_CE=1:CE2 禁用,CE1 作为高电平有效时钟使能信号,直接控制 ISERDESE2 输入寄存器。

NUM_CE=2:CE1 与 CE2 协同工作,分别使能 CLKDIV 周期的 前/后 ½ 半段,合成内部时钟使能信号 ICE。

ICE:internal clock enable signal

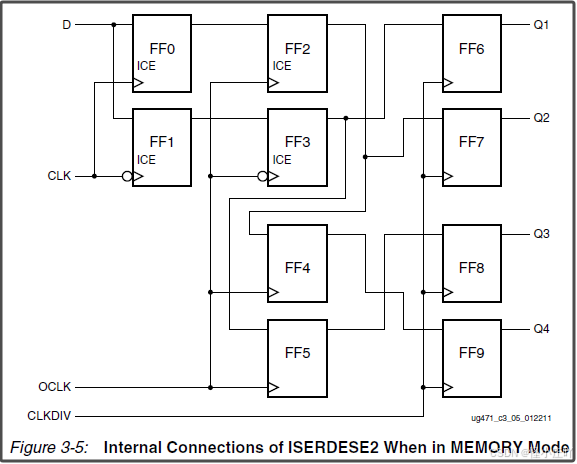

驱动图 3-5 中 FF0~FF3 寄存器的时钟使能端

(图 3-5中的其余寄存器无时钟使能输入)

- 5、High-Speed Clock Input - CLK

用作采样输入串行数据流的高速主时钟输入,与串行数据速率相匹配。

- 6、High-Speed Clock Input - CLKB

用作采样输入串行数据流的高速次时钟输入,

常规模式:连接至 CLK 的反相信号(CLKB = ~CLK)。

MEMORY_QDR 模式:需连接独立相位偏移时钟(如 90° 偏移)。

- 7、 Divided Clock Input - CLKDIV

通常为 CLK 的分频信号(分频比由解串位宽决定),

驱动:serial-to-parallel converter, the Bitslip submodule, and the CE module.

- 8、Serial Input Data from IOB - D

ISERDESE2 的高速串行数据输入端口,

必须与 7 系列 FPGA 的 IOB 资源配合使用。

- 9、Serial Input Data from IDELAYE2 - DDLY

DDLY 是 ISERDESE2 的延迟路径串行数据输入端口,

需与 7 系列 FPGA 的 IDELAYE2 模块协同使用。

数据流路径为:IOB → IDELAYE2 → ISERDESE2.DDLY。

- 10、Serial Input Data from OSERDESE2 - OFB

OFB 是 ISERDESE2 的串行反馈数据输入端口,

专用于与 OSERDESE2 的 OFB 端口互联。

- 11、High-Speed Clock for Strobe-Based Memory Interfaces and Oversampling Mode - OCLK

INTERFACE_TYPE = NETWORKING 时,禁用;

INTERFACE_TYPE = MEMORY_DDR3/QDR 时,

将选通信号(Strobe)域数据同步至 FPGA 自由运行时钟域(OCLK 频率=CLK 频率)。

如图 3-5 所示,通过 IDELAY 调节 CLK 输入延迟,匹配 OCLK 域时序。

- 12、Reset Input - RST

a、高电平有效:

使 CLK/CLKDIV 域异步强制输出低电平。

(除前 4 个触发器可通过属性配置复位值)

b、低电平释放:

同步于 CLKDIV,

内部逻辑在 CLK 首上升沿重新同步复位释放,

输出数据在复位释放后需 2 个 CLKDIV 周期恢复有效。

4 ··· ISERDESE2 属性

- 1、DATA_RATE

DATA_RATE属性用于设定输入数据流的处理模式:

1、SDR(单数据速率):数据在时钟单边沿采样

2、DDR(双数据速率):数据在时钟上升沿与下降沿双沿采样,默认状态。

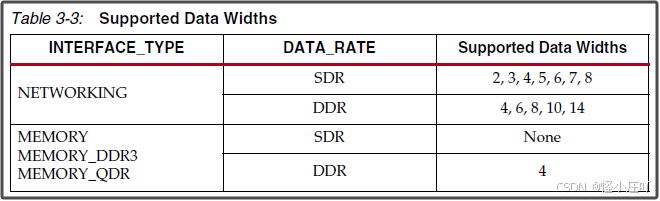

- 2、DATA_WIDTH

DATA_WIDTH 属性定义了串行转并行转换器的并行数据输出宽度。

此属性的可能取值取决于 INTERFACE_TYPE 和 DATA_RATE 属性。

- 3、INTERFACE_TYPE

INTERFACE_TYPE 属性决定了 ISERDESE2 是配置为存储器模式还是网络模式。此属性的允许取值为 MEMORY、MEMORY_DDR3、MEMORY_QDR、OVERSAMPLE 或 NETWORKING。默认模式为 MEMORY。

- 4、NUM_CE

NUM_CE 属性定义了所使用的时钟使能(CE1 和 CE2)的数量。

可能的取值为 1 和 2(默认值为 2)。

- 5、SERDES_MODE

SERDES_MODE 属性定义了在使用位宽扩展时,ISERDESE2 模块是主模块还是从模块。

可能的取值为主模块和从模块,默认值为主模块。

5、ISERDESE2 时钟配置方法

5.1、NETWORKING 接口类型

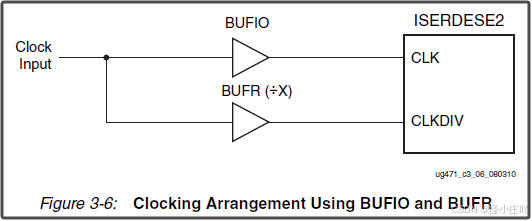

在串并转换过程中,CLK 与 CLLDIV 的相位关系至关重要。

理想情况下,两者应在允许的容差范围内保持相位对齐。

需使 CLK 和 CLKDIV 的相位在名义上(nominally)对齐。

例如,如果设计者在 ISERDESE2 输入端将图 3-6 中的 CLK 和 CLKDIV 反相,

则即使这种时钟配置是允许的 BUFIO/BUFR 配置,时钟仍会处于反相状态。

这也禁止使用 DYNCLKINVSEL 和 DYNCLKDIVINVSEL。

ISERDESE2模块(NETWORKING接口类型)有效时钟配置方案:

1、由 BUFIO 驱动 CLK ,由 BUFR 驱动 CLKDIV 。

2、由 MMCM 或 PLL 驱动 CLK ,由同一 MMCM/PLL 的 CLKOUT[0:6] 输出驱动 CLKDIV 。

当采用 MMCM 驱动 ISERDESE2 的 CLK 与 CLKDIV 时:

向ISERDESE2提供信号的缓冲器类型不能混用。

例如,如果时钟(CLK)由BUFG驱动,那么时钟分频(CLKDIV)也必须由BUFG驱动。

或者,MMCM可以通过BUFIO和BUFR为ISERDESE2提供时钟信号。

5.2、MEMORY 接口类型

ISERDESE2模块(NETWORKING接口类型)有效时钟配置方案:

1、由 BUFIO 驱动CLK,由 BUFIO 驱动OCLK,由 BUFR 驱动CLKDIV。

2、由 MMCM 或 PLL 驱动 CLK 与 OCLK,由同一 MMCM/PLL 的 CLKOUT[0:6] 输出驱动CLKDIV。

3、由 BUFG(全局时钟缓冲器)驱动 CLK 与 OCLK,由另一独立 BUFG 驱动CLKDIV。

OCLK 与 CLKDIV:需名义上(nominally)相位对齐。

CLK 与 OCLK:无需相位关系(允许任意相位偏移)。

5.3、MEMORY_QDR 接口类型

由于 QDR 内存的要求,MEMORY_QDR 模式具有复杂的时钟结构。

仅在使用 MIG 工具时才支持此 INTERFACE_TYPE 属性设置。

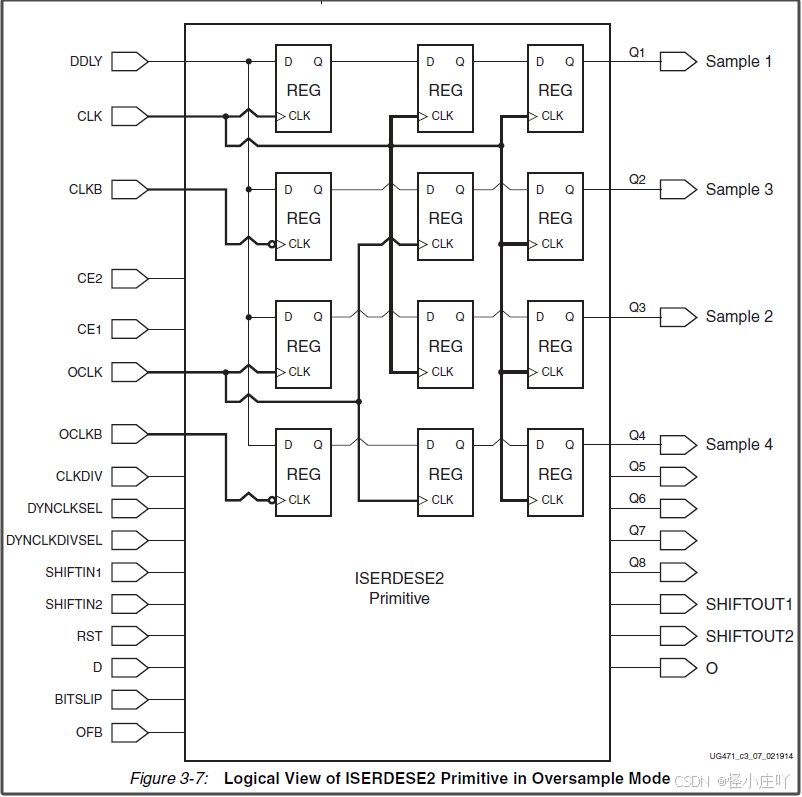

5.4、OVERSAMPLE 接口类型

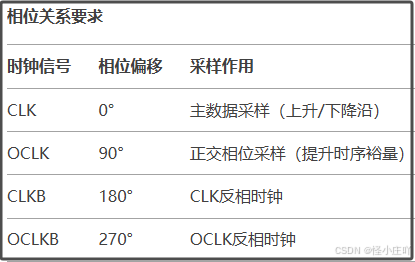

OVERSAMPLE模式用于捕获双相位DDR数据。

如图 3-7 所示,数据如何在 CLK 和 OCLK 的上升沿和下降沿被捕获。

CLK 和 OCLK 之间必须存在 90° 的相位偏移,因为数据在 CLK 和 OCLK 上都被捕获,但会在 CLK 域中被时钟驱动输出。

在此模式下,不使用 CLKDIV。

在此模式下,不使用 CLKDIV。

ISERDESE2模块(OVERSAMPLE接口类型)有效时钟配置方案:

1、由同一BUFIO驱动CLK/CLKB,

由另一相移90°的BUFIO驱动OCLK/OCLKB。

2、由同一BUFG驱动CLK/CLKB,

由另一相移90°的BUFG驱动OCLK/OCLKB。

5.5、MEMORY_DDR3 接口类型

MEMORY_DDR3模式因DDR3存储器的要求而具有复杂时钟架构。

仅在使用 MIG 工具时才支持此 INTERFACE_TYPE 属性设置。

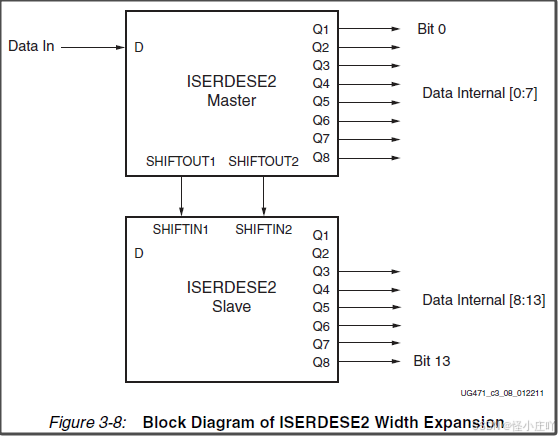

6、ISERDESE2 位宽扩展

两个 ISERDESE2 模块可以用于构建大于 1:8 的串行转并行转换器。

每个I/O单元(I/O tile)中包含两个 ISERDESE2 模块:一个主模块和一个从模块。

通过将主 ISERDESE2 的 SHIFTOUT 引脚连接到从 ISERDESE2 的 SHIFTIN 引脚,

可以将串行转并行转换器扩展到 1:10 和 1:14(仅 DDR 模式)。

图 3-8 展示了一个主从 ISERDESE2 模块级联的 DDR 串并转换的模块图。

在 1:10 SERDES 的情况下,从模块的 Q3、Q4 引脚用于并行接口的最后两位。

对于差分输入,主 ISERDESE2 必须位于差分输入对的正端(_P 引脚)。

当输入不是差分时,与从 ISERDESE2 相关联的输入缓冲器不可用,因此无法使用级联。

- 位宽扩展指南:

-

- 1、两个 ISERDESE2 模块必须是相邻的主从对。

两个 ISERDESE2 模块都必须处于NETWORKING模式,因为MEMORY模式下不支持位宽扩展。

- 1、两个 ISERDESE2 模块必须是相邻的主从对。

-

- 2、将主 ISERDESE2 的 SERDES_MODE 属性设置为 MASTER,

从 ISERDESE2 的 SERDES_MODE 属性设置为 SLAVE。

- 2、将主 ISERDESE2 的 SERDES_MODE 属性设置为 MASTER,

-

- 3、用户必须将从模块的 SHIFTIN 引脚连接到主模块的 SHIFTOUT 引脚。

-

- 4、从模块使用 Q3 到 Q8 引脚作为输出。

-

- 5、DATA_WIDTH 要适用于图 3-8 中的主模块和从模块。

7、ISERDESE2 延迟

1、MEMORY模式

OCLK 级延迟 为 1 个 CLKDIV 周期;

总延迟取决于 CLK 与 OCLK 时钟的相位关系。

2、NETWORKING模式

总延迟 为 2 个 CLKDIV 周期。

NETWORKING模式下比MEMORY模式多出的一个 CLKDIV 周期延迟是由于 Bitslip 子模块的校准操作。

3、MEMORY_QDR 与 MEMORY_DDR3 模式

总延迟为 2 个 CLKDIV 周期。

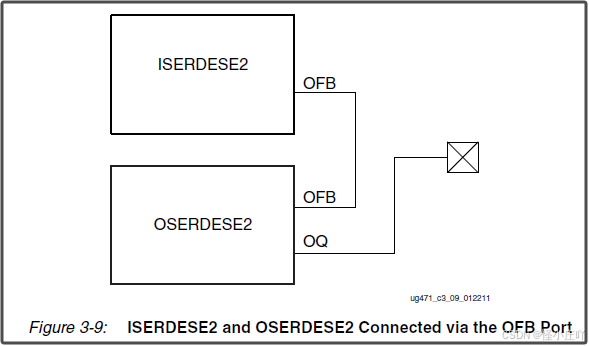

8、ISERDESE2 从 OSERDESE2 接收的反馈

如图3-9所示,ISERDESE2 和 OSERDESE2 中的 OFB 引脚可用于将 OSERDESE2 上发送的数据反馈回 ISERDESE2。

当属性 OFB_USED = TRUE 时,此功能被启用。

当属性 OFB_USED = TRUE 时,此功能被启用。

为了使反馈数据正确,OSERDESE2 和 ISERDESE2 必须具有相同的 DATA_RATE 和 DATA_WIDTH 设置。

当仅使用 ISERDESE2 和 OSERDESE2 的位宽扩展模式时,将主 OSERDESE2 连接到主 ISERDESE2。

将 ISERDESE2 用作反馈端口时,它不能作为外部数据的输入端口。

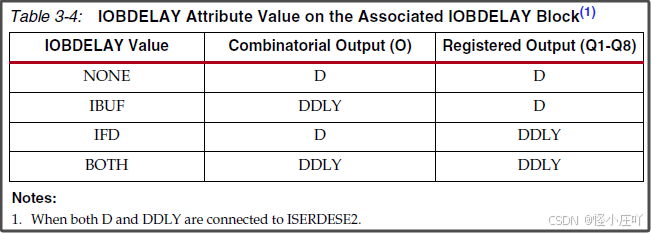

9、在 ISERDESE2 中使用 D 和 DDLY

D 和 DDLY 引脚是 ISERDESE2 的专用输入引脚。

D 输入直接连接到 IOB,而 DDLY 输入直接连接到 IDELAYE2。

这种配置允许用户选择将输入信号的延迟版本或非延迟版本应用于寄存输出(Q1-Q8)或组合输出(O)路径。

IOBDELAY 属性决定了应用于 ISERDESE2 的输入信号选择。

当 D 和 DDLY 均已连接时,表 3-4 显示了 IOBDELAY 不同设置下的结果。

10、BITSLIP 子模块

7 系列器件中的所有 ISERDESE2 模块均包含一个 Bitslip 子模块。

该子模块用于源同步网络类型应用(source-synchronous networking-type applicat)中的字对齐(Word Alignment)。

BITSLIP可对ISERDESE2模块中的并行数据进行重排序,使解串器接收到的所有重复串行模式组合都能呈现给FPGA内部结构。

这种重复串行模式通常被称为训练模式(许多网络和电信标准都支持训练模式)。在某些接口中,这可能是低速转发时钟,可视为重复位模式。

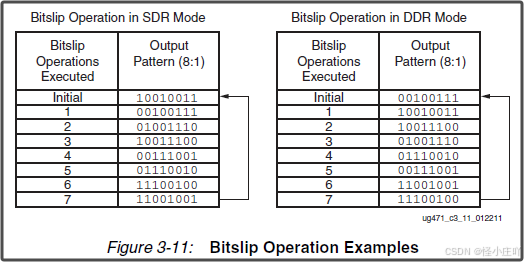

10.1、Bitslip 操作

通过断言 ISERDESE2 模块的 Bitslip 引脚,可在并行端对输入串行数据流进行重排序。重复此操作直至在ISERDESE2输出端观测到所需的训练模式。

图 3-11 中的表格展示了 SDR 和 DDR 模式下 Bitslip 操作的效果。(ISERDESE2 输入的第 8 位是接收到的第一个比特。)

Bitslip 操作与 CLKDIV 同步。

在 SDR 模式下,每次 Bitslip 操作会使输出模式左移一位。

在 DDR 模式下,每次 Bitslip 操作会使输出模式在右移一位和左移三位之间交替。在此示例中,第八次 Bitslip 操作时,输出模式恢复为初始模式。(这假设串行数据是一个八位重复模式。)

尽管重复模式似乎表明 Bitslip 是一个桶形移位操作,但事实并非如此。每次Bitslip操作向输入数据流插入1个新比特,并同时丢弃第n个比特(n为当前并行位宽)。这导致在重复模式上的操作看起来像桶形移位操作。

10.2、BITSLIP子模块使用指南

1、可用模式:仅限 NETWORKING模式下可用,其它模式下不可用。

2、触发条件:BITSLIP 引脚需在 1 个 CLKDIV 周期内保持高电平。

禁止连续触发,且两次 BITSLIP 触发操作之间需至少间隔 1 个 CLKDIV 周期的低电平

3、在 SDR 和 DDR 模式下,从 ISERDESE2 捕获断言的 Bitslip 输入到通过 CLKDIV 将"位滑动"的 ISERDESE2 输出 Q1--Q8 采样到 FPGA 逻辑的总延迟为 2 个 CLKDIV 周期。

4、从应用角度而言,单次BITSLIP指令仅需在一个CLKDIV周期内发出。

5、用户逻辑在分析接收数据模式并决定是否发起下一次BITSLIP操作前,

需在SDR模式下等待至少2个CLKDIV周期,在DDR模式下等待至少3个CLKDIV周期。

6、若对ISERDESE2进行复位操作,BITSLIP逻辑将同步复位至初始状态。

10.3、Bitslip 时序模型和参数

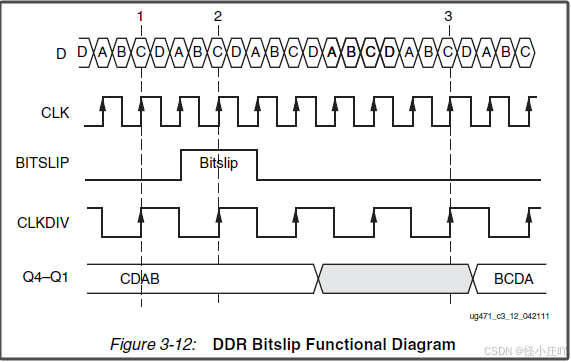

本节以1:4 DDR配置为例说明BITSLIP控制器的时序模型。

假设输入数据(D)为4位重复训练模式ABCD,

该模式在ISERDESE2并行输出端Q1-Q4可能出现四种排列:ABCD、BCDA、CDAB和DABC。

其中仅有某种特定排列对读取Q1-Q4输出的下游逻辑具有实际意义。

通过断言BITSLIP,用户可遍历输入数据所有可能的配置,最终选定所需对齐方式(ABCD)。

图3-12展示了BITSLIP操作的时序特性以及ISERDESE2并行输出Q1-Q4的对应重对齐过程。

11、ISERDESE2 模块例化

// ISERDESE2: Input SERial/DESerializer with bitslip

// 7 Series

// Xilinx HDL Libraries Guide, version 13.4

ISERDESE2 #(

.DATA_RATE("DDR"), // DDR, SDR

.DATA_WIDTH(4), // Parallel data width (2-8,10,14)

.DYN_CLKDIV_INV_EN("FALSE"), // Enable DYNCLKDIVINVSEL inversion (FALSE, TRUE)

.DYN_CLK_INV_EN("FALSE"), // Enable DYNCLKINVSEL inversion (FALSE, TRUE)

// INIT_Q1 - INIT_Q4: Initial value on the Q outputs (0/1)

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.INIT_Q3(1'b0),

.INIT_Q4(1'b0),

.INTERFACE_TYPE("MEMORY"), // MEMORY, MEMORY_DDR3, MEMORY_QDR, NETWORKING, OVERSAMPLE

.IOBDELAY("NONE"), // NONE, BOTH, IBUF, IFD

.NUM_CE(2), // Number of clock enables (1,2)

.OFB_USED("FALSE"), // Select OFB path (FALSE, TRUE)

.SERDES_MODE("MASTER"), // MASTER, SLAVE

// SRVAL_Q1 - SRVAL_Q4: Q output values when SR is used (0/1)

.SRVAL_Q1(1'b0),

.SRVAL_Q2(1'b0),

.SRVAL_Q3(1'b0),

.SRVAL_Q4(1'b0)

)ISERDESE2_inst (

.O(O), // 1-bit output: Combinatorial output

// Q1 - Q8: 1-bit (each) output: Registered data outputs

.Q1(Q1),

.Q2(Q2),

.Q3(Q3),

.Q4(Q4),

.Q5(Q5),

.Q6(Q6),

.Q7(Q7),

.Q8(Q8),

// SHIFTOUT1-SHIFTOUT2: 1-bit (each) output: Data width expansion output ports

.SHIFTOUT1(SHIFTOUT1),

.SHIFTOUT2(SHIFTOUT2),

.BITSLIP(BITSLIP), // 1-bit input: The BITSLIP pin performs a Bitslip operation synchronous to

// CLKDIV when asserted (active High). Subsequently, the data seen on the Q1

// to Q8 output ports will shift, as in a barrel-shifter operation, one

// position every time Bitslip is invoked (DDR operation is different from

// SDR).

// CE1, CE2: 1-bit (each) input: Data register clock enable inputs

.CE1(CE1),

.CE2(CE2),

.CLKDIVP(CLKDIVP), // 1-bit input: TBD

// Clocks: 1-bit (each) input: ISERDESE2 clock input ports

.CLK(CLK), // 1-bit input: High-speed clock

.CLKB(CLKB), // 1-bit input: High-speed secondary clock

.CLKDIV(CLKDIV), // 1-bit input: Divided clock

.OCLK(OCLK), // 1-bit input: High speed output clock used when INTERFACE_TYPE="MEMORY"

// Dynamic Clock Inversions: 1-bit (each) input: Dynamic clock inversion pins to switch clock polarity

.DYNCLKDIVSEL(DYNCLKDIVSEL), // 1-bit input: Dynamic CLKDIV inversion

.DYNCLKSEL(DYNCLKSEL), // 1-bit input: Dynamic CLK/CLKB inversion

// Input Data: 1-bit (each) input: ISERDESE2 data input ports

.D(D), // 1-bit input: Data input

.DDLY(DDLY), // 1-bit input: Serial data from IDELAYE2

.OFB(OFB), // 1-bit input: Data feedback from OSERDESE2

.OCLKB(OCLKB), // 1-bit input: High speed negative edge output clock

.RST(RST), // 1-bit input: Active high asynchronous reset

// SHIFTIN1-SHIFTIN2: 1-bit (each) input: Data width expansion input ports

.SHIFTIN1(SHIFTIN1),

.SHIFTIN2(SHIFTIN2)

);

// End of ISERDESE2_inst instantiation12、参考文献

1、《ug471_7Series_SelectIO.pdf》